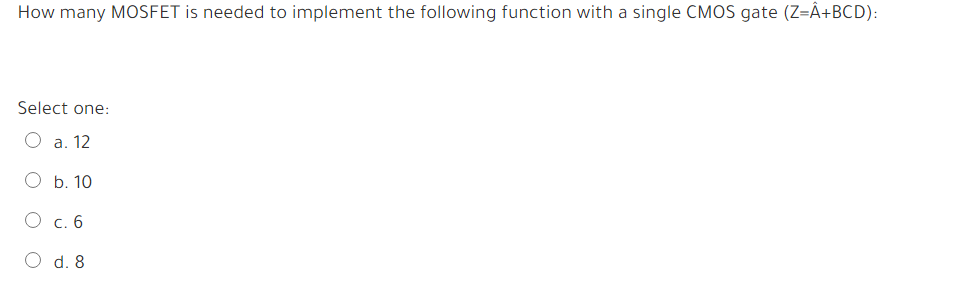

How many MOSFET is needed to implement the following function with a single CMOS gate (Z=Â+BCD):

Q: A certain relay requires 60 mA. Devise a way to use open-collector NAND gates with IOL(max) = 40 mA…

A: Answer: Logic - HI is provided by an external 1Kη PULL- UP RESISTOR, RESISTER is used to control the…

Q: A single-phase, full-wave diode bridge is used to supply power to a resistive load of value R = 75…

A: Given, A single-phase, full-wave diode bridge is used to supply power to a resistive load of value R…

Q: Implement the BCD-to-seven segment decoder circuit using NAND gates only. A CD a 1 1 1 1 1 1 1 1 1 1…

A: The solution to the given problem is below.

Q: Write a 8051 assembly and C program to generate a square wave with a delay of 5 ms on pin P2.1.…

A: Assembly language: Assembly language is a low level programming language. It is used to directly…

Q: Show that the overall the noise figure of a system comprising three 2-port networks connected in…

A: If the blcok are impedance matched properly, the gain G G=G1 G2for each…

Q: Write the Dynamic gates using a clocked pMOS pull-up network.

A: Dynamic gates using a clocked pMOS pull-up network.

Q: If we wish to have an ouput that switches ac, we would need to specify O TTL output. solid state…

A: The complete answer is given below

Q: How can we reduce the transition time of a Bistable Multivibrator?

A: A Bistable Multivibrator has two stable states. The circuit stays in any one of the two stable…

Q: Implement the given SOP using NAND Gate AB + B'CD+ A'C

A: Given boolean SOP expression: AB + B'CD+ A'C Apply Demorgan's theorem by taking the double…

Q: Determine the worst case delay of CMOS circuit with the expression F=((A.C)+B).(A’.C’) driving 8…

A: Given: Determine the worst case delay of CMOS circuit with the expression F=((A.C)+B).(A’.C’)…

Q: For the below circuit, find Req across the source in KQ. 3 kng 5 kng 4 kfl 3 mA 10 kΩ 7 kn3 Select…

A: Correct answer - option (b)

Q: Given a 2 input-4 column 3-output programmable logic array (PLA) device as shown in Figure Q2(e).…

A: solution :

Q: Build a 4-bit adder with inputs a (input [3:0] a;) and inputs b (input [3:0]b;) with outputs c…

A: Given that Build a 4-bit adder with inputs a (input [3:0] a;) and inputs b (input [3:0]b;) with…

Q: According to the data-sheet of M74HC00 IC, ICC=50mA,tpLH=7ns, tpHL=15ns, VOH=5.9v, VOL=0.1,…

A:

Q: How many valid states for a modulus-N counter? Select one: ON O N-1 O 2N O N? What is the initial…

A: Here in this multiple question we have asked no of valid state in modulus N counter ..and second…

Q: Q2: A medium scale Digital Circuit needs to be implemented on an ASIC. Study and list out any two…

A: The two points highlight the parameters and performance indicators as given in the question as per…

Q: In the intérfacing diagram of DAC with 8051 microcontrollers, connect a switch SW to pin P0.0. Write…

A: Staircase waveform:- ANSWER:-

Q: 2. Which of the following is true for a pnp transistor in active region? a. CB junction is reversed…

A: The types of transistors are as follows:- 1. pnp 2. npn

Q: In the comparison of certain logic devices, it is noted that the power dissipation for one…

A: Ans"- CMOS device

Q: 2- According to the FPGA's cells studied, how many FPGA cells are required to implement an 8 bit…

A: Given: According to the FPGA's cells studied, how many FPGA cells are required to implement an 8-…

Q: In CMOS circuit when the pullup part is "off" and the pulldown is "off" then the logic output is:…

A: We have a CMOS circuit. The full form of CMOS is "complementary metal-oxide-semiconductor". CMOS is…

Q: The minimum number of transistors required to implement a two input AND gate is

A: the minimum number of transistors required to implement a two input AND gate is

Q: Convert the following CFG to a PDA.

A:

Q: The following switching functions are to be implemented using a decoder. The minimum configuration…

A: The Answer is in below Steps

Q: Circuits implemented using FPGA compared to the same circuits implemented using ASIC are difficult…

A: The correct Answer for the above question is "True" Explanation: ASIC stands for…

Q: diagram and a brief explanation, explain how a transistor works. What is the main difference between…

A: Transistor is a semiconductor device. It has both majority and minority currents Transistors mainly…

Q: Consider a 2 input NOR gate as shown below: VDD B OUT Which of the following represents the worst…

A: Answer: The inclusive NOR (Not-OR) gate has a logic level "1" output that only goes "LOW" to logic…

Q: Write a ALP to implement an NAND gate and store the result in the memory location 6000H.

A: NAND as Universal Gate – NAND is a universal gate. All other logic gates can be constructed by the…

Q: Using the connection abbreviations, redraw the circuit in Figure 8.9c to show how it can be…

A: Given Data

Q: 3- How many 74LS00 NAND gate inputs can be driven by a 74LS00 NAND gate outputs' Refer to data sheet…

A:

Q: 2- write a ALP to implement an NOR gate and store the result in the memory location 8000H?

A: ALP to implement an NOR gate and store the result in the memory location 8000H is given below:-

Q: Calculate the logic swing, transition width, and the midpoint voltage for an depletion loaded - NMOS…

A: Solution ::

Q: If R = 202, L = 0.6H what value of C will make an RLC series circuit: %3D (a) overdamped, (b)…

A: overdamped, \alpha > \omega_0α>ω0alpha, leads to the sum of two decaying exponentials…

Q: Consider the circuit given below: MSB MSB Decimal Input BCD Gray code 2" x1 encoder converter You…

A: introduction :

Q: The rows and columns of the interconnection matrix in an SPLD are connected using(a) fuses (b)…

A: SPLD: Typically, the logic block includes a few macrocells that are able to perform multiple inputs…

Q: The circuit below has a 2-to-4 decoder with active high outputs connected to a 4-to-1 MUX. Derive an…

A: Decoder:A binary code of n bits is capable of representing up to 2^n distinct elements of coded…

Q: We can design ripple counter that counts from 0 – 10 by inserting (A3, A1) to NAND gate and connect…

A: Explanation: The NAND-Gate is indeed a logic-gate which operates in the opposite direction of an…

Q: Find the Boolean function implemented by the CMOS gate circuit whose bar diagram is given below.

A: The correct answer is option A) Reason: The three trans are in parallel (A, B, C) and the trans D…

Q: 2. Realize the following function using only fundamental CMOS gates and CMOS transmission gates.…

A: Realize the following function using only fundamental CMOS gates and CMOS transmission gates.…

Q: The base - emitter junction is normally active region. biased, when the bipolar junction transistor…

A: Answer: Forward

Q: DISCUSSION: 1. Explain why a series RL circuit with high inductance has a slow response?

A: As it was not stated which question to be answered, I'm answering the question of the discussion…

Q: To build CMOS circuit we need 2 rules Select one or more: O a. only use NFETS in pullup circuits b.…

A: answers: option b and d are correct This is a method used to develop integrated circuits also CMOS…

Q: Show step-by-step mathematical calculations for XOR gate implementation using multilayer perceptron.

A: Please upvote. I am providing you the correct answer below. Please please please.

Q: 03: choice the correct answer 1. In a transistor lightly doped part is a. Emitter b. Collector C.…

A: Transistor: The arrangement of semiconductors such that a thin semiconductors is placed in between…

Q: Write complete VHDL modules for the following digital circuits: (a) A Difference Borrow (b) S1 S2 A…

A: It is defined as Very High-Speed Integration Circuit HDL (Hardware Description Language). VHDL…

Q: What is the advantage of a carry lookahead adder over a ripple adder (explain your answer)? and what…

A: The fi. This is the expansion strategy that disposes of the issue due to interstate convey delay.…

Q: What is the logic gate for the following CMOS gates? V DD V DD P1 A P3 P2 B Y N2 N3 GND GND ) AND…

A: Given The answer is given below.

Q: When the frequency of the input signal to a CMOS gate is increased, the average power dissipation(a)…

A: Given: When the frequency of the input signal to a CMOS gate is increased, the average power…

Q: n CMOS circuit when the pullup part is "on" and the pulldown is "on" then the logic output is

A: Correct answer: D

Step by step

Solved in 2 steps

- A medium scale Digital Circuit needs to be implemented on an ASIC. Study and list out any two points highlighting the parameters and performance indicators when the selection of the ASIC goes in favor for a CPLD instead of an FPGA.Determine the worst case delay of CMOS circuit with the expression F=((A.C)+B).(A’.C’) driving 8 identical 2-input NAND Gates.The circuit of Exp #8.2, configured as a subtractor, can be used to compare two 4-bit numbers. Subtractor outputs Cout and (S3.so) can be combined logically to indicate the relationship between inputs A and B. The gate circuit needed to do this appears as the interface block in the following diagram. Subtractor 220 ohm Cout A - B LEDO 4 A S3 A < B LED1 220 ohm Interface Block S2 (Your Design) 220 ohm B S1 A > B LED2 So (A - B) AirSupplyLab.com Figure 8.2: 4-bit Comparator Design the contents of this interface. You will build the circuit using only 2 chips: 1. a 7402 NOR chip 2. either a 7432 OR chip or a 7408 AND chip. Design the interface two ways: (a) an OR and NOR circuit, and (b), a NOR and AND circuit. Include both designs in your lab notebook and build and test one of them. Each design consists of 3 parts – one for each output – and requires 5 gates total. ExpressSCH has custom DM symbols for all gates (including ANDS and ORs). Use them, but only where they make circuit…

- Write a ALP to implement an NAND gate and store the result in the memory location 6000H.Using a diagram and a brief explanation, explain how a transistor works. What is the main difference between an NPN and PNP configuration?Design and implement a minimal 5 up counter. It counts from 0 to 4 and repeats. Design the circuit such that, if the counter enters into the unwanted states: 5,6 and 7, it should jump into state 0 on the next clock pulse.

- (b) For the following Fixed Biased Junction Field Effect Transistor, determine & 16v (i) Vaso (i) Ing (iii) Vpsq 2k D Ipss =10mA Vp=-8VBuild and simulate in multisim using gates, then using chips F2 = A(B’ + C’ + D’) + BCDShow step-by-step mathematical calculations for XOR gate implementation using multilayer perceptron.

- How does a Phase-Locked Loop (PLL) operate within a microchip's clock generation circuitry?Write a function to generate an output voltage of 0.5V on the CCP2 pin. Consider a resolution of 12 bits, a fosc of 16MHz, Vcc of 3.3V and a Vss of 0V. It is necessary to include the proper pin configuration.In the context of an ALU, how does the carry-lookahead adder improve addition speed compared to a ripple-carry adder?