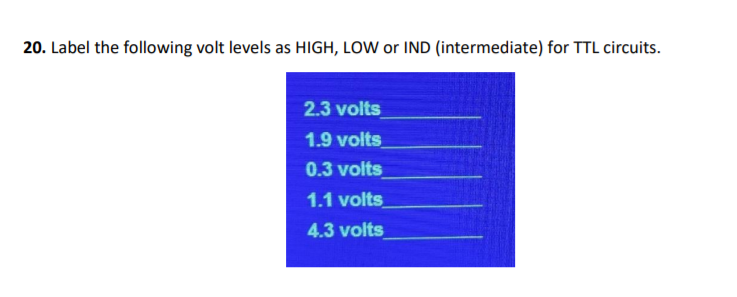

20. Label the following volt levels as HIGH, LOW or IND (intermediate) for TTL circuits. 2.3 volts 1.9 volts 0.3 volts 1.1 volts 4.3 volts

20. Label the following volt levels as HIGH, LOW or IND (intermediate) for TTL circuits. 2.3 volts 1.9 volts 0.3 volts 1.1 volts 4.3 volts

Chapter25: Television, Telephone, And Low-voltage Signal Systems

Section25.1: Television Circuit

Problem 15R

Related questions

Question

Transcribed Image Text:20. Label the following volt levels as HIGH, LOW or IND (intermediate) for TTL circuits.

2.3 volts

1.9 volts

0.3 volts

1.1 volts

4.3 volts

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by step

Solved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, electrical-engineering and related others by exploring similar questions and additional content below.Recommended textbooks for you

EBK ELECTRICAL WIRING RESIDENTIAL

Electrical Engineering

ISBN:

9781337516549

Author:

Simmons

Publisher:

CENGAGE LEARNING - CONSIGNMENT

EBK ELECTRICAL WIRING RESIDENTIAL

Electrical Engineering

ISBN:

9781337516549

Author:

Simmons

Publisher:

CENGAGE LEARNING - CONSIGNMENT