4. Given a multiplexer: Assume i3 = 0, i2 = 1, il = 1, and iO = 0. a) If s1 = 0 and s0 = 0, then y = ? b) If s1 = 1 and sO = 0, then y = ? c) sls0 = ? allows iO to pass through to y. d) s1s0 = ? allows i3 to pass through to y.

4. Given a multiplexer: Assume i3 = 0, i2 = 1, il = 1, and iO = 0. a) If s1 = 0 and s0 = 0, then y = ? b) If s1 = 1 and sO = 0, then y = ? c) sls0 = ? allows iO to pass through to y. d) s1s0 = ? allows i3 to pass through to y.

C++ for Engineers and Scientists

4th Edition

ISBN:9781133187844

Author:Bronson, Gary J.

Publisher:Bronson, Gary J.

Chapter4: Selection Structures

Section4.3: Nested If Statements

Problem 8E

Related questions

Question

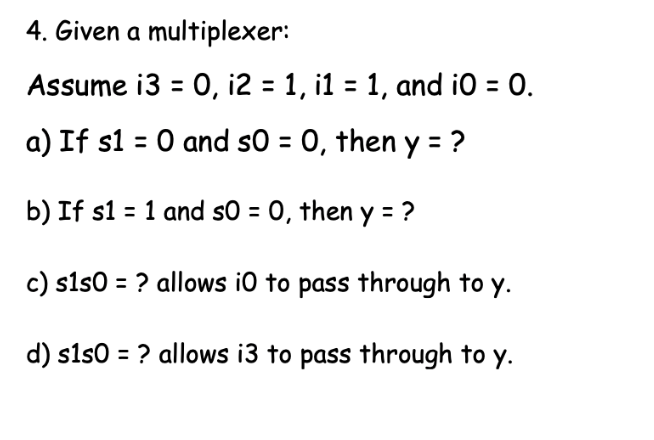

Transcribed Image Text:4. Given a multiplexer:

Assume i3 = 0, i2 = 1, i1 = 1, and i0 = 0.

a) If s1 = 0 and s0 = 0, then y = ?

b) If s1 = 1 and so = 0, then y = ?

c) s1s0 = ? allows i0 to pass through to y.

d) sls0 = ? allows i3 to pass through to y.

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

C++ for Engineers and Scientists

Computer Science

ISBN:

9781133187844

Author:

Bronson, Gary J.

Publisher:

Course Technology Ptr

C++ for Engineers and Scientists

Computer Science

ISBN:

9781133187844

Author:

Bronson, Gary J.

Publisher:

Course Technology Ptr