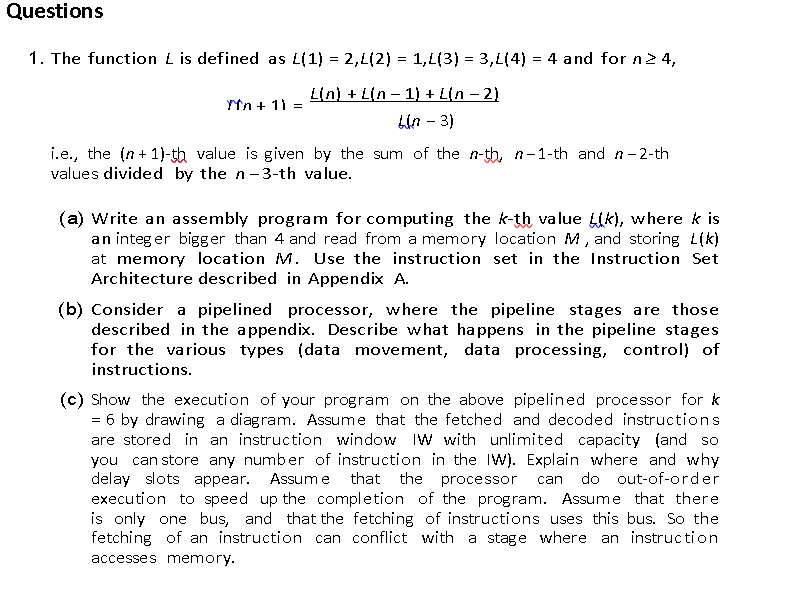

A & B answers are given below please Answer C part Algorithm – We are taking first element of array in A Comparing A with other elements of array, if A is smaller then store that element in A otherwise compare with next element The value of A is the answer A Solution

A & B answers are given below please Answer C part

- We are taking first element of array in A

- Comparing A with other elements of array, if A is smaller then store that element in A otherwise compare with next element

- The value of A is the answer

A Solution

|

2000 |

LXI H 2050 |

H←20, L←50 |

|

2003 |

MOV C, M |

C←M |

|

2004 |

DCR C |

C←C-01 |

|

2005 |

INX H |

HL←HL+0001 |

|

2006 |

MOV A, M |

A←M |

|

2007 |

INX H |

HL←HL+0001 |

|

2008 |

CMP M |

A-M |

|

2009 |

JNC 200D |

If Carry Flag=0, goto 200D |

|

200C |

MOV A, M |

A←M |

|

200D |

DCR C |

C←C-1 |

|

200E |

JNZ 2007 |

If Zero Flag=0, goto 2007 |

|

2011 |

STA 3050 |

A→3050 |

|

2014 |

HLT |

Part (b)

Pipeline-

The pipeline is the implementation technique where multiple instructions are executed simultaneously. It is highly efficient and improves overall performance.

In a pipelined processor, the pipeline has two ends the input end and the output end. Between both ends, there are many stages, where one stage is connected to another stage. The common clock controls all the stages in the pipeline along with the interface register.

The five stages of the pipeline are

- IF(instruction fetch)

- ID(instruction decode)

- RR(register read)

- EX(execute instruction)

- WB(Write back result into the register)

The processor has 5 stages of the pipeline.

Stage 1

IF(instruction fetch)

It fetches the instruction to be executed from the address available in the memory whose value is present in the program counter. The program counter(PC) keeps track of instructions that are being fetched. At every clock cycle from the instruction memory, the instructions are fetched.

Stage 2

ID(instruction decode)

It decoded the instruction and execute it. The 16-bit instructions will be divided into several parts.

Stage 3

RR(register read)

In this stage, it calculates the address of read register and that address sends to the register. Data from the register is read and send to the next unit.

Stage 4

EX(execute instruction)

It executes the instructions.ALU operations are performed in this stage.

Stage 5

WB(Write back result into the register)

After executing the instruction the result is written into the register. It is used to write any data from the instruction or storing the result of the ALU to the register.

A Instruction Set Architecture

A.1 Instruction set

We present a list of instructions typical of a RISC (reduced instruction set computer) machine. In data-movement and control instructions, the addresses may be immediate #X, direct (memory) M, indirect (memory) [M], register r, or register indirect [r] addresses. Data-processing instructions use immediate or register addressing. PC is the programme counter and a <- b indicates that the value of b is placed in a.

LOAD a, b a <- b

STOR a, b a <- b

ADD a, b, c a <- b + c

ASH a, b, c a <- (b >>[s] c)

LSH a, b, c a <- (b >>[u] c) BR a PC <- a

|

SUB |

a, |

b, |

c |

a |

<- |

b |

- c |

BEQ |

a, |

b, |

c |

PC |

<- |

a |

if |

b = |

c |

|

MUL |

a, |

b, |

c |

a |

<- |

b |

* c |

BNE |

a, |

b, |

c |

PC |

<- |

a |

if |

not |

b = c |

|

DIV |

a, |

b, |

c |

a |

<- |

b |

/ c |

BLT |

a, |

b, |

c |

PC |

<- |

a |

if |

b < |

c |

|

AND |

a, |

b, |

c |

a |

<- |

b |

& c |

BGT |

a, |

b, |

c |

PC |

<- |

a |

if |

b > |

c |

OR a, b, c a <- b | c

NOT a, b a <- !b

BLE a, b, c PC <- a if b <= c BGE a, b, c PC <- a if b >= c

Note: Here b >>[s] c denotes the arithmetical shift of b to the right by c positions, and

b >>[u] c denotes the logical shift of b to the right by c positions.

A.2 The pipeline

We will use a five-stage pipeline:

- IF (instruction fetch),

- ID (instruction decode),

- RR (register read),

- EX (execute instruction),

- WB (write back result into register).

- Note that for some instructions (e.g., LOAD r, #X) some of the pipeline stages (e.g., RR) are not

A.3 Execution rules

The rules for the execution of instructions are as follows:

- All instructions go through the IF and ID stages

- For data-movement instructions the data transfer between the CPU and main mem- ory happens in the execute stage. (This means that if a data transfer operation is executing, no data can be transferred across the main-memory )

- Immediate addressing for input arguments does not require RR or EX (e.g., LOAD r1, #X).

- Arithmetic and logic instructions need RR, EX and

- Branching operations require RR, EX and WB, unless all operands are immediate, in which case only EX and WB are

- For the instruction LOAD a, b the argument b must be an immediate address or memory location and a must be a

- For the instruction STOR a, b the argument b must be an immediate address or register and a must be a memory

- For each of the remaining instructions the arguments a, b and c must all be registers or immediate

- You may assume for the sake of the questions that the ISA supports floating point arithmetic with no loss of precision

Trending now

This is a popular solution!

Step by step

Solved in 2 steps