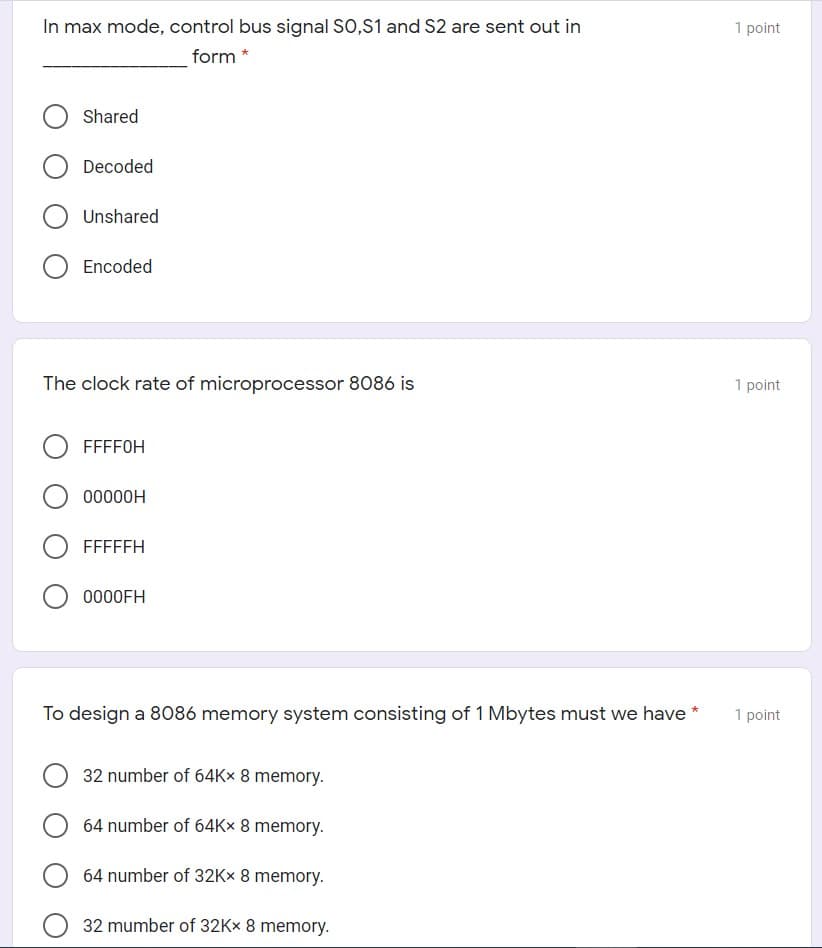

In max mode, control bus signal So,s1 and S2 are sent out in form * Shared Decoded Unshared O Encoded

Q: Nonsynchronous and synchronous buses are two different things.

A: Introduction: Time signals are sent together with each bit of data sent, making synchronised data…

Q: Considering the 3 bus SRC write the concrete RTN and control sequence for and ra,rb,rc.Explain why…

A: We will describe RTN by using it to describe SRC. ... R[3] Z; Control Sequence R[2]out, Yin;…

Q: (RISC-V) Write an instruction that calculates the bitwise Exclusive OR of x3 and 466 (in decimal)…

A: Destination register = x18Source register(first operand for ALU) = x3immediate value(second operand…

Q: II. IMPLEMENTATION OF SIMPLE SYSTEMS. Implement the given RTL below using bus connection and…

A: Answer: I have given answer in the handwritten format.

Q: Draw suitable diagrams for frame relay format and address field format, explain the followings with…

A: Frame format of the frame relay is shown below:…

Q: Draw the control unit and datapath for the following algorithm that returns an integer value. The…

A: The control unit and data path of the algorithm is given below.

Q: riefly why Direct Memory Address (DMA) is the most efficient in converting ultiple ADC channels at…

A: Contrast from Programmed I/O and Interrupt-Driven I/O, Direct Memory Access is a strategy for moving…

Q: When it comes to a single data route architecture, what is the most important disadvantage? It is…

A: Introduction: The process of picking a path for traffic within a network or across or across many…

Q: First address in block can be founded by setting rightmost 32- N bits to

A: Here we are asked about the first address of block (starting). IP is of 32 bits, which is divided…

Q: Instruction CLD belongs to Implied addressing and it sets the Carry Flag to one. Select one: True…

A: The given statement is false. CLD is an example of implied addressing mode It reset the DF flag to…

Q: Data bus is unidirectional. Select one: True False

A: According to the Question below the Solution:

Q: One of the disadvantages of the Bus topology that you should mention is the difficulty in…

A: Please find the detailed explanation in the following steps.

Q: b) Binary values of the select inputs S2, S1, and So that must be applied to BUS;

A: The question is to write the answer of question b) for the given problem.

Q: What is the most significant disadvantage of a single data route design? Multiple Multiplexors are…

A: Given that: What is the most significant disadvantage of a single data route design? Multiple…

Q: Calculate the locations of CS and IP of the ISR for the interrupt TYPE 123

A: IP:- IP are stored in the interrupt vector table that is located at the bottom of memory and give…

Q: Q1) Write the content of register and flags after executing each instruction below. Explain your…

A: The answer is in step 2:

Q: List two alternate designations for the PCI-Express bus.

A: PCI-Express bus is a fast constant PC advancement transport standard, expected to supersede the more…

Q: Q2/ A- Sum of series of 10 numbers stored at memory location 0100H:0500H and then store result in…

A: Move 00 to register B immediately for carry Load the data of memory [0500] into H immediately Move…

Q: The address bus consists parallel signal lines while data bus consists separate lines.

A: Question 1: Answer: False Explanation: Address bus: There are 16, 20, 24, or 32 parallel lines on…

Q: The idle state is one clock period long, is inserted in the the bus cycle, while the wait state…

A: Lets see the solution.

Q: Write three address code and quadruple for the expression a[i] = -b * (a[k--] – y[ k--] /2)

A: Three-address code is the intermediate code that is used by the optimizer compiler by breaking down…

Q: In a Mil-Std 1553 Bus, one of the Remote Terminals (Terminal Address 4) would like to send the…

A: The answer is

Q: System Bus is one of the structures of the computer. 1 True 2 False

A: In computer architecture, a bus is a subsystem that transfers data between components inside a…

Q: In a Mil-Std 1553 Bus, one of the Remote Terminals (Terminal Address 4) would like to send the…

A: a. MIL-STD-1553 is a tactical standard that characterizes mechanical, electrical, and working…

Q: The difference between IP& IR registers is in:

A: Answer: The IR is utilized to store the guidance word. At the point when the CPU brings a guidance…

Q: Consider a system whose RTL code is given as follows: assume that j,o,h,n are mutually exclusive…

A: Here I have about a and c answer which i have gave in step 2 and step 3 below, as we assumed that…

Q: Write three address code and quadruple for the expression a[i] = -b * (a[k--]- y[ k--] /2)

A: a[I]=-b*(a[k--]-y[k--]/2)

Q: Write down the control sequence for the following instructions (given as operation source…

A: Task : Write the control sequence for the given instructions.

Q: IMPLEMENTATION OF SIMPLE SYSTEMS. Implement the given RTL below using bus connection and tri-state…

A: Implementation System:- Implement the given RTL below using bus connection and multiplexer and/or…

Q: Control Operation performed Result = codes 1 00 0 01 1 01 A or B A – B A+B A xor B A and B 1 10 1 11…

A:

Q: IMPLEMENTATION OF SIMPLE SYSTEMS. Implement the given RTL below using bus connection and tri-state…

A: A transport network is a neighborhood (LAN) geography in which every hub - - a workstation or other…

Q: Write the concrete RTN and control signals for not and shra signals for a 2-bus architecture.

A: T0 MA <- PC; T1 PC <- PC+4:MD <-M[MA]; T2 IR <- MD; T3 A <- R[rb]; T4 R[ra] <-…

Q: Draw the functional block diagram of the datapath unit.

A: Functional block diagram:

Q: Describe a linear address

A: Linear address: The address is used to denote an exact location in the memory. A hexadecimal…

Q: Difference between address bus & data bus is: a) Both carry bits in either directions. b) Address…

A: The answer is given below:

Q: mplement of ALU Control Block (MIPS 32 bits) shown based on the following TT with 6 input variables…

A:

Q: Control bus is bidirectional. Select one: O True O False

A: Here in this question we have asked about control bus.weather the control bus is…

Q: Buses use either synchronous timing or asynchronous timing. With synchronous timing, the occurrene…

A: Answer is option d The clock

Q: Considering the 2 bus SRC write the concrete RTN and control sequence for ldr ra,c1

A: CPU Design Control Unit Generates the control signals in the correct order to ... RTN Assignment…

Q: iple signals need to

A: Answer is multiplexer.

Q: Example: show the control signals needed to perform Add R1, R2, R0 using: a. Three bus organization…

A:

Q: 3-)A BUS structure can be built using RS232 communication. True False

A: The given statement is TRUE.

Q: 3-)It is possible to establish a BUS structure with RS232 communication. True False

A: Here is the Answer and Explanation

Q: this: For register RO to R63 in a 16-bit bus system; what is the MUX size we use? and how many…

A:

Q: Explain Priority Arbitration in CAN BUS.

A: ANSWER : Since a serial communication system such as CAN is based on a two-wire connection between…

Q: Buses use either synchronous timing or asynchronous timing. With synchronous timing, the occurrence…

A: Busesuse either synchronous timing or asynchronous timing.With synchronous timing, the occurrence…

Q: Describe the sequence of events in a bus request operation.

A: A control bus is part of the system bus in computer architecture, and it is used by CPUs to…

Q: Analyse (using appropriate clock diagrams) burst read transfer for AMBA AHB bus protocols with the…

A: Advanced Microcontroller bus architecture: The Advanced microcontroller bus architecture (AMBA )…

Q: After executing : MOV SP,-12012 PUSH SP What is the content in hex of the byte in memory whose…

A: We have 2 instructions as- MOV SP, -12012 PUSH SP We need to tell that what value is stored at…

Q: As a general rule, is it better to switch auxiliary buses in parallel or drop-and-pick-up? why?

A: Introduction: Drop and pick-up: It is a strategy in which a single bus is used to pick and drop the…

Step by step

Solved in 2 steps

- If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the fetch cycle is 40% of the processor cycle time, what memory access speed is required to implement load operations with zero wait states and load operations with two wait states?A(n) ________________ instruction always alters the instruction execution sequence. A(n) ______________ instruction alters the instruction execution sequence only if a specified Condition is true.Will upvote! Find the memory address of the next instruction executed by the microprocessor, when operated in the real mode, for the following CS:IP and 80286 register combinations: a. DS=2F2E & DX=9D64 b. CS=9F7A & IP=AB27 c. ES=DE21 & DI=D75F d. SS=FF5C & BP=92B8 e. DS=DC67 & CX=2FE8

- Registers in RISC-V are 64-bit. For the sake of simplicity, consider the following instructions operating on 32-bit registers. Assume that registers x5 and x6 hold the values 0xBBBBBBBB and 0x00000000, respectively. What is the value in x6 for the followingslli x6, x5, 6 Using the result from the part above, what is the value in x6 for the following instruction. srli x6, x6, 6In the Intel 8086 microprocessor, suppose the register AX contains the data 35AB H. What will be the contents of AX after executing the following programs? Assume that the initial content on the Carry Flag (CF) is one for all the calculations. You MUST clearly show ALL your steps in obtaining your final result for getting full and/or partial credit. Please present your final result in Hexadecimal format. (a) MOV CL,04H SHR AX,CL RET (b) MOV CL,04H RCR AX,CL RETWhat happens if an instruction is not accepted and it writes to VA page 30? In the following scenarios, a software-managed TLB would be faster than a hardware-managed TLB:

- Suppose a specific MCU has the following size of memories: 2 M byte of flash, starting from 0x0800_0000, 256 k byte of SRAM starting from 0x2000_0000, and 8 k byte registers for GPIOs, start at 0x4001_0000. (Note that 0x is the prefix for hexadecimal numbers.) Draw the memory map based on your calculations for the addresses.Q:Answer the following sentence with (True) or (False) and correct the false answer: 1. You can input data of size 16-bit through the fixed port. 2. In the maximum mode, the status signals S₁, S₂ and S3 are controlled by the bus controller. 3. HLDA is an output signal. 4. In 8086, when executing the instruction MOV AL, [SI+100D H] where SI-100AH, Ao=0 and BHE=1 5. When S, is 0, the TF is disabled.1. T/F - if (B)=006000 (PC)=003600 (X)=000090, for the machine instruction 0x032026, the target address is 003000.2. T/F – PC register stores the return address for subroutine jump.3. T/F – S register contains a variety of information such as condition code.4. T/F – INPUT WORD 1034 – This means Operating system should reserve 1034 bytes in memory5. T/F - In a two pass assembler, adding literals to literal table and address resolution of local symbol are done using first pass and second pass respectively.

- Single instruction computer (SIC) has only one instruction that for all operations our MIPS does. The instruction has the following format. sbn a, b, c # Mems[a]=Mem[a]- Mem[b]; if (Mem[a]<0) go to PC+c For example, here is the program to copy a number from location a to location b: Start: sbn temp, temp, 1 sbn temp, a, 1 sbn b, b, 1 sbn b, temp, 1 So build SIC program to add a and b, leaving the result in a and leaving b unmodified.On a uniprocessor, portion A of program P consumes 24 seconds, while portion B consumes 822 seconds. On a parallel computer, moderately serial portion A speeds up 4 times, while perfectly parallel portion B speeds up by the number of processors. 1- What is the speedup of program P on 1,024 processors? _______ times 2- How many processors are required to achieve at least half the theoretical maximum possible speedup on P?in 80886 microprocessor Suppose that. DS = 0200H, BX = 0300H, and DI-400H Determine the memory address accessed by each of the following instructions, assuming real mode operation: (1) MOV AL,[1234H] (2) MOV AX,[BX] (3) MOV [DI]AL