Question 9 What register is used to send the return value to the operating system O/S?

Question 9 What register is used to send the return value to the operating system O/S?

Chapter6: Managing Multiple Worksheets And Workbooks

Section: Chapter Questions

Problem 23RA

Related questions

Question

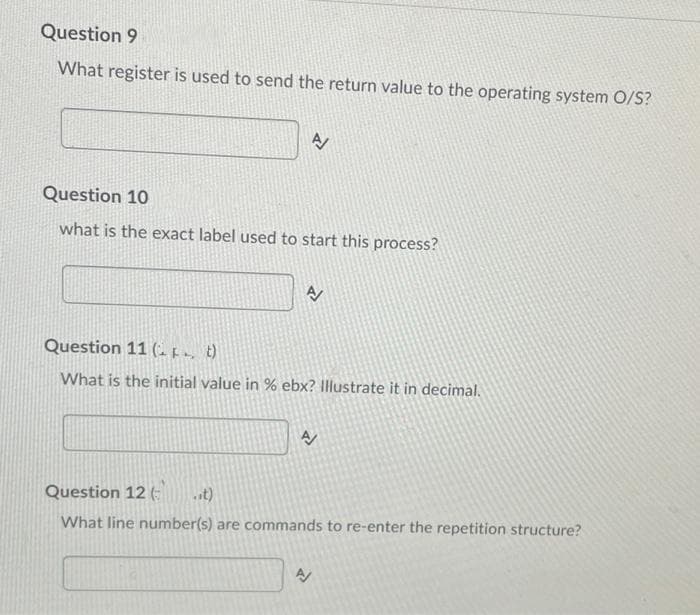

Transcribed Image Text:Question 9

What register is used to send the return value to the operating system O/S?

A

Question 10

what is the exact label used to start this process?

Question 11 (En t)

What is the initial value in % ebx? Illustrate it in decimal.

Question 12 (

it)

What line number(s) are commands to re-enter the repetition structure?

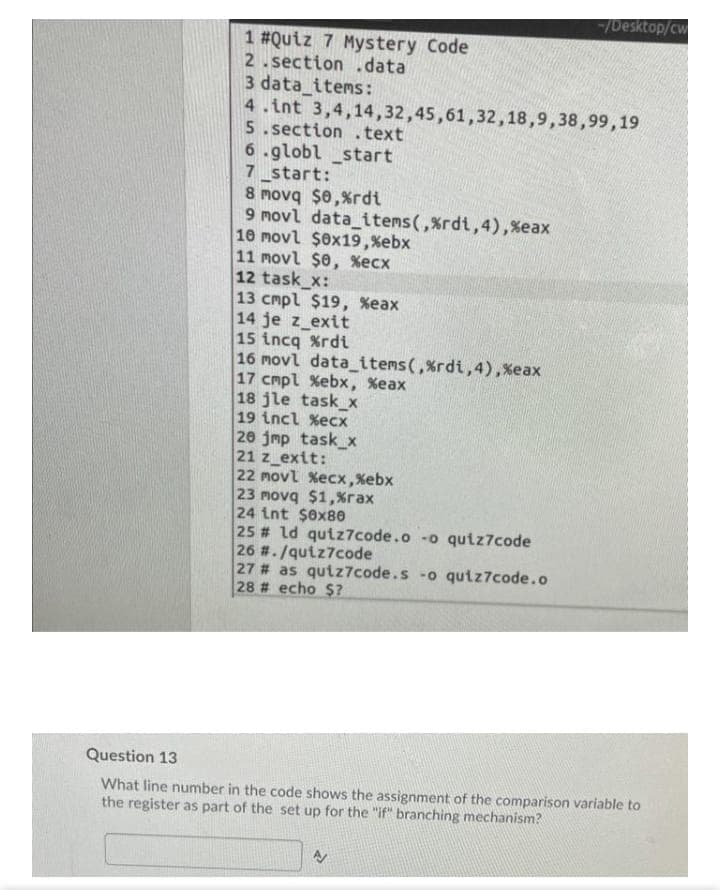

Transcribed Image Text:/Desktop/cw

1 #Quiz 7 Mystery Code

2.section.data

3 data_items:

4.int 3,4,14,32,45,61,32,18,9,38,99,19

5.section .text

6 .globl _start

7_start:

8 movq $0,%rdi

9 novl data_items(,%rdt,4),%eax

10 movl $0x19,%ebx

11 movl $e, %ecx

12 task_x:

13 cmpl $19, %eax

14 je z_exit

15 incq Xrdi

16 movl data_items(,%rdi,4),Xeax

17 cmpl Xebx, Xeax

18 jle task_x

19 incl Xecx

20 jmp task_x

21 z_exit:

22 movl Xecx,Xebx

23 movq $1,%rax

24 int $ex8e

25 # ld qutz7code.o -o qutz7code

26 #./qutz7code

27 # as quiz7code.s -o quiz7code.o

28 # echo $?

Question 13

What line number in the code shows the assignment of the comparison variable to

the register as part of the set up for the "if" branching mechanism?

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Np Ms Office 365/Excel 2016 I Ntermed

Computer Science

ISBN:

9781337508841

Author:

Carey

Publisher:

Cengage

Np Ms Office 365/Excel 2016 I Ntermed

Computer Science

ISBN:

9781337508841

Author:

Carey

Publisher:

Cengage