2- According to the FPGA's cells studied, how many FPGA cells are required to implement an 8 bit ripple carry counter ?

2- According to the FPGA's cells studied, how many FPGA cells are required to implement an 8 bit ripple carry counter ?

Chapter3: Data Representation

Section: Chapter Questions

Problem 11VE: Most Intel CPUs use the __________, in which each memory address is represented by two integers.

Related questions

Question

digital advanced , please solve question 2

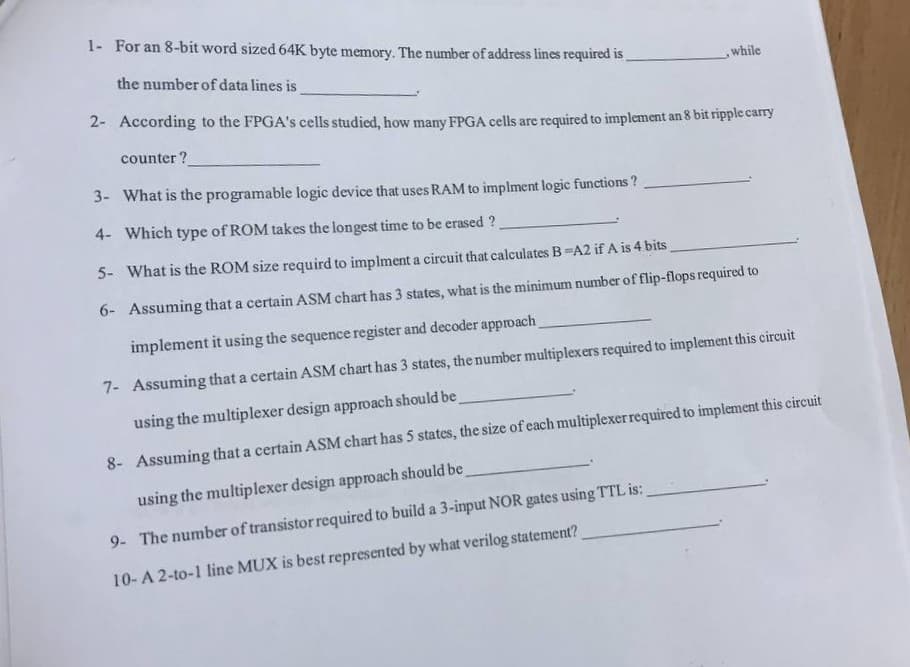

Transcribed Image Text:1- For an 8-bit word sized 64K byte memory. The number of address lines required is,

the number of data lines is

while

2- According to the FPGA's cells studied, how many FPGA cells are required to implement an 8 bit ripple carry

counter ?

3- What is the programable logic device that uses RAM to implment logic functions ?

4- Which type of ROM takes the longest time to be erased ?

5- What is the ROM size requird to implment a circuit that calculates B A2 if A is 4 bits

6- Assuming that a certain ASM chart has 3 states, what is the minimum number of flip-flops required to

implement it using the sequence register and decoder approach

7- Assuming that a certain ASM chart has 3 states, the number multiplexers required to implement this circuit

using the multiplexer design approach should be

8- Assuming that a certain ASM chart has 5 states, the size of each multiplexerrequired to implement this circuit

using the multiplexer design approach should be

9- The number of transistor required to build a 3-input NOR gates using TTL is:

10-A 2-to-1 line MUX is best represented by what verilog statement?

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by step

Solved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning