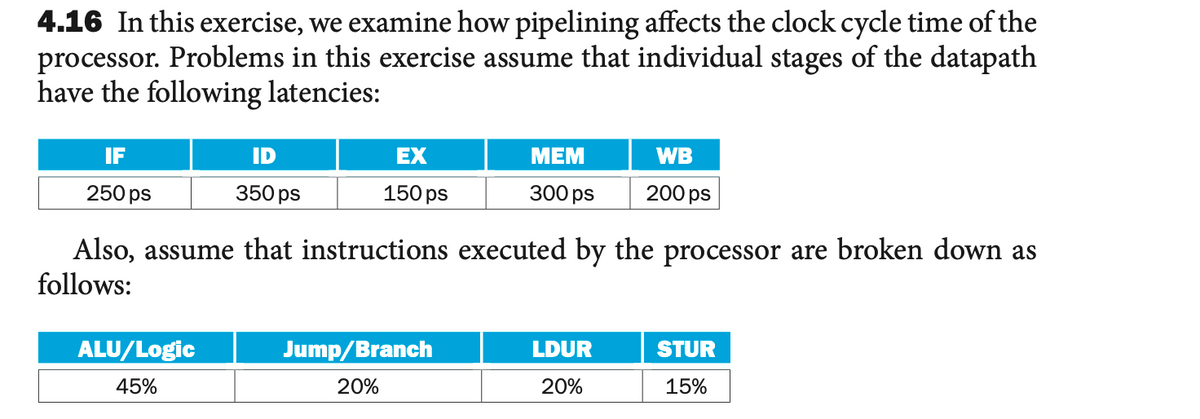

4.16 In this exercise, we examine how pipelining affects the clock cycle time of the processor. Problems in this exercise assume that individual stages of the datapath have the following latencies: IF ID EX MEM WB 250 ps 350 ps 150 ps 300 ps 200 ps Also, assume that instructions executed by the processor are broken down as follows: ALU/Logic Jump/Branch LDUR STUR 45% 20% 20% 15%

Q: In JAVA

A: It seems like the text you provided is a mixture of project requirements, course descriptions, and…

Q: Assume the data length of an IPv4 datagram is 100000 and the minimum size of the datagram of the…

A: To determine if padding is necessary and if so, how many bytes are needed, let's break down the…

Q: software enginering cocomo model questıon = Calculate the tıme and labor costs and man/month ratio…

A: Your calculations using the COCOMO (Constructive Cost Model) basic model seem to be correct.The…

Q: Based on this article entitled as "Own Data? Ethical Reflections on Data Ownership" by Patrik…

A: Approach to solving the question: Detailed explanation: Examples: Key references:Philosophy

Q: Please check the answer twice and add explanation ... Don't use ai

A: 3.a Compute n if p = 205951 and q = 470593.We can simply multiply p and q to compute n when p =…

Q: I need this in the coral language

A: Here's a summary of Project 8-1 in Coral:1. Data Reading: Loo de ramen data from a CSV file into a…

Q: Alert dont submit AI generated answer.

A: The objective of the question is to design and configure a network for two offices using Variable…

Q: My code does not produce the required output, can anyone let me know what seems to be off? Input:…

A: Insertion Method (insert_after) Issue: When you insert nodes after a certain node, the next and prev…

Q: Are there any specific evaluation reports that should be produced when implementing a cyberattack…

A: The objective of the question is to understand the types of evaluation reports that should be…

Q: 23. What are agents who have the capability of maintaining an internal state of information?…

A: Processing Agents:These agents are designed to process information by performing computations,…

Q: Need help ! I have attached the problem! I am taking database management course.

A: For 2NF:Each attribute in the original table depends on the primary key (Emp_ID).There are no…

Q: Provide an example of how a program you wrote this semester used the OOP inheritance principle.…

A: This semester, I worked on a program called "Vehicle Management System" for a fictional car rental…

Q: An organization is granted the block 108.153.200.40/17. The administrator wants to create 100…

A:

Q: Consider the following problem: 1. You have a four-gallon jug and a three-gallon jug, neither of…

A: The water jug problem is resolved by this Prolog program by specifying the starting and end states…

Q: For the given 2-3 tree: Add node 65 Remove node 20 50 90 120 150 30 40 60 80 100 110 130 140 160 ?

A:

Q: 1. Given that Valley Enterprises opted to implement Voice over Internet Protocol (VoIP) servicein…

A: The objective of the question is to identify the negotiations that should have taken place between…

Q: Given the matrix 5 0.6 0.1 A 6 -0.1 1 02 find both the Gerschgorin row and column disks, and use…

A: This MATLAB code calculates the Gerschgorin disks, computes the eigenvalues of the matrix, and then…

Q: In NLP there is a universal set of stop words that all programmers follow. A) True B) False

A: In the realm of natural language processing (NLP), stop words play a crucial role in text analysis…

Q: section ALook at the class definitions below and answer the questions based on it:class Node{//…

A: Step 1: a) Here are the files 'Node.java' and 'BinarySearchTree.java':Node.javapublic class Node {…

Q: How many bytes from the very start of the Ethernet frame does the ASCII “O” in “OK” (i.e., the HTTP…

A: An Ethernet frame is the basic unit of communication in an Ethernet network. It consists of a header…

Q: My code does not produce the required output, can anyone let me know what seems to be off? Input:…

A: The objective of the question is to identify the issue in the provided Python code which is causing…

Q: A system has four processes and five allocatable resources. The current allocation and maximum needs…

A: To solve the question using the Banker's Algorithm, we need to follow these steps: 1.…

Q: Need help ! I have attached the problem! I am taking a database management course. i am using mysql…

A: CREATE TABLE Statement:This statement creates a table named Employee.It defines five columns:Emp_ID…

Q: Assume that G is a Context Free Grammar as the 4-tuple (V,T,S,P) where V={S,A,B} set of non-terminal…

A: Option 1. P is defined as {X Y: such that X V. Y (V T)+ } (V T)+ defines one or more…

Q: Which is an example of an operation that can be performed using declarative schema mapping but not…

A: Detailed explanation:Let's examine each choice in more detail: (A) Aggregating data: is the process…

Q: Please trace the calculation on a 4-bit two’s complement Adder/Subtractor. Fill out the tables…

A: Let's trace the calculation of A+B, where A=5 and B=3 using a 4-bit two's complement…

Q: Please check the answer twice and add explanation to.every step Note - don't use AI answer ( i will…

A: The hexadecimal number is:0001 -> 10111 -> 71000 -> 81111 -> F0000 -> 00000->…

Q: Integer numSize is read from input. ArrayList colorsList contains numSize strings read from input.…

A: Completing the missing code: In order to complete the missing code we need to implement an enhanced…

Q: Draw the collaboration diagram for online food ordering system. Identify minimum 3 objects and 10…

A: A collaboration diagram, sometimes referred to as a communication diagram, uses the Unified Modeling…

Q: 1.10 A hash table is created to store integer keys using a hash function h(k) = k mod 19. The…

A: Calculate the initial position: The initial position for a key in the hash table is determined by…

Q: After visiting a node, if we determined that it can possibly lead to a solution we will expend it.…

A: The correct term for a node that, after evaluation, is determined to potentially lead to a solution…

Q: MATLAB CODES ONLY

A: Step 1:Define the Differential Equation Function (myODE.m): function dxdt = myODE(t, x) dxdt =…

Q: w |w Consider alphabet Σ = {0,1} and language L = = {wες : Σw # i=1 i=1 regular. Σ (1 - w;)}. Prove…

A: Let's dive deeper into the explanation of why the language L defined as L = {Σ^i: Σ(1-0)^i} is a…

Q: IN JAVA PLEASE --------------------------------------------------- Main Menu 1 : Student Management…

A: Creating a comprehensive Java program for the provided menu-driven student management system…

Q: A Python Program with 10 menu choices. program could answer 1. Which states did not present data?2.…

A: I have provided the comments in the code so that you can easily…

Q: How many instances of Point are created in the following lines of code? How do you get the…

A: Step 1: To determine how many instances of Point are created, we look at each line where a new Point…

Q: the measured Consider the figure below, which plots the evolution of TCP's congestion window at the…

A: Step 1:Understanding the Graph:The graph depicts the evolution of TCP's congestion window size…

Q: Given a stack of objects of type char, write the output and the stack contents atthe return of each…

A: The functionality of the stack functions used in the above table:size(): Returns the integer…

Q: Suppose a program have 40% of its code enhanced to yield a system speedup of 4.3 times faster. What…

A: Approach to solving the question: Detailed explanation: Examples: Key references: computer science

Q: Consider alphabet Σ = {0,1} and language Lo₁ = {weΣ* : w=0"1" for some nonnegative n€ Z}. Prove or…

A: Understanding L01: The language L01 consists of strings over the alphabet Σ={0,1} Σ={0,1} where…

Q: In the calculation of the molecule of H2O, a researcher used the basis set 6-311+G(d,p).(i) Using…

A: EXPLAINED QUESTIONS ASKED IN DETAILED USING 311+G(d,P) and context of split valence basis sets.

Q: The following should be done in a user experience analysis to understand the problem being addressed…

A: Step 1: All the options are correct Document and understand the content that is presented as part…

Q: Solve the questions on recursive function;

A: a) To draw the recursion tree for computing combinations(4, 7), we can start with the initial call…

Q: For this Context Free Grammar: G = ( {S}, {a+b, a-b, +, −}, S, {S S+S | S-S|a|b}) This related Parse…

A: :context-free grammar (CFG).The string associated with the given parse tree is determined by tracing…

Q: ⚫ Each prescription is exclusive to a doctor. However, each doctor may compose a large number of…

A: ### 1. Conceptual Database Design: #### Entities: 1. **Doctor**: Represents the medical…

Q: Many companies are undergoing server virtualization. This is the concept of putting…

A: 1. **Identify Costs**: - **Initial Costs**: Includes the cost of virtualization software licenses,…

Q: The "MULTIEQUAL" p-code operator has not been considered in the script. Please identify the correct…

A: 1. One can simply add PcodeOp.MULTIEQUAL into 'binary_operators' and the resulted script will be…

Q: Question 3: You are tasked with developing an Arduino-controlled temperature management system for…

A: The image you sent seems to be a flowchart outlining the design process for your Arduino controlled…

Q: MC Q. 27 You're using Multiple Choice flash hard 7 SSD Saved data storage when you save a file to…

A: Local storage is basically the process of storing your digital files and documents on a physical…

Q: For each of the following problems, you should write your answer as an expression. Do not give the…

A: We will be using permutations.Step 1: Determine the given:Given:n = 26k = 14where:n is the total…

4.16.1 [5] <§4.5> What is the clock cycle time in a pipelined and non-pipelined processor?

4.16.2 [10] <§4.5> What is the total latency of an LDUR instruction in a pipelined and non-pipelined processor?

4.16.3 [10] <§4.5> If we can split one stage of the pipelined datapath into two new stages, each with half the latency of the original stage, which stage would you split and what is the new clock cycle time of the processor?

4.16.4 [10] <§4.5> Assuming there are no stalls or hazards, what is the utilization of the data memory?

4.16.5 [10] <§4.5> Assuming there are no stalls or hazards, what is the utilization

of the write-register port of the “Registers” unit?

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

- In this exercise we examine in detail how an instruction is executed in a single-cycle datapath. Problems in this exercise refer to a clock cycle in which theprocessor fetches the following instruction word: 10101100100001010000000000011100 Assume that the data memory is all zeros and that the processor’s registers havethe following values at the beginning of the cycle in which the above instructionword is fetched: R0 R1 R2 R3 R4 R5 R6 R8 R12 R31 0 2 4 6 13 10 12 16 24 31 a. What are the outputs of the sign-extend and the jump “Shift-Left-2” (near the topof the following Figure) for this instruction word? (Pic3) b. What are the values of ALU control unit’s inputs (ALUOp and Instruction[5-0])for this instruction? c. What is the new PC address after this instruction is executed? Highlight the paththrough which this value is determined. d. For the ALU and the two add units, what are their data input values? ALU Add (PC+4) Add…10. Consider the following code: .386 .model flat, stdcall .stack 4096 ExitProcess PROTO, dwExitCode : DWORD .data aVal SDWORD -6 bVal SWORD 19h cVal DWORD 17h .code mov edx, aVal add edx, edx mov eax, 0FFFFFFFFh mov ax, bVal sub edx, eax Show the content of edx and eax after executing each instruction in Hexadecima4.19.16: [5] <COD §4.6>. In this exercise, we examine how pipelining affects the clock cycle time of the processor. Problems in this exercise assume that individual stages of the datapath have the following latencies: Also, assume that instructions executed by the processor are broken down as follows: (a) What is the clock cycle time in a pipelined and non-pipelined processor? (b) What is the total latency of an lw instruction in a pipelined and non-pipelined processor? (c) If we can split one stage of the pipelined datapath into two new stages, each with half the latency of the original stage, which stage would you split and what is the new clock cycle time of the processor? (d) Assuming there are no stalls or hazards, what is the utilization of the data memory? (e) Assuming there are no stalls or hazards, what is the utilization of the write-register port of the "Registers" unit? No hand written and fast answer with explanation

- Considering the following contents of Stack Segment (SS) Register and Stack Pointer (SP) Register: SS = A5B0H, SP = 4DF0H (a) Calculate the values of Top of Stack (ToS) and Bottom of Stack (BoS)? (b) Consider the following operations on the stack: PUSH AX PUSH [CX] PUSH 10 POP [BX] POP AX What is the value of ToS after all these operations? Also, provide the value of ToS after each instruction.We will explore the impact of cache capacity on performance, focusing exclusively on the data cache and excluding instruction storage in the caches. Cache access time is directly linked to its capacity. For the sake of simplicity, let's assume that accessing the main memory takes 100ns, and in a specific program, 50% of instructions involve data access. Two distinct processors, denoted as P1 and P2, are engaged in executing this program. Each processor is equipped with its own L1 cache. L1 size L1 Miss Rate L1 Hit Time P1 64 KB 3.6% 1.26 ns P2 128 KB 3.1% 2.17ns (a) What is the AMAT for P1 and P2 assuming no other levels of cache?17. Consider the following hypothetical instruction: SubMem R1, mem1, mem2 This instruction works as follows: \[ \mathrm{R} 1 \leftarrow \text { [mem1] - [mem2] } \] In a multi-cycle datapath implementation, this instruction will: a. Use the MDR twice b. Use the ALU once c. Use the "shift to left" unit twice d. None of the above Answer: B 18. Consider the following hypothetical instruction: Mems mem1, R1, mem2 This instruction works as follows: \[ \text { [mem1] } \leftarrow \mathrm{R} 1 \text { - [mem2] } \] One of the following is correct about this instruction: a. It will not need theBregister b. It will require priting into MDR twice c. It will require writing into the ALUout three times d. None of the above Answer: A 19. By comparing the hypothetical instructions given in Questions (17) and (18), if we run these instructions on the same processor, then one of the following is correct: a. Both instructions have the same CPI b. Mems executes faster than SubMem c. SubMem executes…

- In this exercise we compare the performance of 1-issue and 2-issue processors, taking into account program transformations that can be made to optimize for 2-issue execution. Problems in this exercise refer to the following loop(written in C):for(i=0;i!=j;i+=2)b[i]=a[i]–a[i+1];When writing MIPS code, assume that variables are kept in registers as follows, and that all registers except those indicated as Free are used to keep various variables, so they cannot be used for anything else. i j a b c Free R5 R6 R1 R2 R3 R10,R11,R12 Translate this C code into MIPS instructions. Your translation should be direct, without rearranging instructions to achieve better performance.Consider a multilevel computer in which levels are vertically stacked, with the lowest level being level 1. Each level has instructions that are m times as powerful as those of the level below it; that is, one level r instruction can do the work of m instructions at level r-1. However, n instructions at level r-1 are required to interpret each instruction at level r. Given this, answer the following questions: If a level 1 program requires k seconds to run, how long would the equivalent program take to run at levels 2, 3 and 4. Express your answer in terms of n, m, and r. What is the performance implication for the program if n > m? Conversely, what is the implication if m > n? Which case do you think more likely? Why?Consider the following instruction:Instruction: Add Rd, Rs, RtInterperation: Reg[Rd] = Reg[Rs] + Reg[Rt] RegWrite MemRead ALUMux MemWrite ALUOp RegMux Branch a, What are the values of control signals generated by the control in Figure 4.2 for the above instruction? b, Which resources (blocks) perform a useful function for this instruction? c, Which resources (blocks) produce outputs, but their outputs are not used for this instruction? d, which resources (blocks) produce no output for this instruction?

- Write MIPS assembly for the following function. Assume N is passed to yourfunction in register $a0. Your output should be in register $v0 at the end of yourfunction. Note: You must implement this function recursively. The purpose of thisassignment is to learn how to manipulate the stack correctly in MIPS. int Myfun (int N){ if (N<3) return 1; return ( 2* Myfun(N-1)+ Myfun(N-2));}Please explain each instruction with a comment. Please submit your source codeand a screenshot that shows the registers with correct output value for N=3, i.e.,Myfun(3) returns 3 and Myfun(4) returns 7Q1: Suppose the hypothetical processor has two I/O instructions: (3+3+3)0011=Load AC from I/O0111=Store AC to I/OIn this case, the 12-bit address identifies a particular external device. Show the program execution using figure for the following program:a) Load AC from device 6b) Add contents of memory location 880c) Store AC to device 7 (Note: Question is to be solved similar to the pictures attached with minimum explaination of a line or two with the steps and SHOULD include the memory location 880 as stated in the question)In this exercise, we examine in detail how much an instruction is executed in a single-cycle Datapath. The problem refers to a clock cycle in which the processor fetches the following instruction word: 1010 1100 0110 0010 0000 0000 0001 0100. Assume that data memory is all zeros and that the processor's registers have the following values at the beginning of the cycle in which of the instruction word is fetched: (See image attached) What is the new PC address after this instruction is executed? Highlight the path through which this value is determined?