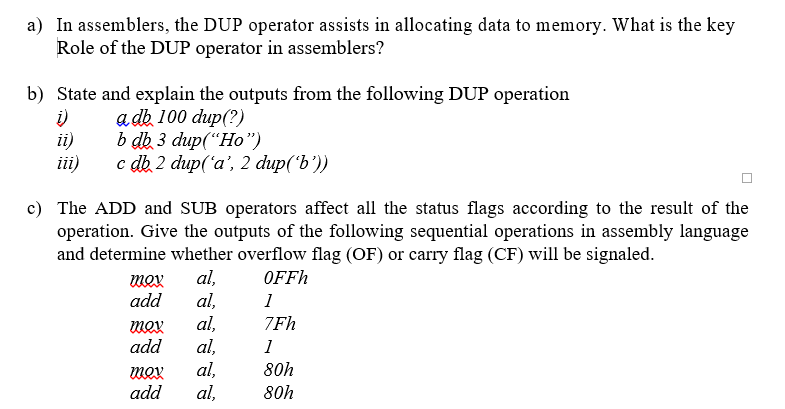

a) In assemblers, the DUP operator assists in allocating data to memory. What is the key Role of the DUP operator in assemblers?

Q: (a) Set a base address for a generic PIO at 0x10008000 called pioBase. Assume this is just an 8-bit…

A: Change in memory location an interrupt is set to send signals, when we change in memory.

Q: Explain block diagrams and examples of (REG, memory),( REG, REG), (memory, immediate ), (REG,…

A: Register is a temporary unit of storage that quickly accepts the data, stores it for a while, and…

Q: Examine the advantages of using Direct Memory Access over Interrupt Driven I/O.

A: Introduction: Direct memory access refers to the method of transmitting data without using the CPU…

Q: d. Outline the various steps of the fetch-decode-execute cycle. In your explanation, you should…

A: Instruction cycle : Every instructionis execution consists of three phases they are : 1.Fetch :…

Q: Define uniform memory access.

A: Shared memory UMA:

Q: Explain the notion of locality of reference and why it is important in memory systems.

A: In software engineering, locality of reference, otherwise called the standard of locality, is the…

Q: Describe the disadvantages of memory address translation with segmentation technique

A: Segmentation is a memory management technique in which the memory is divided into the variable size…

Q: Assume the following values are stored at the indicated memory addresses and registers: Address…

A: The Answer starts from step-2.

Q: DMA and cache memory are contrasted.

A: Introduction: DMA is an abbreviation for Direct Memory Access. It is a technology in which I/O…

Q: make a virtual memory specification

A: This question is about a standard for virtual memory.

Q: Variable x' is assigned to X19 Variable 'y' is assigned to X20 Assume the operation returns the…

A:

Q: On the basis of the following considerations, compare memory and registers in tabular form.…

A: Intro The question is about Difference between memory and registers in tabular form on the basis of…

Q: 4. Explain the steps of the fetch-decode-execute cycle. Your explanation should include what is…

A: Fetch-decode-execute cycle stepsFetch-decode-execute cycle is a standard process that describes the…

Q: 9- Design a simple memory of type RAM starting from address 0001 to 0110 with memory width is 8…

A: Actually, memory is used to stores the data.

Q: Explain the following with respect to 8086 Microprocessor. a. Procedures with example b. Different…

A: The instructions are given by the program accordingly. The program is used to solve everyday…

Q: Define memory hierarchy.

A: The memory hierarchy is the organization of the several parts of the computer memory in a…

Q: Explain Uniform memory access.

A: Shared memory UMA:

Q: (d) Assume that a, b, c, x are stored in registers $s1-$s4. Translate the fol- lowing high-level…

A: MIPS stands for "Million instruction per second". MIPS assembly language is simply assembly code or…

Q: Using indirect addressing mode (like for LDI and STI), the first memory location contains the…

A: Find the answer given as below :

Q: Explain the role of base and limit register in memory protection. Determine whether the following…

A: The formula to find if the logical address generated by the CPU is legal or illegal can be found…

Q: 1. Implement the following calculation in assembler using AX,BX,CX and DX registers and describe…

A: We need to implement the given calculation in 8086 and find the final state of CF.

Q: c) Design and write an assembly language program for the 68000 Microprocessor that can give an…

A: 68000 processor has 16 registers that are directly accessible by the user. Those are: 8…

Q: 1) Explain the general & pointer registers?

A: “Since you have asked multiple question, we will solve the first question for you. If you want any…

Q: Given X, and Y memory locations, write an assembler codes to find number of in each location of X…

A: The Answer is

Q: 1-Translate the following C programs to MIPS assembly program (Please explain each instruction in…

A: Assembly Language: Assembly language is the low level language which is understandable by the…

Q: In assemblers, the DUP operator assists in allocating data to memory. What is the key role of the…

A: The DUP operator is used in Microsoft Macro Assembly or MASM. MASM offers a number of benefits over…

Q: 8259 microprocessor is used to increase the interrupt handling capability of 8085 and 8086…

A: Intel 8259 is designed for Intel 8085 and Intel 8086 microprocessor. It can be programmed either in…

Q: Write simple instructions (simple program) that will add two consecutive bytes of data storied with…

A: In a direct addressing mode, the data to be worked upon is in a memory location and as an operand,…

Q: Example 2: The memory location 2050H holds the data byte F7H. Write instructions to transfer the…

A: LXI instructions are used to load the 16-bit address into the register pair. We use this instruction…

Q: Assembly language programming Question: The solution to the question should only run/execute ARM UAL…

A: .<code>ldr r0, =dataldr r1, [r0]ldr r2, [r0,#4]ldr r3, [r0,#8]ldr r4, [r0,#0xc]add r8, r1,…

Q: 1-Perform the following operation using the direct addressing mode, index addressing mode, base…

A: Answer : In direct addressing mode, address field within the guidance contains the powerful location…

Q: Describe the advantages of memory address translation with segmentation technique.

A: the advantages of memory address translation with segmentation techniques are given below :

Q: What is the 8086 microprocessor's minimum and maximum mode?

A: 8086 microprocessor: 8086 is a 16-bit microprocessor. It is designed by intel in 1976. 8086…

Q: C) If you want to Design 8K-byte memory starting from (B000)H by using a memory chip with size (4096…

A: As per the answering guidelines, solving the first 3 question. 1. Number of 4096x2 chips required =…

Q: DATA DEFINING ASSEMBLER DIRECTIVES IDENTIFY THE TYPE, LENGTH AND SIZE OF THE GIVEN 1. MEM DW…

A: The answer is given in the below step

Q: Explain the difference between memory-mapped I/O and instruction-based I/O.

A: Input and output (I/O) devices: The devices which are used to communication with computer system…

Q: Draw and explain the block diagram of the memory unit which is accessed by its content. Also explain…

A: Please find the answer below:

Q: 6. Explain the steps of the fetch-decode-execute cycle. Your explanation should include what is…

A: Instruction Cycle: A program that resides in a computer's memory unit is a sequence of…

Q: Define the term " preprocessor include " .

A: The #include preprocessor mandate is utilized to glue code of given record into current document. It…

Q: C)Explain the principles of content-addressable memory.

A: Content-Addressable Memory is a Special Type of Computer Memory Used in Certain Very High-Speed…

Q: Explain memory leak.

A: The memory leak occurs, when a piece of memory which was previously allocated by the programmer.…

Q: 10- Design a simple memory of type RAM starting from address 0011 to 0111 with memory width is 8…

A: “Since you have asked multiple question, we will solve the first question for you. If you want any…

Q: Describe the process of segmentation in 80386 microprocessor

A: GIven Describe the process of segmentation in 80386 microprocessor.

Q: 2. Assume that these registers contain the following: A=F0,B=55, and R1-90. Perform the following…

A:

Q: t, and the Stack Segment should all be distinguished. Determine the combination of registers that…

A: Code segment (CS): code segment is utilized for tending to memory area in the code segment of the…

Q: Show how the decimal value 2019111310 would be stored by byte-addressable machines with 32-bit…

A:

Q: Q1: Fill with the required information assuming that memory byte addressable using:

A: I have solved the problem & filled the table in the two ways mentioned in the question. If you…

Step by step

Solved in 2 steps

- (ASM) For the following C statement, what is the corresponding MIPS assembly code? Assume that the variables f, g, h, i, and j are assigned to registers $s0, $s1, $s2, $s3, and $s4, respectively. Assume that the base address of the arrays A and B are in registers $s6 and $s7, respectively. B[f] = A[(i-h)+j] + g;Translate the following pseudo code into MIPS assembly to show each of the addressing modes covered in this chapter. Note that variables x and y are static and volatile, so should be stored in data memory. When using register direct access, you do not need to store the variables in memory. main() { static volatile int miles = prompt("Enter the number of miles driven: "); static volatile int gallons = prompt("Enter the number of gallons used: "); static volatile int mpg = miles / gallons; output("Your mpg = " + mpg);}Explain the multithreading capability of the CPU and go through the three (3) different types of multithreading in a nutshell.

- Please solve and show all work. For the following C statement, what is the corresponding MIPS assembly code? Assume that the variables f, g, h, i, and j are assigned to registers $s0, $s1, $s2, $s3, and $s4, respectively. Assume that the base address of the arrays A and B are in registers $s6 and $s7, respectively. Assume that the elements of the arrays A and B are 8-byte words: f = (g+i+2) + (h − 8); B[8] = A[i-9] + A[j+8] + 7;For the following C statement, what is the corresponding MIPS assembly code? Assume that the variables f, g, h, i, and j are assigned to registers $s0, $s1, $s2, $s3, and $s4, respectively. Assume that the base address of the arrays (A and B) are in registers $s6 and $s7, respectively. Also, assume that A and B are arrays of words. B[f-j] = B[i] + A[g]This section describes memory hierarchy structures. Why did your authors choose to represent their work with a pyramid?

- Fill in blank Suppose that segmentation technique is used for memory management. If the memory addresses are 7-bit binary numbers where the first two bits are used to specify segment ID, then the size of a user stack will be ---------- bytes.Please look at the entire text below. Please solve and show all work. Thank you. What is the corresponding MIPS assembly code for the following C statement? Assume that the variables f, g, h, i, and j are assigned to register $s0, $s1, $s2, $s3, and $s4, respectively. Assume that the base address of the arrays A and B are in registers $s6 and $s7, respectively. B[8] = A[i−j] Translate the following C code to MIPS. Assume that the variables f, g, h, i, and j are assigned to register $s0, $s1, $s2, $s3, and $s4, respectively. Assume that the base address of the arrays A and B are in registers $s6 and $s7, respectively. Assume that the elements of the arrays A and B are 8-byte words: B[8] = A[i] + A[j] Assume that registers $s0 and $s1 hold the values 0x80000000 and 0xD0000000, respectively. What is the value of $t0 for the following assembly code? add $t0, $s0, $s1 Is the result in $t0 the desired result, or has there been an overflow? For the contents of registers $s0 and $s1 as…A(n) __________ is a storage location implemented in the CPU.

- 01 : (a) Write an assembly language program for the Intel 8086 microprocessor that adds two 16-bit words in the memory locations called ADD1 and ADD2, respectively, and stores the result in a memory location SUM? In the assembly language program, make sure to properly define the different segments using the appropriate assembler directives. (b) Draw a diagram showing the data arrangement in memory for the multiply program you wrote in section (a)?Computer organization and assembly language Please help me with this. I have to write line by line what each line of codes does. CODE IS BELOW: .model small .386 .stack 100h .data msg1 db 13, 10, "Enter any number --> ", "$" msg2 db "Enter an operation +,- * or / --> ",13, 10, "$" msg3 db "The Operation is --> ", "$" msg4 db "The result is --> ", "$" By_base dd 21 by_10 dd 10 ; 32 bits variable with initial value = 10 sp_counter db 0 ; 8 bits variable with initial value of zero disp_number dd 0 ; 32 bits variable with initial value = 0 disp_number2 dd 0 disp_number3 dd 0 op_type db 0 last_key dd 0 ; 32 bits variable with initial value of zero remainder db 0 .code main proc mov ax,@data;set up datasegment movds,ax mov dx,offset msg1 call display_message callm_keyin calloperation mov dx,offset msg1 calldisplay_message callm_keyin cmpop_type, "+" jnz short skip_plus callop_plus skiP_plus: cmp op_type, "-" jnz short skip_minus callop_minus…3. For the following C statement, write the corresponding MIPS assembly code. Assume that the variables f, g, h, i, and j are assigned to registers $s0, $s1, $s2, $s3, and $s4, respectively. Assume that the base address of the arrays A and B are in registers $s6 and $s7, respectively. B[i-j] = A[8]; 4.Translate the following C code to MIPS. Assume that the variables, f,g. h, i, and j are assigned to registers $s0, $s1, $s2, $s3, $s4, and $s4, respectively. Assume that the base address of A and B are in registers $s6 and $s7, respectively. Assume that the elements of the arrays A and B are 8-byte words: B[8] = A[i] + A[j]; 5.For the MIPS assembly instructions below, what is the corresponding C statement? Assume that the variables f, g, h, i, and j are assigned to registers $s0, $s1, $s2, $s3, and $s4, respectively. Assume that the base address of the arrays A and B are in registers $s6 and $s7, respectively. You must add line comments to ALL uncommented 4 lines. sll $t0, $s0, 2 #…