PC Read address Add Instruction Instruction memory Read register 1 Read register 2 Registers Read data 2 Write register Write data RegWrite Read data 1 16 Sign- extend 32 Shift left 2 ALUSrc E3X Add ALU result ALU operation Zero ALU ALU PCSrc result Address MemWrite MemRead Read data Write Data data memory MemtoReg MUX

PC Read address Add Instruction Instruction memory Read register 1 Read register 2 Registers Read data 2 Write register Write data RegWrite Read data 1 16 Sign- extend 32 Shift left 2 ALUSrc E3X Add ALU result ALU operation Zero ALU ALU PCSrc result Address MemWrite MemRead Read data Write Data data memory MemtoReg MUX

Oh no! Our experts couldn't answer your question.

Don't worry! We won't leave you hanging. Plus, we're giving you back one question for the inconvenience.

Submit your question and receive a step-by-step explanation from our experts in as fast as 30 minutes.

You have no more questions left.

Message from our expert:

Our experts are unable to provide you with a solution at this time. Try rewording your question, and make sure to submit one question at a time. We've credited a question to your account.

Your Question:

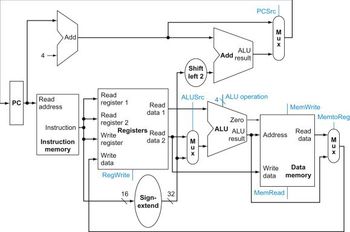

Assume that individual stages of the datapath have the following latencies:

- IF: 250ps

- ID: 350ps

- EX: 150ps

- MEM: 300ps

- WB: 200ps

-

- List the required stages for each of the following types of instructions: load, store, r-type, branch.

- What is the execution time of each type of instruction assuming only the required stages execute for each instruction?

- Assuming the same instruction mix listed in Problem 7, what is the average execution time across all instructions?

- Assuming pipelining is used, what would be the necessary clock cycle time?

- Assuming pipelining is used, what would be the execution time for a single load instruction to execute?

- Use the average instruction execution time calculated in Part d of this problem to determine the overall speed-up gained by pipelining. Assume the processor continuously runs with a full pipeline and hazards are completely avoided.

Transcribed Image Text:PC

Read

address

Add

Instruction

Instruction

memory

Read

register 1

Read

register 2

Registers Read

data 2

Write

register

Write

data

RegWrite

Read

data 1

16

Sign-

extend

32

Shift

left 2

ALUSrc

E3X

Add

ALU

result

ALU operation

Zero

ALU ALU

PCSrc

result

Address

MemWrite

MemRead

Read

data

Write Data

data

memory

MemtoReg

MUX

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Database System Concepts

Computer Science

ISBN:

9780078022159

Author:

Abraham Silberschatz Professor, Henry F. Korth, S. Sudarshan

Publisher:

McGraw-Hill Education

Starting Out with Python (4th Edition)

Computer Science

ISBN:

9780134444321

Author:

Tony Gaddis

Publisher:

PEARSON

Digital Fundamentals (11th Edition)

Computer Science

ISBN:

9780132737968

Author:

Thomas L. Floyd

Publisher:

PEARSON

Database System Concepts

Computer Science

ISBN:

9780078022159

Author:

Abraham Silberschatz Professor, Henry F. Korth, S. Sudarshan

Publisher:

McGraw-Hill Education

Starting Out with Python (4th Edition)

Computer Science

ISBN:

9780134444321

Author:

Tony Gaddis

Publisher:

PEARSON

Digital Fundamentals (11th Edition)

Computer Science

ISBN:

9780132737968

Author:

Thomas L. Floyd

Publisher:

PEARSON

C How to Program (8th Edition)

Computer Science

ISBN:

9780133976892

Author:

Paul J. Deitel, Harvey Deitel

Publisher:

PEARSON

Database Systems: Design, Implementation, & Manag…

Computer Science

ISBN:

9781337627900

Author:

Carlos Coronel, Steven Morris

Publisher:

Cengage Learning

Programmable Logic Controllers

Computer Science

ISBN:

9780073373843

Author:

Frank D. Petruzella

Publisher:

McGraw-Hill Education