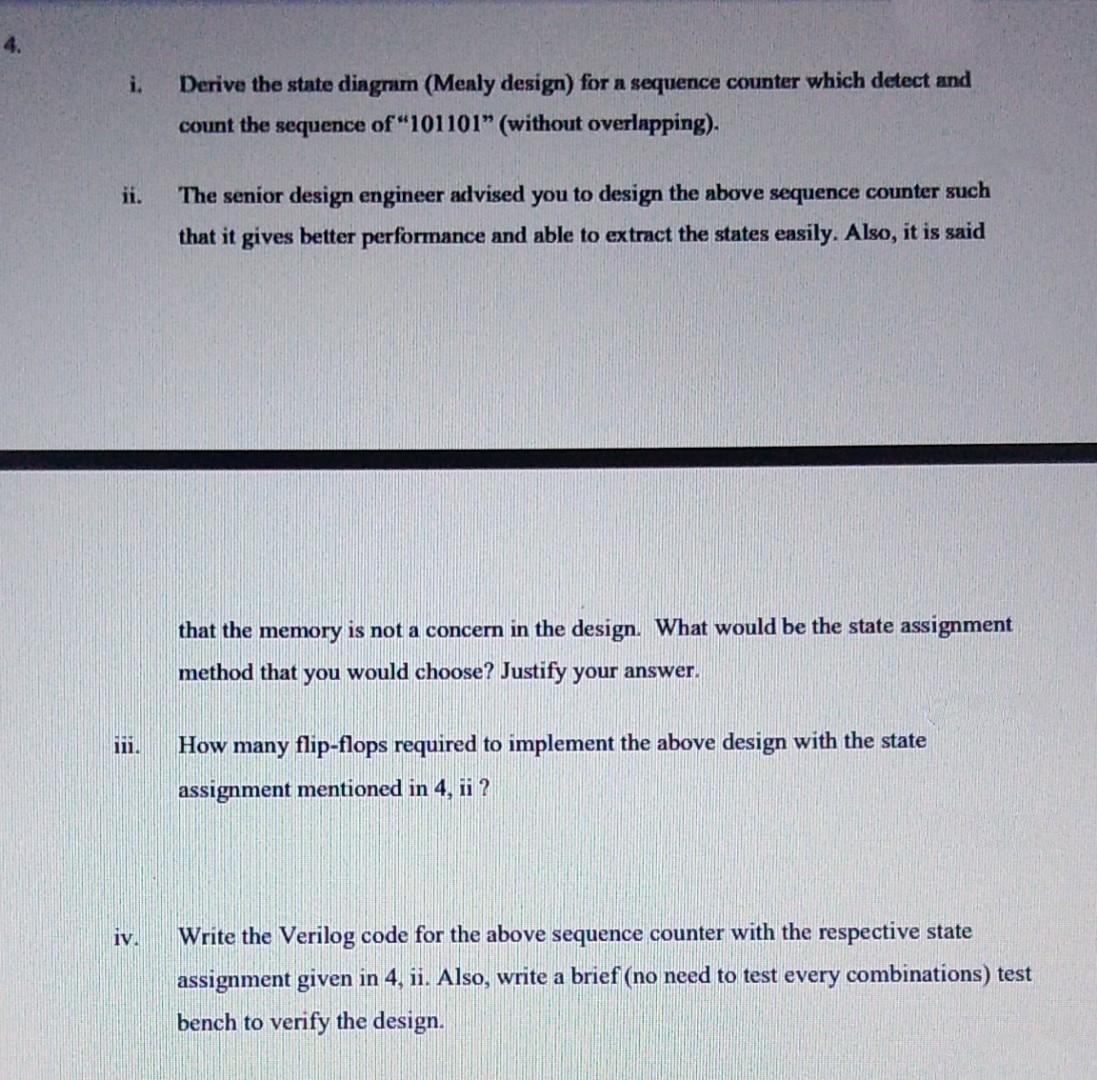

i. Derive the state diagram (Mealy design) for a sequence counter which detect and count the sequence of "101101" (without overlapping). ii. The senior design engineer advised you to design the above sequence counter such that it gives better performance and able to extract the states easily. Also, it is said that the memory is not a concern in the design. What would be the state assignment method that you would choose? Justify your answer. iii. How many flip-flops required to implement the above design with the state assignment mentioned in 4, ii ? iv. Write the Verilog code for the above sequence counter with the respective state assignment given in 4, ii. Also, write a brief (no need to test every combinations) test bench to verify the design.

i. Derive the state diagram (Mealy design) for a sequence counter which detect and count the sequence of "101101" (without overlapping). ii. The senior design engineer advised you to design the above sequence counter such that it gives better performance and able to extract the states easily. Also, it is said that the memory is not a concern in the design. What would be the state assignment method that you would choose? Justify your answer. iii. How many flip-flops required to implement the above design with the state assignment mentioned in 4, ii ? iv. Write the Verilog code for the above sequence counter with the respective state assignment given in 4, ii. Also, write a brief (no need to test every combinations) test bench to verify the design.

C++ for Engineers and Scientists

4th Edition

ISBN:9781133187844

Author:Bronson, Gary J.

Publisher:Bronson, Gary J.

Chapter2: Problem Solving Using C++using

Section2.3: Data Types

Problem 4E: (Practice) Show how the name KINGSLEY is stored in a computer that uses the ASCII code by drawing a...

Related questions

Question

Transcribed Image Text:i.

Derive the state diagram (Mealy design) for a sequence counter which detect and

count the sequence of "101101" (without overlapping).

ii.

The senior design engineer advised you to design the above sequence counter such

that it gives better performance and able to extract the states easily. Also, it is said

that the memory is not a concern in the design. What would be the state assignment

method that you would choose? Justify your answer.

iii.

How many flip-flops required to implement the above design with the state

assignment mentioned in 4, ii ?

iv.

Write the Verilog code for the above sequence counter with the respective state

assignment given in 4, ii. Also, write a brief (no need to test every combinations) test

bench to verify the design.

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 4 steps with 1 images

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

C++ for Engineers and Scientists

Computer Science

ISBN:

9781133187844

Author:

Bronson, Gary J.

Publisher:

Course Technology Ptr

C++ for Engineers and Scientists

Computer Science

ISBN:

9781133187844

Author:

Bronson, Gary J.

Publisher:

Course Technology Ptr