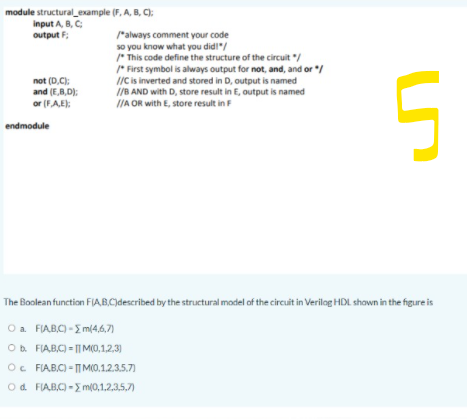

module structuraleample (, A,B, C: Input A B,C output F Palways comment your code so you know what you didi"/ * This code define the structure of the circuit "/ *First symbol is always output for not, and, and or / I/Cis inverted and stored in D, output is named IN AND with D, store result in E, output is named not (D.C: and AD): orAE IA OR with E, store result in endmodule The Booleanfunction FIARCdescribed by the structural model of the circuit in Verilog HDL shown in the feure is Oa FIABO-Em467) O FIABO- I M0,12.3) Oc FIABC) - I MIO.12.35.7) Od FIABC)-Em0,1.2357)

Protection System

A system that protects electrical systems from faults by isolating the problematic part from the remainder of the system, preventing power from being cut from healthy elements, improving system dependability and efficiency is the protection system. Protection devices are the equipment that are utilized to implement the protection system.

Predictive Maintenance System

Predictive maintenance technologies are designed to assist in determining the state of in-service equipment so that maintenance can be scheduled. Predictive maintenance is the application of information; proactive maintenance approaches examine the condition of equipment and anticipate when it should maintain. The purpose of predictive maintenance is to forecast when equipment will fail (depending on a variety of parameters), then prevent the failure through routine and corrective maintenance.Condition monitoring is the continual monitoring of machines during process conditions to maintain optimal machine use, which is necessary for predictive maintenance. There are three types of condition monitoring: online, periodic, and remote. Finally, remote condition monitoring allows the equipment observed from a small place and data supplied for analysis.

Preventive Maintenance System

To maintain the equipment and materials on a regular basis in order to maintain those running conditions and reduce unnecessary shutdowns due to unexpected equipment failure is called Preventive Maintenance (PM).

Step by step

Solved in 3 steps with 6 images