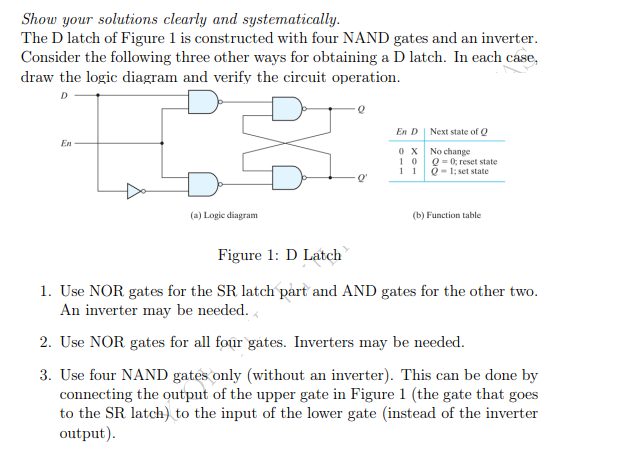

Show your solutions clearly and systematically. The D latch of Figure 1 is constructed with four NAND gates and an inverter. Consider the following three other ways for obtaining a D latch. In each case, draw the logic diagram and verify the circuit operation. 2 En D Next state of Q En 0X 10 No change Q = 0; reset state Q-1; set state 11 -Q' (a) Logic diagram (b) Function table Figure 1: D Latch 1. Use NOR gates for the SR latch part and AND gates for the other two. An inverter may be needed. 2. Use NOR gates for all four gates. Inverters may be needed. 3. Use four NAND gates only (without an inverter). This can be done by connecting the output of the upper gate in Figure 1 (the gate that goes to the SR latch) to the input of the lower gate (instead of the inverter output).

Show your solutions clearly and systematically. The D latch of Figure 1 is constructed with four NAND gates and an inverter. Consider the following three other ways for obtaining a D latch. In each case, draw the logic diagram and verify the circuit operation. 2 En D Next state of Q En 0X 10 No change Q = 0; reset state Q-1; set state 11 -Q' (a) Logic diagram (b) Function table Figure 1: D Latch 1. Use NOR gates for the SR latch part and AND gates for the other two. An inverter may be needed. 2. Use NOR gates for all four gates. Inverters may be needed. 3. Use four NAND gates only (without an inverter). This can be done by connecting the output of the upper gate in Figure 1 (the gate that goes to the SR latch) to the input of the lower gate (instead of the inverter output).

Chapter22: Sequence Control

Section: Chapter Questions

Problem 6SQ: Draw a symbol for a solid-state logic element AND.

Related questions

Question

TYPEWRITTEN ONLY PLEASE. ILL UPVOTE ONLY IF TYPEWRITTEN, COMPLETE, AND CORRECT. DONT ANSWER IF YOU ALREADY ANSWERED THIS, ILL DOWNVOTE. THANK YOU

Transcribed Image Text:Show your solutions clearly and systematically.

The D latch of Figure 1 is constructed with four NAND gates and an inverter.

Consider the following three other ways for obtaining a D latch. In each case,

draw the logic diagram and verify the circuit operation.

2

En D

Next state of Q

En

0X

10

No change

Q = 0; reset state

Q-1; set state

11

-Q'

(a) Logic diagram

(b) Function table

Figure 1: D Latch

1. Use NOR gates for the SR latch part and AND gates for the other two.

An inverter may be needed.

2. Use NOR gates for all four gates. Inverters may be needed.

3. Use four NAND gates only (without an inverter). This can be done by

connecting the output of the upper gate in Figure 1 (the gate that goes

to the SR latch) to the input of the lower gate (instead of the inverter

output).

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 4 steps with 3 images

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, electrical-engineering and related others by exploring similar questions and additional content below.Recommended textbooks for you