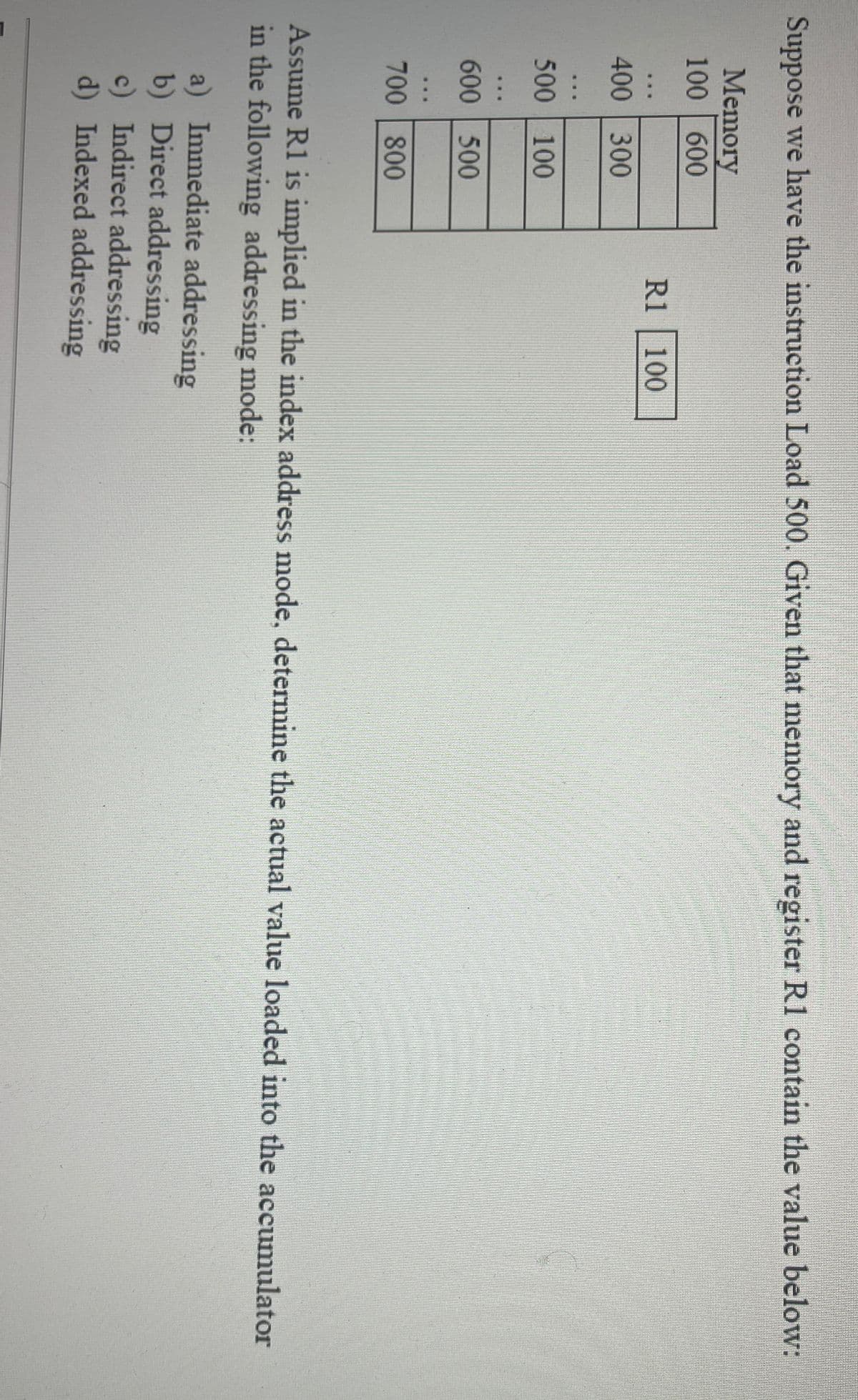

Suppose we have the instr Memory 100 600 R1| ... 400 300 ... 500 100 600 500 ... 700 800 Assume R1 is implied in t in the following addressir a) Immediate addres b) Direct addressing c) Indirect addressin d) Indexed addressin

Q: QUESTION 1 A program runs on a processor of two levels of cache. We know the following: L1 cache…

A:

Q: I need an answer to question no. 2

A: Assuming the page size to be 4KB. The calculations for physical addresses are given below: (a) VA =…

Q: 2) Assuming X22 has 7000, what address will be stored in X9 by: LDUR X9, (X22, #7] a) 7000 b) 7007…

A: According to the information given:- we have to find out the correct option on the basic of LDUR X9,…

Q: Assume that your ultra-low-cost processor doesn't have the hardware budget for an integer multiplier…

A: The instruction written here is the multiplication of two numbers but not using mul op code.

Q: Suppose a computer using direct-mapped cache has 2 bytes of byte-addressable main memory and a cache…

A: Given information: - memory address is: (0DB63)16

Q: Assume that your ultra-low-cost processor doesn't have the hardware budget for an integer multiplier…

A: Using a loop this method of multiplication is possible.

Q: For this assignment, you are to write a MIPS assembly language program using the MARS IDE and assume…

A: Answer :

Q: Given 256 GB of physical memory, a 2-way set associative cache that is 128 KB in size with a block…

A: Below is the answer to above question. I hope this will be helpful for you...

Q: Assume we have a program that resides in the memory range of 80088000-820FOF00. The numbers are in…

A: a. PAGE SIZE(in bytes) = 2^offset = 2^8 = 256Bytes b. Number of entries in 1st level page table is =…

Q: Suppose a computer using direct mapped cache has 23232 bytes of byte-addressable main memory, and a…

A: I have answered this question in step 2.

Q: b. Suppose we use two-level paging and arrange for all page tables to fit into a single page frame.…

A:

Q: For this assignment, you are to write a MIPS assembly language program using the MARS IDE and assume…

A: datavAddr: .asciiz "The address "vPage: .asciiz " is in: Page number = "vOff: .asciiz " Offset = "…

Q: Assume that your ultra-low-cost processor doesn't have the hardware budget for an integer multiplier…

A: Answer:)

Q: Suppose we have a byte-addressable computer using direct mapping with 16-bit main memory addresses…

A: Step 1:- Memory address size=16 bit Number of cache block=32 a) The number of bits of the offset…

Q: How many bits are in a physical address?

A: There are 4 pages frames of size 64 each, or 22 x 26=28. So each physical address has 8 bits.

Q: Q1: Consider a machine with a byte addressable main memory of bytes and block size of 8 bytes.…

A: Hey there, I am writing the required solution based on the above given question. Please do find the…

Q: a simple paging system with 224 bytes of physical memory, 256 pages of logical address space, and a…

A: Given : Physical memory = 224 bytes Logical address space = 256 pages Page size = 210 bytes

Q: 9- 1. Assume that 8086 Microprocessor segment registers are DS: 1000H CS: 2000H Which of the…

A: Here is the explanation about the question:

Q: 5. Suppose that a machine has 38-bit virtual addresses and 32-bit physical addresses. a) What is the…

A: A virtual address space or address space is the set of ranges of virtual addresses that an operating…

Q: Consider a virtual memory system providing 32 pages for each user program; the size of each page is…

A:

Q: For the following problems assume 1 kilobyte (KB) = 1024 bytes and1 megabyte (MB) = 1024 kilobytes.…

A: Below is the answer to abobe question. I'm providing the answr to all su

Q: 2. Suppose a computer using direct-mapped cache has 232 bytes of byte-addressable main memory and a…

A: Given: Suppose a computer using direct-mapped cache has 232 bytes of byte-addressable main memory…

Q: A certain processor uses a fully associative cache of size 16 kB, The cache block size is 16 bytes.…

A:

Q: Suppose a computer using direct mapped cache has 4MB of byte-addressable main memory, and a cache of…

A: Solution:-

Q: Q: Suppose the hypothetical processor has two I/O instructions: 0011=Load AC from I/O 0111=Store AC…

A: Given data uppose the hypothetical processor has two I/O instructions: 0011=Load AC from…

Q: Consider the main memory size of 128 kB, Cache sıze of 16 kB, Block sıze of 256 B with Byte…

A: ----------------------------------------------- | Tag | Set Number | Block…

Q: • Q7 Consider a machine with a byte addressable main memory of 216 bytes and block size of 8 bytes.…

A: AS PER OUR POLICY “Since you have posted a question with multiple sub-parts, we will solve the first…

Q: 6. Consider a logical address space of 16 pages of 2048 words each, mapped onto a physical memory of…

A: Given that, Logical address of 16 pages of 2048 words each. Number of physical memory frames= 4

Q: Consider a machine with a byte addressable main memory of 216 bytes and block size of 8 bytes.…

A: Cache memory serves as the fastest memory access in the computer architecture. Cache memory is…

Q: Suppose the Vole communicates with a printer using the technique of memory-mapped I/O. Suppose also…

A: Indecipherable symbols are replaced: By using RPLUNPRT(*YES) on the Build Printers File (CRTPRTF),…

Q: r of bits of the tag field. b. To which cache block would the hexadecimal address 0x2468 map? c.…

A: Suppose we have a byte-addressable computer using direct mapping with 16-bit main memory addresses…

Q: For the following problems assume 1 kilobyte (KB) = 1024 bytes and 1 megabyte (MB) = 1024 kilobytes.…

A: Below is the answer to above question. I hope this will be helpful for you...

Q: A computer using direct mapping cache has 256Mbytes of byte addressable main memory and cache size…

A: Size of Cache block =8 byts No of bits for Block offset = log2(8)=3 bits No of cache lines are 32K…

Q: Suppose the following code fragment is executed and that the data word that is allocated and…

A: Dear Student, addi (add immediate) will add $0 with M and will store it in $1. We also know $0…

Q: Given 256 GB of physical memory, a 2-way set associative cache that is 128 KB in size with a block…

A: Dear Student, address space = tag bits + index bits + block offset. Here we can calculate it simply…

Q: Q1\ Suppose 8086 microprocessor perform the following task: ADD AX, 3FF2H Where the value of AX is…

A: The flag register has following: Status Flag Sign (S) Parity (P) Zero (Z) Overflow (O) Auxiliary…

Q: 1. Assume that 8086 Microprocessor segment registers are DS: 1000H CS: 2000H 2- Which of the…

A: Given:

Q: Consider a machine with a byte addressable main memory of 216 bytes and block size of 8 bytes.…

A:

Q: Suppose a computer using fully associative cache has 216 bytes of byte-addressable main memory and a…

A: The given memory address is 0xF8C9. The binary form of the memory address is “1111 1000 1100 1001”…

Q: Fill in blank Suppose that linear page table is used where the memory addresses are 12-bit binary…

A: Here, we are given a linear page table with memory address and page size. Virtual address is divided…

Q: 4. Assume 32 bit memory addresses, which are byte addresses. You have a direct-mapped cache with a…

A: Block size = 8 bytes So block offset bits = 3 pieces All out # of cache blocks = 128 So index…

Q: Consider a machine with a byle addressable main memory of 2 bytes and block size of 8 bytes. Assume…

A: required:

Q: Suppose a computer using fully associative cache has 220220 words of main memory and a cache of 128…

A: solution:

Q: Assume a 32-bit address system that uses a paged virtual memory, with a page size of 2 KB, and a PTE…

A: Data given in the question, 32-bit address system page size of 2 KB PTE (Page Table Entry) size of 1…

Q: Take a look at a 64-bit logical address space. a. Assuming a page size of 4 KB Discover the truth.…

A: Introduction: the question is about Take a look at a 64-bit logical address space. a. Assuming a…

Q: the following. All numbers are decimal, everything is numbered starting from zero, and all addresses…

A: (a) The specified virtual address is V. Page number (P) = (virtual address) / (page size) Page…

Step by step

Solved in 2 steps

- Most Intel CPUs use the __________, in which each memory address is represented by two integers.If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the fetch cycle is 40% of the processor cycle time, what memory access speed is required to implement load operations with zero wait states and load operations with two wait states?Suppose we have the instruction Load 0000. Given memory and register R1 contain thevalues below:R130Memory Address Content0000 40...0010 30...0020 78...0030 55...0040 77...0050 84 Assuming R1 is implied in the indexed addressing mode, determine the actual value loaded into the accumulator using the following addressing modes: a. Immediateb. Directc. Indirectd. Indexed

- Assume that registers $s0 and $s1 hold the values 0x90000000 and 0xA0000000, respectively. These are integer values. Please take into account that these are 32-bit registers. a) What is the value of $t0 after the following MIPS instruction has been completed? add $t0, $s0, $s1 $s0: 0 x 9 0 0 0 0 0 0 0 $s1: 0 x A 0 0 0 0 0 0 06. Assume that two numbers: dividend and divisor are saved in memory address M1 and M2 respectively. Quotient and remainder should be saved in R1 and R2 respectively. Write assembly language instructions and then list microoperations for each instruction and list the control signals required to be activated for each microoperation. MBR is used as buffer for any register to register transfer operation. Signal Description: Control signals operation Comments C0 MAR to RAM (through address bus) C1 PC to MBR C2 PC to MAR C3 MBR to PC C4 MBR to IR C5 RAM to MBR C6 MBR to ALU C7 Accumulator to ALU C8 IR to MAR C9 ALU to Accumulator C10 MBR to Accumulator C11 Accumulator to MBR C12 MBR to RAM (through data bus) C13 IR to Control Unit C14 MBR to R1 C15 MBR to R2 C16 MBR to R3 C17 MBR to R4…1. Name all of the general purpose registers and some of their special functions. 2. How are the segment registers used to form a 20-bit address? 3. (a) If CS contains 03E0H and IP contains 1F20H, from what address is the next instruction fetched? (b) If SS contains 0400H and SP contains 3FFEH, where is the top of the stack located? (c) If a data segment deigns at address 24000H, what is the address of the last location in the segment? 4. Explain what the instruction array and data caches are used for. 5. What is the EU and BIU, and what purpose in the microcomputer? 6. Two memory locations, beginning at address 3000H, contain the bytes 34H and 12H. What is the word stored at location 3000H? See Figure 2.26 for details. Address 3000 Data 34 3001 12 Figure 2.26 For question 6 7. What is a physical address? What are the differences between the 8086 logical and physical memory maps? 8. May memory segments overlap? If so, what is the minimum number of overlapped bytes…

- Suppose we have the instruction Load 1000. Given memory and register R1 contain the values below: Assuming R1 is implied in the indexed addressing mode, determine the actual value loaded into the accumulator and fill in the table below:Assume the register ($s1) contains (0x12345678). Write at most two instructions to move ONLY the fourth byte value in the register ($s1) into the data memory at address stored in ($s0). Hint: In this problem, the fourth byte value in the register ($s1) = "0x12"The following diagram shows some registers like processor registers R1 and R2, Program counter PC and Index Register XR along with their corresponding values. It also shows a memory with some instructions like instruction A and next instruction. The memory holds instruction B which consists of four fields as given above. First field of instruction represents the addressing Mode (I), second field specifies Opcode (operation code) ADD representing operation addition, the third field represents Address field 1 and the fourth field represents Address field 2. Consider the following addressing modes, evaluate the result of execution of above instruction by giving steps of evaluation for each addressing mode for the scenario given above. Ø Immediate Mode Ø Direct Mode Ø Register Ø Relative Mode Ø Index Mode Choose your own values for variables (v – w), T1, T2. Choose any one of the given value for T3 (200 or 300). V=700 W=800 T1=200 T2=200 T3=300

- The following diagram shows some registers like processor registers R1 and R2, Program counter PC and Index Register XR along with their corresponding values. It also shows a memory with some instructions like instruction A and next instruction.The memory holds instruction B which consists of four fields as given above. First field of instruction represents the addressing Mode (I), second field specifies Opcode (operation code) ADD representing operation addition, the third field represents Address field 1 and the fourth field represents Address field 2. Consider the following addressing modes, evaluate the result of execution of above instruction by giving steps of evaluation for each addressing mode for the scenario given above. Immediate Mode Direct Mode Register Relative Mode Index ModeNote: Choose your own values for variables k – w, T1, T2. Choose any one of the given value for T3 (200 or 300).1) For a Pentium II descriptor that contains a base address of 0004B100H, a limit of 00FFFH, and G = 1, what starting and ending locations are addressed by this descriptor? 2) Code a descriptor that describes a memory segment that begins at location 0005CF00h and ends at location 00060EFFh. The memory segment is a data segment that grows upward in the memory system and can be written. The segment has a user level privilege (lowest) and has not been accessed. The descriptor is for an 80386 microprocessor.Consider a 16-bit processor in which the following appears in the main memory, starting at location 200.a. The first part of the first word (content at 200) indicates that this instruction loads a value into an accumulator; the value of 300 in location 201 may be part of the address calculator. The mode field specifies an addressing mode and, if appropriate, indicates a source register. a. Assume that when used, the source register R1, which has a value of 500. b. There is also a base register that contains the value 100, Assume that location 249 contains the value 399, location 250 contains the value 400, and so on. Determine the effective address and the operand to be loaded for the following address modes: