There are two common methods for implementing delays: Use external hardware that acts as a timer, typically interfaced to using interrupts which we will cover later. Write a delay loop. For this homework, you will use the latter approach. Consider the following MIPS fragment: L2: addi $t1,$ zero,N #Nis some positive immediate beg $t1, $ zero, End lw $s1,0 ($s2) sub $s1, $s1,$t1 add $s1, $s1, $ s1 sw $s1,0 ($t2) addi $t1,$t1,-1 jL2 End: lw $s1,0 ($ s1) lw $s1,0 ($ s1) w $s1,0 ($s1) You are running this on a 4GHz CPU, which requires 2 CPI for R-type arithmetic instructions, 3 CPI for immediate arithmetic instructions, 4 CPI for jumps, 5 CPI for memory instructions, and 6 CPI for branches. 1. Determine an appropriate value of N for this fragment to run in as close to 50 μs. as possible. 2. What is the largest delay possible using this code fragment (on our 32-bit MIPS)? For purposes of this problem, please assume that MIPS does not allow arithmetic overflows (even though this assumption isn't quite correct). Make sure to show your work and draw a box around your final answers.

There are two common methods for implementing delays: Use external hardware that acts as a timer, typically interfaced to using interrupts which we will cover later. Write a delay loop. For this homework, you will use the latter approach. Consider the following MIPS fragment: L2: addi $t1,$ zero,N #Nis some positive immediate beg $t1, $ zero, End lw $s1,0 ($s2) sub $s1, $s1,$t1 add $s1, $s1, $ s1 sw $s1,0 ($t2) addi $t1,$t1,-1 jL2 End: lw $s1,0 ($ s1) lw $s1,0 ($ s1) w $s1,0 ($s1) You are running this on a 4GHz CPU, which requires 2 CPI for R-type arithmetic instructions, 3 CPI for immediate arithmetic instructions, 4 CPI for jumps, 5 CPI for memory instructions, and 6 CPI for branches. 1. Determine an appropriate value of N for this fragment to run in as close to 50 μs. as possible. 2. What is the largest delay possible using this code fragment (on our 32-bit MIPS)? For purposes of this problem, please assume that MIPS does not allow arithmetic overflows (even though this assumption isn't quite correct). Make sure to show your work and draw a box around your final answers.

Computer Networking: A Top-Down Approach (7th Edition)

7th Edition

ISBN:9780133594140

Author:James Kurose, Keith Ross

Publisher:James Kurose, Keith Ross

Chapter1: Computer Networks And The Internet

Section: Chapter Questions

Problem R1RQ: What is the difference between a host and an end system? List several different types of end...

Related questions

Question

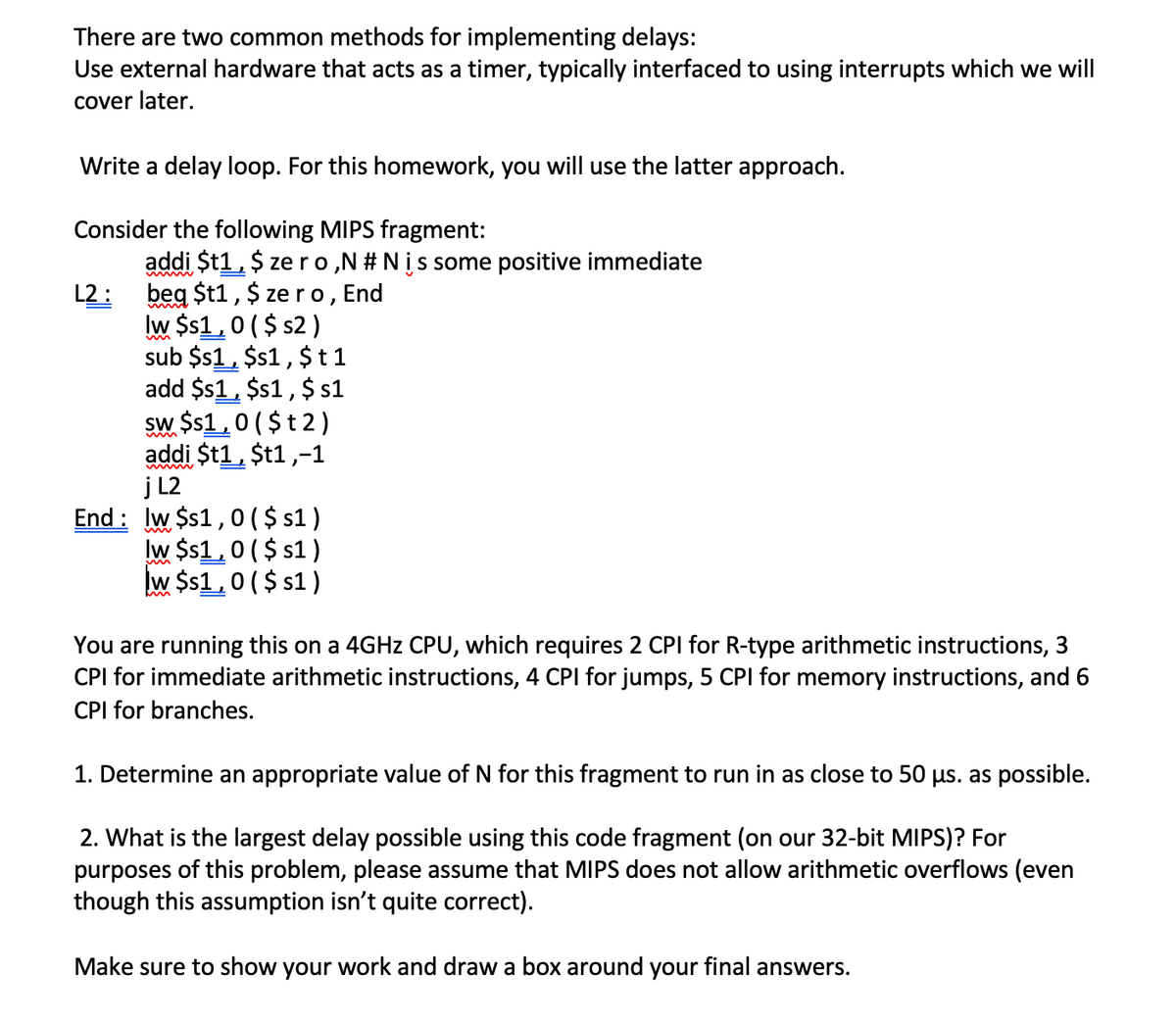

Transcribed Image Text:There are two common methods for implementing delays:

Use external hardware that acts as a timer, typically interfaced to using interrupts which we will

cover later.

Write a delay loop. For this homework, you will use the latter approach.

Consider the following MIPS fragment:

addi $t1,$ zero,N #Nis some positive immediate

beg $t1, $ zero, End

lw $s1,0 ($s2)

sub $s1, $s1, $t1

add $s1, $s1, $ s1

sw $s1,0 ($t 2)

addi $t1,$t1,-1

jL2

End lw $s1,0 ( $ s1)

lw $s1,0 ($ s1)

w $s1,0 ($s1)

L2:

You are running this on a 4GHz CPU, which requires 2 CPI for R-type arithmetic instructions, 3

CPI for immediate arithmetic instructions, 4 CPI for jumps, 5 CPI for memory instructions, and 6

CPI for branches.

1. Determine an appropriate value of N for this fragment to run in as close to 50 µs. as possible.

2. What is the largest delay possible using this code fragment (on our 32-bit MIPS)? For

purposes of this problem, please assume that MIPS does not allow arithmetic overflows (even

though this assumption isn't quite correct).

Make sure to show your work and draw a box around your final answers.

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps with 1 images

Recommended textbooks for you

Computer Networking: A Top-Down Approach (7th Edi…

Computer Engineering

ISBN:

9780133594140

Author:

James Kurose, Keith Ross

Publisher:

PEARSON

Computer Organization and Design MIPS Edition, Fi…

Computer Engineering

ISBN:

9780124077263

Author:

David A. Patterson, John L. Hennessy

Publisher:

Elsevier Science

Network+ Guide to Networks (MindTap Course List)

Computer Engineering

ISBN:

9781337569330

Author:

Jill West, Tamara Dean, Jean Andrews

Publisher:

Cengage Learning

Computer Networking: A Top-Down Approach (7th Edi…

Computer Engineering

ISBN:

9780133594140

Author:

James Kurose, Keith Ross

Publisher:

PEARSON

Computer Organization and Design MIPS Edition, Fi…

Computer Engineering

ISBN:

9780124077263

Author:

David A. Patterson, John L. Hennessy

Publisher:

Elsevier Science

Network+ Guide to Networks (MindTap Course List)

Computer Engineering

ISBN:

9781337569330

Author:

Jill West, Tamara Dean, Jean Andrews

Publisher:

Cengage Learning

Concepts of Database Management

Computer Engineering

ISBN:

9781337093422

Author:

Joy L. Starks, Philip J. Pratt, Mary Z. Last

Publisher:

Cengage Learning

Prelude to Programming

Computer Engineering

ISBN:

9780133750423

Author:

VENIT, Stewart

Publisher:

Pearson Education

Sc Business Data Communications and Networking, T…

Computer Engineering

ISBN:

9781119368830

Author:

FITZGERALD

Publisher:

WILEY