You may assume that in this assembly language, each line of source code assembles to a single one-word (32-bit) instruction

You may assume that in this assembly language, each line of source code assembles to a single one-word (32-bit) instruction

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 2PE: If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the...

Related questions

Question

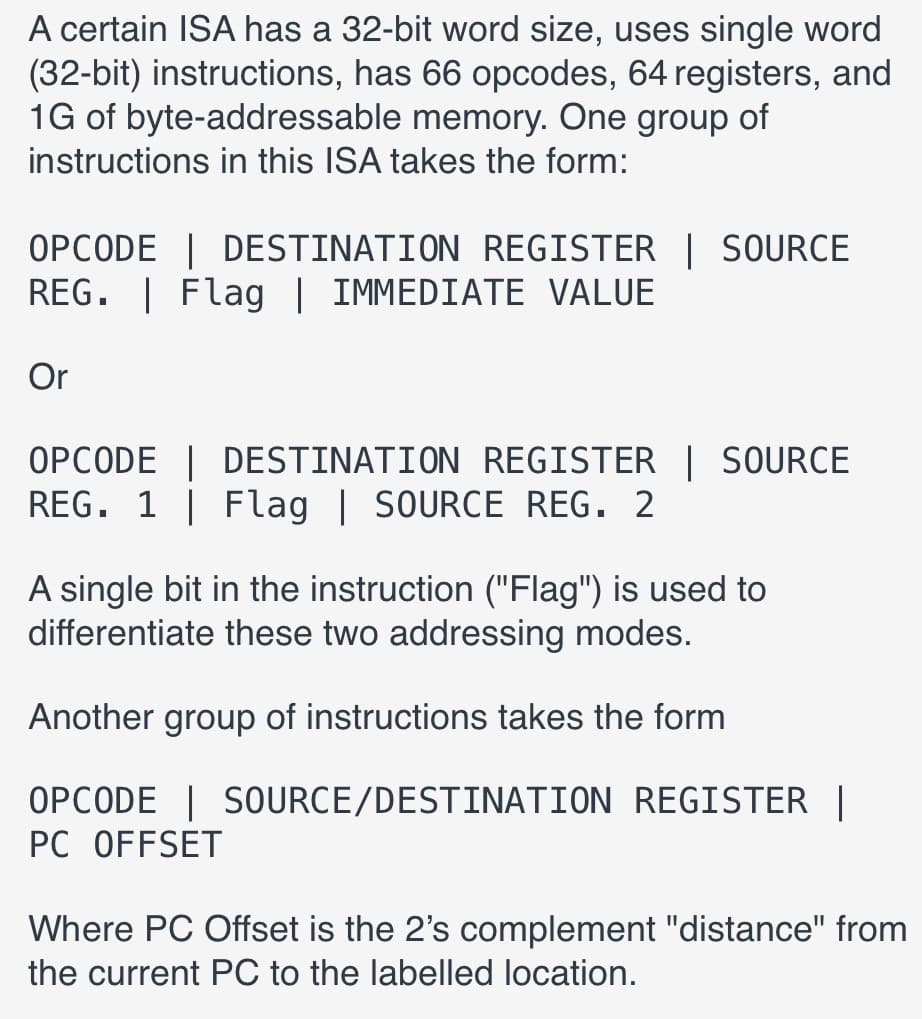

Transcribed Image Text:A certain ISA has a 32-bit word size, uses single word

(32-bit) instructions, has 66 opcodes, 64 registers, and

1G of byte-addressable memory. One group of

instructions in this ISA takes the form:

OPCODE | DESTINATION REGISTER | SOURCE

REG. | Flag | IMMEDIATE VALUE

Or

OPCODE | DESTINATION REGISTER | SOURCE

REG. 1 | Flag | SOURCE REG. 2

A single bit in the instruction ("Flag") is used to

differentiate these two addressing modes.

Another group of instructions takes the form

OPCODE | SOURCE/DESTINATION REGISTER |

PC OFFSET

Where PC Offset is the 2's complement "distance" from

the current PC to the labelled location.

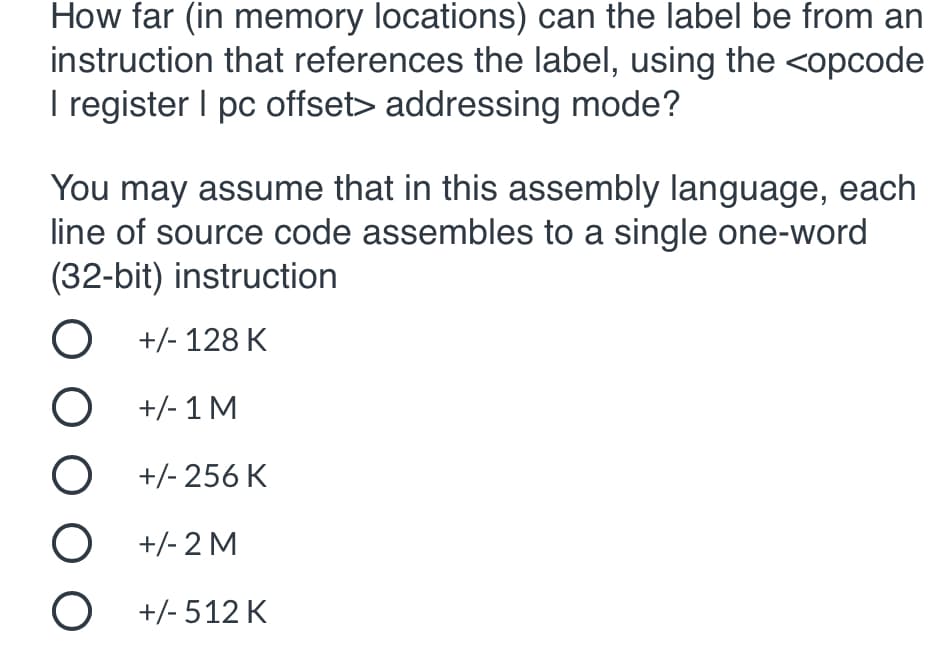

Transcribed Image Text:How far (in memory locations) can the label be from an

instruction that references the label, using the <opcode

I register I pc offset> addressing mode?

You may assume that in this assembly language, each

line of source code assembles to a single one-word

(32-bit) instruction

O +/- 128 K

O +/-1 M

+/- 256 K

O +/- 2 M

O +/- 512 K

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning