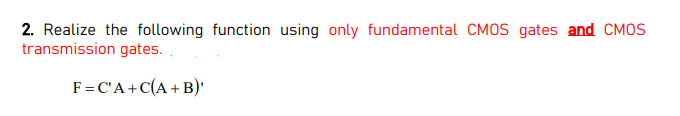

2. Realize the following function using only fundamental CMOS gates and CMOS transmission gates. F=C'A+C(A +B)'

Q: Solve this equation using CMOS technology: F = A'C' + B'D' + A'BD + BC'D + AB'C + ACD'

A: Given equation for the circuit as: According to De-Morgan's Law: Hence, we can observe that taking…

Q: Q2. Ripple Carry Adder The following is a diagram of a 1 bit Full Adder. a b ci

A: It is defined as a combinational logic circuit. It is used for the purpose of adding two n-bit…

Q: Explain with the aid of equations the following: (a) How to improve the noiseless channel capacity?…

A: a)The data rate controls the transmission speed of the data. A very important point in data…

Q: F(A, B, C, D) = Σm(4, 7, 8, 9, 13, 14, 15) Implement following function G and the function F given…

A: Objective: Given two functions F and G with 4 variables A, B, C, and D. These functions need to be…

Q: 2. Explain the function and purpose of different types of Tristate, construct 4:1 Mux using…

A:

Q: A figure of a simple 1 bit ALU with multiplexer BO AO Cout MIMO Full Adder 4:1 Mux FC Logical Unit…

A: Part A: According to diagram we can see that we required AND Gate -1 OR Gate -1 with Not gate…

Q: What are the status of the following CMOS gates when both inputs A and B are 0s? Answer choices:

A: Below the solution

Q: Draw a block diagram of Data Bus Transceiver Circuit

A: - The question asks about the block diagram of the Data Bus Transceiver Circuit. - This circuit is…

Q: DESIGN A 4X16 DECODER CIRCUIT USING 74138( 3X8 DECODER) IN ORDER TO SATISFY THE FUNCTION F(A,B,C,D)=…

A:

Q: In a scheme, all the signal levels are on one side of the time axis, either above or below. Unipolar…

A: Explanation:- In a unipolar scheme, all the signal levels are on one side of the time axis, either…

Q: Calculate the logical effort and parasitic delay of a one-bit ripple-carry cell adder

A: A ripple carry adder is a logic circuit in which the complete of each full adder is the convey in of…

Q: Question 3 a) In your own words, explain what CMOS means, give an example of a CMOS logic gate and…

A: The solution to the given question is: a) CMOS (Complementary Metal-Oxide Semiconductor) It is the…

Q: ) Draw a D Flip-Flop circuit constructed in a Master/Slave configuration, using Transmission Gate…

A: Master-slave is a combination of two flip-flops connected in series, where one acts as a master and…

Q: Design a CMOS transistor circuit that has 2 inputs, A and B, and produces a high output if and only…

A: The term CMOS stands for Complementary Metal Oxide Semiconductor. CMOS consists of P-channel MOS…

Q: According to the data-sheet of M74HC00 IC, ICC=50mA,tpLH=7ns, tpHL=15ns, VOH=5.9v, VOL=0.1,…

A:

Q: How many MOSFET is needed to implement the following function with a single CMOS gate (Z=Â+BCD):

A: MOSFET stands for Metal Oxide Semiconductor Field Effect Transistor. It is a four-terminal device…

Q: Q2) Consider three-stage space-division switch with N=500, n= 50, k=5. 3. What is the maximum number…

A: In this problem first we need to calculate the crossbars at the middle stage.

Q: Using truth table numbers. Show the comparators with proper connections. 4. Design equation…

A: In this question, we will first create a truth tables using 4×1 MUX and then design a circuit…

Q: 1. The overall channel matrix and draw the resultant channel diagram. 2. P(Z₁) and P(Z2) if…

A:

Q: Find Bode plot for the transfer function 2500 (10t s) h (s) = $(2+5) (s*+305+ 21500) and Find (G mi…

A: Dear learner , hope you are doing well , I will try my best to answer this question. Thank You !!

Q: 2- According to the FPGA's cells studied, how many FPGA cells are required to implement an 8 bit…

A: Given: According to the FPGA's cells studied, how many FPGA cells are required to implement an 8-…

Q: 3. Assume that data rate for each input connection in figure above is 6 kbps. Find the new durations…

A: 3. Given data: Data rate for each input connection =6kbps To find: a. Duration for each input slot…

Q: For the given circuit, what will be the value stored in 6T SRAM cell WL =1 VD VDD BL BL

A: The presentation of the planned FinFET primarily based 6T SRAM cell has been assessed for its…

Q: Q2) Consider three-stage space-division switch with N=500, n= 50, k=5. 5. What is the limitation of…

A: In three-stage space-division design, the limitation of this design is its small number of racks. To…

Q: 1.You are synthesizing a chip composed of some logic with an average activity factor of 0.1. You are…

A: answer is

Q: The following switching functions are to be implemented using a decoder. The minimum configuration…

A: The Answer is in below Steps

Q: Circuits implemented using FPGA compared to the same circuits implemented using ASIC are difficult…

A: The correct Answer for the above question is "True" Explanation: ASIC stands for…

Q: 7. Design a self-bias network using a JFET transistor with Ipss=8 mA and Vp -6 V to have a Q-point…

A: The complete explanation is given below.

Q: Question 4: for the timing diagram below, synthesize the function f (x1, x3, x3) in the simplest SOP…

A: Function f(x1,x2,x3) in the simplest sum-of-products form.

Q: Q3: Assume you have a main CLK with frequency of 16KHZ, design a frequency divider circuit that…

A: A frequency divider can be constructed from jk flip flops by taking the output of one cell to the…

Q: Draw the following functions using NAND gates only: a. F(A,B,C)=A'B+A'BC'+A'C b. F(A,B,C,D)=(A'B'CD'…

A: Answer :

Q: QUESTION 1 Using 74LS163 4-bit binary counter and any necessary gates, design a counter that…

A:

Q: Bipolar junction transistors (BJTs) are considered “normally-off” devices, because their natural…

A: Given that Bipolar junction transistors (BJTs) are considered “normally-off” devices, because their…

Q: 2) Explain how the XOR gates and the M bit are being used in the 4-bit adder-subtractor to perform…

A: Explain how the XOR gate and the M bit are being used in the 4-bit adder-subtractor to perform…

Q: The term that is used as an alternative to None Return to Zero (NRZ) is a. Polar b. Unipolar c.…

A: Question The term that is used as an alternative to None Return to Zero (NRZ) is a. Polar b.…

Q: EvenIN ony CoursS GAIS COIse The following expressions of X and Y are to be built using an active…

A: Decoder is nothing but a circuit that changes the code into a signals. It is opposite of encoding.

Q: Multiply unsigned numbers 110011 and 101010 using: a) carry save adders b) serial multiplier with…

A: Below i have answered:

Q: Design a circuit diagram for the following comparator system that takes three 3-bit binary numbers…

A: First you need to see that what is the 3-bit comparator A comparator that thinks about two parallel…

Q: 1. Draw AM modulator Block Diagram 2. Draw all the signals 3. Write the equation for Modulating…

A: Answer:-

Q: The main advantage of ECL over TTL or CMOS is(a) ECL is less expensive(b) ECL consumes less power(c)…

A: The advantages of ECL (Emitter Coupled Logic) gates are as follows: ->Here in the ECL a multiple…

Q: Design a signed n-bit multiplier.

A: Design a signed n-bit multiplier.

Q: To build CMOS circuit we need 2 rules Select one or more: O a. only use NFETS in pullup circuits b.…

A: answers: option b and d are correct This is a method used to develop integrated circuits also CMOS…

Q: Explain the difference between the two BJTS NPN Transistor PNP Transistor Jcollector c JCollector…

A: the difference is an given below :

Q: 3. Convert the following non-standard SOP to standard SOP A + B[AC +(B + C)D]: + CA

A: Steps to Convert the Non Standard to Standard SOP

Q: Calculate the reverse current of P-N diode, if a forward current of 10mA is flowing through it if…

A: Hey there, I am writing the required solution based on the above given question. Please do find the…

Q: If the CLK is operated at 5MHZ, one bus cycle complete in 800 ns O 80 ns O 800 s O

A: 1. If the CLK is operated at 5MHZ, one bus cycle is completed in Answer: 800 ns

Q: 4. The block diagram of two transfer functions G,(s) and G,(s) represented in the figure bellow U…

A: Solution is:

Step by step

Solved in 2 steps with 1 images

- Build the following function using only 8x1 Mux: F(a,b,c,d,e) = ∑ (0, 4, 8, 16, 17, 20, 22, 24, 25, 31) [NB: Must show MSB & LSB] [NB: The circuit should be cost efficient. Meaning, try to use lowest number of ICs possible for an optimum design]Construct a 4x16 decoder using a maximum of four (4) 2x4 decoders. You may use external gates and other combinational logic circuits (e.g. multiplexers, adder, etc.). You may use block diagram for decoders. Label your I/O pins properly and completelyUsing suitable circuit diagrams, implement the following logic equations using CMOS i. f(xy) = overline (x + y) ii. f(xy) =( x -y) iii. f(x.y,z)=( overline x.y.z )

- Implement the following Boolean function by using NAND gates only.F(A,B,C,D) = ∑ (1,3,4,8,10,11,13,14)مصطفى قاسم الخالدي: can xor gates used as a universal gates and can xnor gates used as a universal gates ?Implement the following circuits only using NAND gates. Use the method of your choice (pushing bubbles, De Morgan's, etc.) a. f(A,B)=(A′+B′)

- Draw the logic circuit of the full adder circuit block. the circuit that will perform the operation given below. Implement using a minimum number of full adder circuit blocks and a minimum number of logic gates. Here a1a0, b1b0 and c1c0 are two-bit binary numbers.Simplify the following functions and implement them with two-level NAND gate circuits: 1. F(A,B,C,D) = AC'D' + A'C + ABC + AB'C + A'C'D'4) Simplify the following functionF (A,B,C,D) = ∏ M (2,10,13) in 4.a) SOP form and implement it with only NAND gates. 4.b) POS form and implement it with only NOR gates