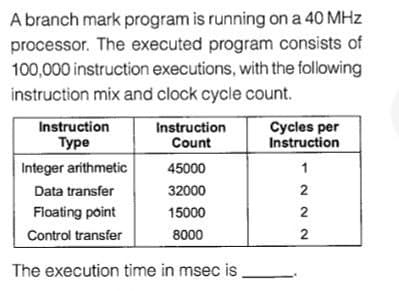

cessor. The ex 000 instruction ruction mix and

Q: The content of register A is 10 and content of register c is 40. The esult for instruction MOV A, C…

A: The content of register A is 10 and content of register c is 40. The result for instruction MOV A, C…

Q: 1. Explain what happens when the instruction sequence below is executed. LAHF MOV [BX+DI], AH

A: 1. LAHF : Copies flag register's lower byte into AH register MOV[BX+DI],AH : This will move the…

Q: Derive the micro-operations and respective control signals in the same fashion as Table for the…

A: Actually, MAR is Memory Address Register. Registers are used to stores the small amount of data.

Q: MOV DS.(202) MOV SI,[200] THESES SEQUENCE OF INSTRUCTIONS ARE EQUAL TO ONE INSTRUCTION WHICH IS…

A: Answer is in next step

Q: Given a memory load instruction, "mov R0; [R1+1000]," please give the input that should be selected…

A: Given instruction: mov R0 , [R1 + 1000] , store content of (R1 +1000) to register R0 [R1 +…

Q: ans the address of the next instruction pair to be fetched from memory. Select one: O True O False

A: A program counter is a register that contains the address of the instruction being executed at the…

Q: Explain the distinction between the written sequence and the time sequence of an instruction.

A:

Q: The instruction -> Add LOCA,R0 does

A: 1) Here is how this assembly level instruction is executed First the instruction is fetched from…

Q: Fill in the blanks: Q. Instruction __________________ Architecture is Better known as…

A: Given question wants us to fill out the architecture based blanks.

Q: Given the machine code, identify the instruction line or command line. Use CAPITAL LETTERS . No…

A: SUMMARY: -Hence, we discussed all the points.

Q: The content of AC after the end of * :execution for the next instruction is 620 700 O 320 None of…

A: Lets see the solution in the next steps

Q: Draw the datapath for store instruction. Give clear explanation too.

A: Solution: The datapath for the store instruction. New pc value is computed instruction is read two…

Q: 1. Explain what happens when the instruction sequence below is executed. LAHF MOV [BX+DI] , AH

A: Solution: LAHF : copies flag register's lower computer memory unit into AH registerMOV[BX+DI],AH :…

Q: Computer Science Q4) write program segment to find number of ones in register BL

A: The Assembly program is implemented below:

Q: Multiple choice please answer this The following operations (instruction) function with signed…

A: Find the answer with explanation given as below :

Q: XCHG [CS],[BX] is a valid instruction. Select one: O True O False

A: XCHG instruction is used to exchange the values on register pairs HL and DE

Q: de the Cortex-M3 16 bit instruction. Your answer should be written in four hex digits: LDR R3, [pc,…

A: The Cortex-M3 32-bit RISC ARM processor is designed as high-speed, low-cost, low power consumption…

Q: The CMP R/M is one of the 8085 instruction sets which compares register or memory content with…

A: X(Not used) - It is not used bit irrespective of the operation. CMP instruction is the compare…

Q: Please write an discussion and conclusion for lab report about easy68k the move instruction in…

A: The 68K is a CPU made by Motorola. Its perhaps the best microprocessor is as yet being used today.…

Q: DEC instruction can decrement DS Register. Select one: O True O False

A: According to the information given:- We have to verify the mentioned statement is true or not

Q: The content of IR after the end of execution :for the next instruction is

A: Correct answer is 4620

Q: Provide examples of three different instruction mnemonics

A: Instruction mnemonic: The instruction mnemonics are the reserved words which define an operation to…

Q: MOV DS,[202] MOV SI,[200] THESES SEQUENCE OF INSTRUCTIONS ARE EQUAL TO ONE INSTRUCTION WHICH IS…

A: We need to find equivalent instruction for MOV DS, [202] MOV SI, [200].

Q: Select an instruction that tests bit position 8 of register CH. Select the correct response: None of…

A: The CH-lower and higher halves 16-bit data register and can be used as 8-bit data register.

Q: BX=FFFF, after instruction INC BX is executed, CF

A: Increment and decrement operations doesn't affect carry flag It affects zero flag

Q: Determine the value after the instruction (signed division). AX = 0020H DL = FCH IDIV DL Select…

A: Option D is correct .i.e FFF8H

Q: MOV DS,(202) MOV SI,[200] THESES SEQUENCE OF INSTRUCTIONS ARE EQUAL TO ONE INSTRUCTION WHICH IS…

A: Let us see the answer below.

Q: Subject Name: Microcomputer application principle Questioon: Write the appropriate or instruction…

A: AX is the register with both AH and AL so reset 5th and 7th bits in this register.

Q: 7. The instruction, CMP to compare source and destination operands it performs a) addition b)…

A: 7. The instruction, CMP to compare source and destination operands it performsa) additionb)…

Q: XCHG (BX],[DS] is a valid instruction. Select one: O True O False

A: XCHG is a instruction that is used to exchange the contents of 2 registers or 2 memory locations.

Q: 5) Rebuild the instructions a- INC CX b- SUB Al,02H c- SUB AX,DX

A: a)INC CX is mainly used as increment counter in loops INC: Increment: This instruction increments…

Q: What will the instruction given below do? MOV A, #55H

A: This instruction will load 55H into A

Q: Evaluate the effect of the instruction LDR r5, [r7, #4], given the initial values below. Give the…

A: The answer and the explanation is given below:

Q: (g) Explain the similarities and differences between the two instructions below in detail. PDOR =…

A: Consider the given instruction PDOR = PDOR & 0x000000FF; PCOR = 0x000000FF;

Q: Computer Fundamentals In the instruction ADD A, B, the answer gets stored in ___________ A B B A C…

A: Here The Instruction says ADD A,B means Add B to A and Store it To A.

Q: The content of AC after the end of :execution for the next instruction is 700 O 620 O 320 O None of…

A: The solution to the given problem is below.

Q: Determine the value after the instruction (signed division). AX = 0020H DL = FCH IDIV DL Select the…

A: Divides the signed dividend by using a signed divisor. Leftmost bit represents the sign (0 means…

Q: 6. List the register transfers of following instruction: (a) ADDI (b) LOAD (c) ADD (d) BEQ

A: a) ADDI Instruction The ADDI instruction performs an addition on both the source register's…

Q: 20% of all instructions are arithr 40% are load,

A: CPI (Cycles Per Instructions) is the number of cycles or clock ticks that an instruction requires to…

Q: CF Match the above pictures with the rotate instruction operations depicted. 1 [Choose ] [Choose ] 2…

A: Dear Student, ROR : This command means Rotate Right without the carry flag. Depending on the count…

Q: ASSEMBLY The JAE instruction jumps if the (unsigned) first operand is greater than or equal to the…

A: Given data is shown below: The JAE instruction jumps if the (unsigned) first operand is greater than…

Q: MOV AL, [BX) is a invalid instruction. Select one: True False

A: Question True/False MOV AL,[BX] is a invalid instruction.

Q: What is wrong with a MOV [BX],[DI] instruction?

A: MOV [BX], [DI] [BX] - Content at the address held by BX [DI] - Content at the address held by…

Q: Define restartable instruction.

A: Restartable instruction Restartable instruction is an instruction in CPU if it causes an exception.…

Q: Write one advantage each of memory-mapped I/O and instruction based I/O.

A: Let us see the details of advantage each of memory-mapped I/O and instruction based I/O.

Q: What is the oppcode, dw, mod, reg, r/m, and displacement for the instruction 8B1E1234

A: We need to answer: What is the oppcode, dw, mod, reg, r/m, and displacement for the instruction…

Q: Execution of instruction is controlled by memory unit 1-true 2-false

A: EXPLANATION: The Memory Unit is also referred to as the Storage unit, main memory, RAM. The…

Q: MOV BX, 649Bh ВХ, ЗАҺ OR The value for BX after OR instruction executes is 65BBH.

A: Summary: - Hence we discussed all the point

Q: (c) Develop an emulated instruction CLRZ using a bit manipulation core instruction.

A: The Texas Instruments (Tl) MSP430 family of processors are low power 16 bit devices. They are…

Step by step

Solved in 2 steps with 2 images

- Processor R is a 64-bit RISC processor with a 2 GHz clock rate. The average instruction requires one cycle to complete, assuming zero wait state memory accesses. Processor C is a CISC processor with a 1.8 GHz clock rate. The average simple instruction requires one cycle to complete, assuming zero wait state memory accesses. The average complex instruction requires two cycles to complete, assuming zero wait state memory accesses. Processor R can’t directly implement the complex processing instructions of Processor C. Executing an equivalent set of simple instructions requires an average of three cycles to complete, assuming zero wait state memory accesses. Program S contains nothing but simple instructions. Program C executes 70% simple instructions and 30% complex instructions. Which processor will execute program S more quickly? Which processor will execute program C more quickly? At what percentage of complex instructions will the performance of the two processors be equal?A(n) ________________ instruction always alters the instruction execution sequence. A(n) ______________ instruction alters the instruction execution sequence only if a specified Condition is true.Will upvote! Find the memory address of the next instruction executed by the microprocessor, when operated in the real mode, for the following CS:IP and 80286 register combinations: a. DS=2F2E & DX=9D64 b. CS=9F7A & IP=AB27 c. ES=DE21 & DI=D75F d. SS=FF5C & BP=92B8 e. DS=DC67 & CX=2FE8

- Question: Suppose a program of 600 instructions runs on a 2 GHz processor. The frequency of instructions and the clock cycle counts per instruction are given as follows. What is the average CPI of this instruction mix? Operation Frequency Clock Cycles ALU operations 55% 1 Loads/Stores 30% 2 Branches 15% 3 Question: Continue from the previous question. What is the CPU time of the program in nanoseconds? Question: Suppose a processor P has a 2.5 GHz clock rate and a CPI of 1.5. If the processor executes a program in 3 microseconds, find the number of instructions in the program.On a uniprocessor, portion A of program P consumes 24 seconds, while portion B consumes 822 seconds. On a parallel computer, moderately serial portion A speeds up 4 times, while perfectly parallel portion B speeds up by the number of processors. 1- What is the speedup of program P on 1,024 processors? _______ times 2- How many processors are required to achieve at least half the theoretical maximum possible speedup on P?Consider the following portions of three different programs running at the same time on three processors in a symmetric multicore processor (SMP). Assume that before this code is run, Total is 15, val_1 is 45, val_2 is 25, and val_3 is 5. Core 1: Total = Total + val_1;Core 2: Total = Total - val_2;Core 3: Total = Total + val_3; 1. Show the assembly code for both instructions. Assume that Total, var_1, and var_2 are stored at 0x0100, 0x0120, and 0x0130 respectively.2. What are all the possible resulting values of Total? For each possibleoutcome, explain how we might arrive at those values. You will need to show all possible interleavings of instructions.3. How could you make the execution more deterministic so that only one set of values is possible?

- On an ARM processor, assuming that [N-bit] = 0, [Z-bit] = 0, [C-bit] = 1, [V-bit] = 1, predict whether each of the following branch instruction is going to make the flow of control branch to the instruction labeled by NEXT (i.e., YES or NO). (These instructions are NOT executed one after the other one; instead, each instruction starts with the initial conditions given in the statement.) (a) BLS NEXT (b) BNE NEXT (c) BLE NEXT (d) BVC NEXTThe runtimes of the five stages of executing an instruction in a non-pipelined machine are listed below. Instruction Fetch 100ps Instruction Decode 200ps ALU 300ps Memory 300ps Write Back 200ps This is then converted into a pipelined machine M1 using the most critical stage as the cycle time. For a new machine M2, we are allowed to break up exactly one stage into two substages of equal times giving us a six stage pipeline. A1: Discuss in short clear sentences the latency differences between the machines M1 and M2. A2: Discuss in short clear sentences the throughput differences between the machines M1 and M2.Suppose you have a computer that does instruction processing in anatomic way, with a clock cycle of 7ns and one instruction executioncompleted every cycle.You now split the processing into the five stages of the RISC pipeline,and you get required processing times of• IF: 1ns• ID: 1.5ns• EX: 1ns• MEM: 2ns• WB: 1.5nsYou now have added 0.1ns of delay between each of these stages. What’s the clock cycle time of this 5-stage pipelined machine?

- In the MIPS micro-architecture, the PC is incremented for each instruction, during the "Instruction Fetch" stage. The value of the PC may also be updated later within the "Memory Access" phase. * If the value of the PC is: 0x0000 2F1C, what is the value of the PC after you complete the execution of the instruction: ``addi $t0, $s0, $ra``?* <!-- response -->Assume a 3GHz processor executes three classes of instructions(A, B, C).i. Calculate the average CPI for this sequence of program.ii. Calculate the execution time for this sequence of program.iii. If we use a system with four same processors, there will bespeed up by a factor of 4 for classes A and C, but class B willremain unaffected. Calculate the new execution time for thissystem. What is the overall speed up? Class A B C CPI for class 4 2 10 IC in sequence 100 200 300Consider a fairly standard 5-stage pipeline: Fetch; Decode; Execute; Memory; Writeback. Let the processor be a nice, simple RISC single-cycle machine. The instructions below are executed. The branch should be taken — however, this processor does no prediction and always assumes a fall-through. Draw a Gantt chart for this and determine the branch penalty. SUB R1, R1, #1 BEQ R1, R0, LoopDone LOAD R2, Memory(100) SUB R3, R2, R1 MUL R3, R3, R3 LOAD R4, Memory(200) ADD R5, R4, R3 STORE R5, Memory(204)