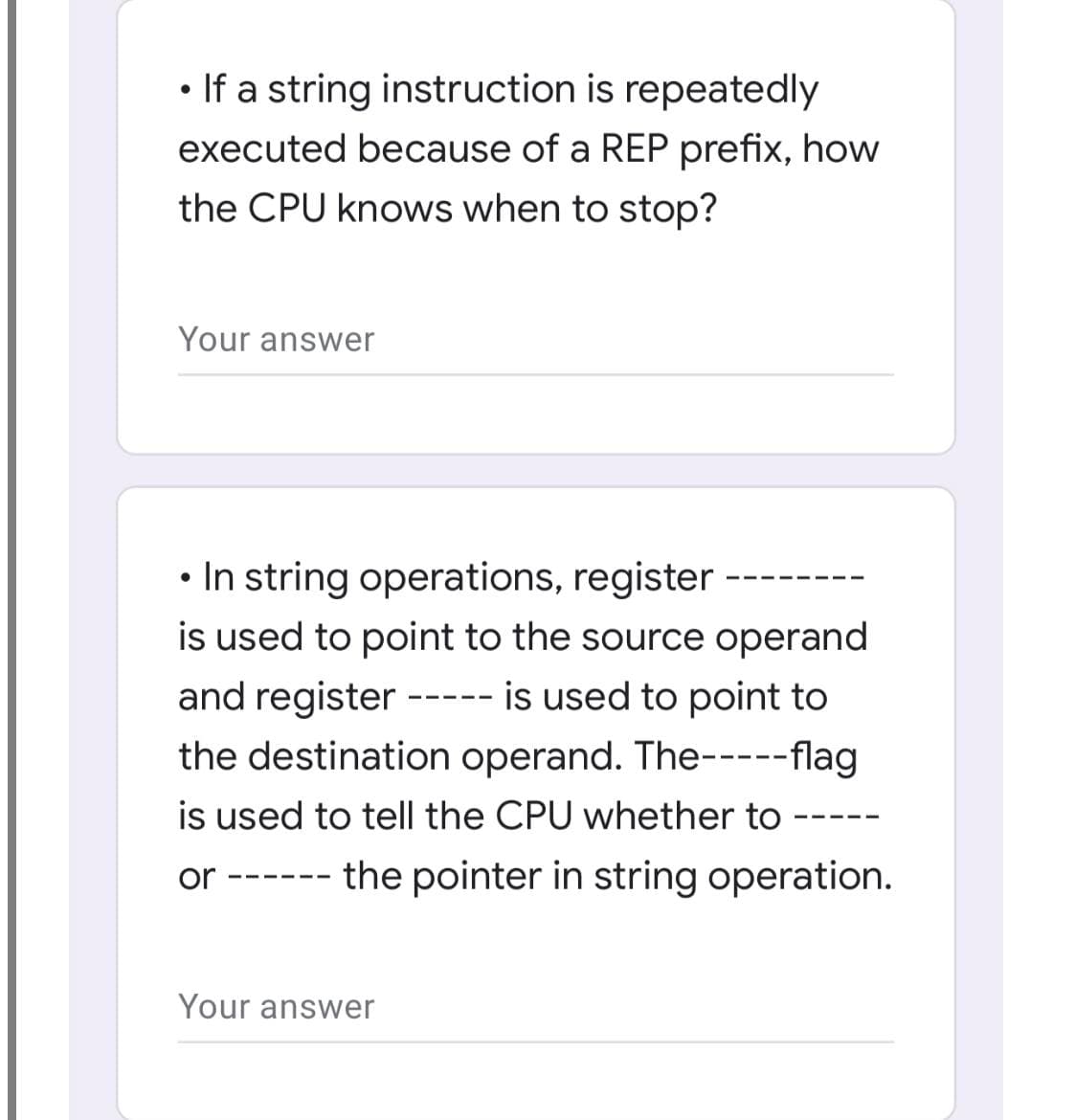

executed because of a REP prefix, how the CPU knows when to stop?

Q: • If a string instruction is repeatedly executed because of a REP prefix, how the CPU knows when to…

A: Repeat Prefix: The repeat prefixes cause repetition of sure directions that load, store, move,…

Q: Write Priority CPU Scheduling ?Algorithm In C++ with Gantt Chart

A: C++ program for the implementation for Priority CPU Scheduling algorithm with different arrival time…

Q: The CPU of a computer may be set up in three different ways: as a general register, a single…

A: The central processing unit (CPU) of a computer is the part of the machine that obtains and executes…

Q: What does "reduced" imply when referring to a computer with a constrained set of instructions?

A: A computer with a central processing unit (CPU) that follows to the processor design idea of…

Q: In microprocessor, zero flag is set to 1 when the result is zero the result is positive O the result…

A: Answers for both with explanation given below

Q: In 8086, instruction queue is a part of, O a. EU O b. BIU Oc. neither EU nor BIU O d. both EU and…

A: Required:

Q: What happens when the CPU executes a load instruction that reads the byte at address 0x03d4

A: In the given problem, we will discuss how the CPU executes a load instruction.

Q: 13) Loading the contents of the stack in to the CPU register is called )a. Push b. MOV c. POP

A: Answer13. The answer is option(c) POP Explanation:- The pop instruction are used to load the stack…

Q: Microprocessor lab tasks - Solve the problems in assembly language using emu8086 solution…

A: 1) ; You may customize this and other start-up templates; ; The location of this template is…

Q: If DP is $F0, then the CPU can access any memory locations in the following page: None of the other…

A: 6809 processor: It is an 8-bit microprocessor. 6809 processor was designed by Motorola's Terry…

Q: Branches and Branches Here is a portion of a program. The initial condition codes have the values N-…

A: Branches and BranchesHere is a portion of a program. The initial condition codes have the values N =…

Q: addressing mode is most suitable to change the normal sequence of execution of instructions. А.…

A: Correct answer id (c) - Relative

Q: Course: Assembly Language Question: Write a POWER MACRO N, which takes the number in AX and raises…

A: Given question has asked to Write a POWER MACRO N, which takes the number in AX and raises it to…

Q: The instructions that are used to call a subroutine from the main program and return to the main…

A: 1) JMP instruction is used to jump the control of the execution from one place to the specified…

Q: What are the benefits of using indirect addressing in a machine language as opposed to immediate…

A: In Memory direct addressing to , the memory address is in the order. In Register roundabout tending…

Q: Why do modern machines typically pass subroutine parameters in registers rather than on the stack?

A: Modern machines typically pass subroutine parameters in registers rather than on the stack because…

Q: Write an 8086 assembly language program that compares two values if 1st value is greater then add…

A:

Q: Using the Assembly Language Programming of 8086, write and simulate a program that adds two data…

A: Find the required code given as below :

Q: When an interrupt occurs, which of these functions would be the last to occur? O a. the processor…

A: The stack is an SRAM area that is used to store the general registers temporarily. An operation…

Q: uced" imply when referring to a computer with a constrained set of ins

A: Introduction: Decreased instruction really indicates that the amount of work done by each…

Q: A program accesses ten continuous memory locations. The CPU will take less time if ?the addressing…

A: Given: A program accesses ten continuous memory locations. The CPU will take less time if the…

Q: Write a sequence of statements that display a subroutine’s return address. Hint: the esp register…

A: Answer)

Q: Define the ways that auto increment and auto decrement can change the address.

A: Definition: The contents of a register mentioned in the instruction serve as the operand's effective…

Q: a) Write a subroutine which copies a string starting from address $1100 to a location starting from…

A: As according to guidelines we can answer only one question at a time if you want answer of…

Q: There are a variety of reasons why machine designers prefer that all instructions be the same length…

A: A stack machine is a method of calculation where chief control is kept up entirely through attach ,…

Q: The statement ( AR – M[AR]) in basic computer means: O A. Fetch effective address from memory O B.…

A: AR (Address register) - Holds address for memory M[AR] - content of the memory word specified by the…

Q: What is meant by CPU Scheduler?

A: CPU scheduler: It is a scheduler which is a process that allows one process to use the central…

Q: e factors of a number and store the result at address 200 in memory. Sample Answer: I wrote a…

A: Assembly code as,

Q: 0001 = Load AC from memory 0010 = Store AC to memory 0101 = Add to AC from memory 0011 = Load AC…

A: Please find the answer below:

Q: The CPU determines which operation to do during the fetch-decode-execute part of the…

A: The CPU is mainly responsible for running applications utilizing the fetch-decode execution cycle…

Q: The CPU of a computer may be configured in one of three ways: as a global register, an individual…

A: Answer:

Q: е, calcu nds, exe ional br address stage c ng new n until th

A:

Q: ASSEMBLY Local variables are stored on the runtime stack, at a higher address than the stack…

A: Given: ASSEMBLY Local variables are stored on the runtime stack, at a higher address than the…

Q: The addressinh mode is what it sounds like. Give instances of 8051 addressing modes.

A: Introduction: Addressing modes are instructions for transferring data from one register to another…

Q: 5. Write an assembly language program that inputs the number of a student from the keyboard and…

A: Solution: #Assembly code: reverse: push rbp mov rbp, rsp mov DWORD PTR [rbp-20], edi mov DWORD…

Q: : Define the following terminologies in Assembly Language Programming: Addressing M

A: NOTE: ACCORDING TO COMPANY POLICY WE CANNOT SOLVE MORE THAN THIS. YOU CAN RESUBMIT THE QUESTION…

Q: Find out the Object code for each line of instructions. (SIC/XE) The address needs hexadecimal.…

A: Here we write code in given format:…

Q: Why might a compiler generating x86_64 final code allocate space for all parameters in the…

A: Answer is given below-

Q: t is the difference between a debug command and a CP

A: Lets see the solution.

Q: WHAT DO YOU THINK ABOUT THIS IF IT IS TRUE? A computer's CPU may be configured in three ways: as a…

A: The central processing unit (CPU) of a computer is the part of the machine that obtains and executes…

Q: hicroprocessor CPUS do not understand mnemonics as they are, they have to be converted to binary

A: Because microprocessor CPUs do not understand mnemonics as they are, they have to be converted to…

Q: Translate the following algorithm to this simple computer's assembly language and then to machine…

A: Answer: This is question based on MIPS instruction so we have answered in hand written format. this…

Q: 10) Functions in high-level languages often declare local variables just below the return address on…

A: According to the information given:- We have to write a function in high level language on the basis…

Q: When the INT instruction executes, what is the first task carried out by the CPU?

A: Task carried during the execution of INT instruction INT is an assembly instruction for x86…

Q: The CPU decides the operation to do in the portion of the fetch-decode-execute cycle.

A: The main job of the CPU is to execute programs using the fetch-decode-execute cycle .This cycle…

Q: Soru 1 Round Robin CPU Scheduling can be implemented to include priorty for the processes.…

A: Correct Answer: False

Q: In a 32-bit microprocessor, if any instantaneous PC (program counter), register value of the program…

A: We are going to find out the value of PC(program counter) after execution of 7 commands from given…

Step by step

Solved in 2 steps

- Copy the top 2 words from the stack into registers AX and CX respectively. Do this withoutchanging the stack pointer do not use POP instructions! Use BP as the base register. Howwill your program know what value to place in BP?To ensure that the stack contains some known values, place the following code at thebeginning of your program:mov dx, 1234Hpush dxmov dx, 0ABCDHpush dxSave the based.s source file as /home/username/project1/based.sPlease answer the following with the reference; 1a. What is the purpose of the movq 0x10 (%rdi), rbp instruction here (at the C level or higher)? How does this relate to the earlier call to pushq rbp? 1b. Alice just remembered that the original C code had the following structure! Using what you now know about mystery, fill in the blanks with C code. long mystery ( TreeNode* t){ If ( ) { return ; } return }Question1: Multiple Choice : (please leave it to other tutors who can answer all my sub-question since this is my last question for this month) 1-If for some inputs, a procedure never terminates, the procedure lacks a. computability b. definiteness c. finiteness d. scalability 2-The elements of the ISA for a particular type of CPU include a. addressing modes b. data types c. instructions d. a and b e. a, b and c Question 2: Perform the following logical operations and express your answers in hexadecimal notation. x3487 AND x7254 xABCD or x3234 xF098 XOR x3344

- 25: . Find the time delay in the following program if the crystal frequency is 1 MHz. Do not ignore the time delay due to the first and last instruction. DELAY: LDI R16, 30 AGAIN: LDI R17, 35 HERE: NOP NOP DEC R17 BRNE HERE DEC R16 BRNE AGAIN RET 26: Write a program to display 2 on 7 segment. A 7 segment is connected to PortD.Consider the following instruction:Instruction: Add Rd, Rs, RtInterperation: Reg[Rd] = Reg[Rs] + Reg[Rt] RegWrite MemRead ALUMux MemWrite ALUOp RegMux Branch a, What are the values of control signals generated by the control in Figure 4.2 for the above instruction? b, Which resources (blocks) perform a useful function for this instruction? c, Which resources (blocks) produce outputs, but their outputs are not used for this instruction? d, which resources (blocks) produce no output for this instruction?When we execute a program that contains a lot of if-statements or for/while-loops, the pipelineof Teletraan-2 faces a problem. The instruction fetch stage does not know which branch of theif-statement shall be fetched, until the write back stage writes the True/False value of the ifcondition to a flag register. What should we do to alleviate the problem?A. Don't wait. Let the CPU predict which branch will probably be executed, and fetch theinstruction(s) of that branch. If it is later revealed the prediction is wrong, undo theinstruction(s).B. Don't wait. Fetch-decode-execute the instructions of all branches of the if-statement.C. Nothing. We can only let the instruction fetch stage wait for the write back stage to finishwriting the value of the if-condition.D. Eliminate all if-statements during the assembly process.

- Write MIPS assembly for the following function. Assume N is passed to yourfunction in register $a0. Your output should be in register $v0 at the end of yourfunction. Note: You must implement this function recursively. The purpose of thisassignment is to learn how to manipulate the stack correctly in MIPS. int Myfun (int N){ if (N<3) return 1; return ( 2* Myfun(N-1)+ Myfun(N-2));}Please explain each instruction with a comment. Please submit your source codeand a screenshot that shows the registers with correct output value for N=3, i.e.,Myfun(3) returns 3 and Myfun(4) returns 7For the (pseudo) assembly code below, replace X, Y, P, and Q with thesmallest set of instructions to save/restore values on the stack and update the stackpointer. Assume that procA and procB were written independently by two differentprogrammers who are following the MIPS guidelines for caller-saved and callee-savedregisters. In other words, the two programmers agree on the input arguments andreturn value of procB, but they can't see the code written by the other person. procA:$s0 = ...$s1 = ...$s2 = ...$t0 = ...$t1 = ...$t2 = ...X$a0 = ...$a1 = ...jal procBY... = $s1... = $t0... = $t1... = $a0jr $raprocB:P... = $a0... = $a1$s2 = ...$t0 = ...Qjr $raAdd control states to the following to implement a bitwise-OR-with-immediate instruction (as decoded by the when below), such that ori $rt,$rs,immed yields rt=(rs|immed). This is actually a MIPS instruction, as we'll discuss later. Hint: except for using bitwise OR instead of addition, it's essentially the same as the addi that is already handled by: when (op()) {addi} Addiwhen (op()) {ori} OriStart: PCout, MARin, MEMread, Yin CONST(4), ALUadd, Zin, UNTILmfc MDRout, IRin Zout, PCin, JUMPonop HALT /* Should end here on undecoded op */Addi: SELrs, REGout, Yin IRimmedout, ALUadd, Zin Zout, SELrt, REGin, JUMP(Start)Ori: You can test your specification using the http://super.ece.engr.uky.edu:8088/cgi-bin/simple.cgiLinks to an external site. simulator. For testing, you can add the initial conditions: MEM[0]={ori}+rs(9)+rt(10)+immed(3)MEM[4]=0$9=5 Register $10 should end-up holding the value 0x00000007 (3|5 = 7 decimal).

- Add control states to the following to implement a bitwise-OR-with-immediate instruction (as decoded by the when below), such that ori $rt,$rs,immed yields rt=(rs|immed). This is actually a MIPS instruction, as we'll discuss later. Hint: except for using bitwise OR instead of addition, it's essentially the same as the addi that is already handled by: when (op()) {addi} Addiwhen (op()) {ori} OriStart: PCout, MARin, MEMread, Yin CONST(4), ALUadd, Zin, UNTILmfc MDRout, IRin Zout, PCin, JUMPonop HALT /* Should end here on undecoded op */Addi: SELrs, REGout, Yin IRimmedout, ALUadd, Zin Zout, SELrt, REGin, JUMP(Start)Ori: You can test your specification using the http://super.ece.engr.uky.edu:8088/cgi-bin/simple.cgi (Links to an external site.) simulator. For testing, you can add the initial conditions: MEM[0]={ori}+rs(9)+rt(10)+immed(3)MEM[4]=0$9=5 Register $10 should end-up holding the value 0x00000007 (3|5 = 7 decimal).Implement a new unary instruction in place of N0P0 called ASL2 that does two left shifts on the accumulator. V should remain unchanged, but N and Z should correlate with the new value in the accumulator, and C should be the carry from the second shift. Write a program that tests all the features of the new instruction.Write and simulate a MIPS assembly-language routine that: 1. Prints your group number, for example “Group 1”, 2. Computes the dot product of two vectors, A_vec and B_vec, as described in Lab 4 of the Lab Manual, 3. Stores the result at memory word DOTPROD, and 4. Prints the result preceded by the phrase: “The result of the dot product is: “. Your data segment should look like the following: .data group: .asciiz “\nGroup x” msg: .asciiz "\nThe result of the dot product is: " A_vec: .word x, 4, 20, 13, 3, 10, 5 B_vec: .word 4, 2, 1, 2, 5, 2, 4 n: .word 7 DOTPROD: .word 0 Replace each “x” with your group number.