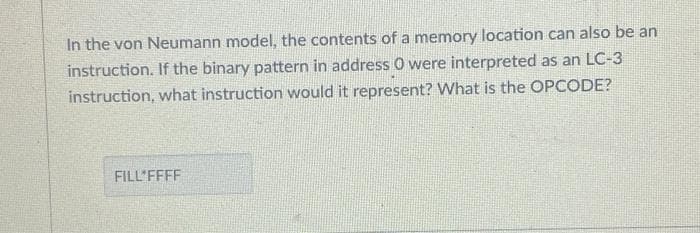

In the von Neumann model, the contents of a memory location can also be an instruction. If the binary pattern in address O were interpreted as an LC-3 instruction, what instruction would it represent? What is the OPCODE?

Q: What are the advantages of the Harvard architecture in relation to the von Neumann architecture? If…

A: - Harvard and von Neumann architecture are computer architectures of different times. von Neumann is…

Q: Consider the array : char arr[5]; If address of arr is 100 then what will be the address of…

A: Given: char arr[5]; Address of arr=100. Size of one char = 1 byte. To Find: Address of arr[4]

Q: 1. Suppose the Vole memory cells from addresses 0x00 to 0x05 contain the bit patterns given in the…

A: According to the Bartelby guideline we are suppose to answer only one question at a time. Kindly…

Q: Suppose a computer using direct-mapped cache has 2 bytes of byte-addressable main memory and a cache…

A: Given information: - memory address is: (0DB63)16

Q: Consider a machine with a word addressable and a word consists of 2 bytes, main memory of 236 bytes…

A: Given in the question: Main memory size = 236bytes Total address space = 36 bits Block size = 32…

Q: Consider the basic computer whose microinstruction set is described by table 1. If the f Address E02…

A: It is defined as a type of computer memory used to quickly accept, store, and transfer data and…

Q: Assume a cache system has been designed such that each block contains 4 words and the cache has 1024…

A: Given: Assume a cache system has been designed such that each block contains 4 words and the cache…

Q: Explain with a diagram the process of mapping a logical address to a physical address in the main…

A: According to the question In operating systems, there is always a need to map from a logical address…

Q: Suppose a computer using fully associative cache has 224 bytes of byte-addressable main memory and a…

A: Given: The computer is using fully associative cache. Size of the main memory = 224 Bytes Size of…

Q: 23)The last action taken by the CPU in the fetch-execution cycle is: a. IR[address] --> MAR b. PC +…

A: Here, we are asked the last action taken by the CPU in the fetch-execution cycle is. During…

Q: Suppose a computer using direct-mapped cache has 232 bytes of byte-addressable main memory and a…

A: Given: The computer is using direct mapped cache. Size of main memory = 232 Size of block = 1024…

Q: 12. Consider the following diagram. Fill the physical memory with appropriate addresses: a,b,.n.o,p…

A: Solution:

Q: Consider an 8-bit microprocessor performing an 8-bit arithmetic (all the internal registers are of…

A: The answer is

Q: Suppose a computer using fully associative cache has 224 bytes of byte-addressable main memory and a…

A: Size of main memory = 224 bytes Size of cache= 128 bytes = 27 bytes Size of each block= 64 bytes =…

Q: Consider a byte-addressable computer with 24-bit addresses, a cache capable of storing a total of…

A: Advantages of using direct memory mapping: 1) No replacement algorithm is needed. Disadvantages of…

Q: I have a little bit problem with my late quiz for computer architecture, I get the answer from my…

A: Following information has been given: Main memory size = 4 Gbytes(GB) = 210x 210x 210x 22 bytes…

Q: If logical addresses are represented using m bits as shown below, where m=4 and n=2. What is the…

A: Actually, memory is used to stores the data.

Q: For a system employing paging, consider a logical address space of 1024 pages of 4096 bytes, mapping…

A: Here we have to find but used for logical address space(LAS)..LAS is consist of two parts page no…

Q: Consider the main memory size of 128 kB, Cache size of 16 kB, Block size of 256 B with Byte…

A: Answer is in next step.

Q: Suppose a computer using set associative cache has 216 words of main memory and a cache of 128…

A: Given Data: Size of Main Memory = 216 words Size of Cache = 128 block The Cache is 4-way Set…

Q: Add the following instructions to the computer of Sec 7-3 (EA is the effective address). Write the…

A:

Q: Consider a 4-way set associative cache consisting of 128 lines with a line size of 64 words. The CPU…

A: Given that, Number of lines= 128 Line size= 64 words Number of bits in main memory address= 20 bits…

Q: Assume a cache system has been designed such that each block contains 4 words and the cache has 1024…

A:

Q: For a 512k x 32 memory system, how wide does the incoming address bus needed to be in order to…

A: Here is the explanation about the width of the address bus:

Q: Q1:Suppose the initial physical address of a segment register is given by 0E41:A02EH. Determine the…

A: The solution for the above given question is given below:

Q: Consider the following registers X and Y of a certain computer contains the decimal values 1024 and…

A: Introduction. Given, register X=1024 register Y=4096 Three instructions, are given:- I1.…

Q: Consider a Computer which has a memory which is capable of storing 4096 K words and each word in…

A: Given Data : Nmber of memory words = 4096K words Word size = 32 bits Addressing modes = 6 Number of…

Q: Consider a hypothetical memory access time: 1 memory bus clock cycle to send an address

A: Answer: The bandwidth attainable from parallelizing the DRAM initialization time would be 8 words…

Q: 1. In a non-paged address translation, if the base register contains 0x52000000 and the limit…

A: For non-paged memory, all the framework needs to do is guarantee that an actual page outline is…

Q: Suppose we have a byte-addressable computer using fully associative mapping with 16-bit main memory…

A: The number of bits in the main memory address is given =16 bits In fully associative mapping a…

Q: Consider a byte-addressable computer with 24-bit addresses, a cache capable of storing a total of…

A: Introduction: The 4-way set associative the memory block is divided into 4 blocks containing 4-lines…

Q: Consider a 32-bit microprocessor, with a 16-bit external data bus, driven by an 8-MHz input clock.…

A:

Q: Consider a memory system that uses a 32-bit address to address at the byte level, plus a cache that…

A: Step 1:- a)Address Format tag=20 bits line size is 64 bytes 64 bytes=26 bytes set/line(r)=6 bits…

Q: Consider a 32-bit microprocessor, with a 16-bit external data bus, driven by an 8-MHz input clock.…

A: Introduction :Given , 32 bit microprocessordata bus is 16 bits clock rate is 8 MHzWe have to…

Q: consider a processor using 32-bit memory addresses, also a 4 KiB (of actual data) direct-mapped…

A:

Q: Consider a word addressable system. The main memory is of size 2 MB and direct-mapped cache…

A: consider word addressable system. The main memory size of 2MB and direct -mapped cache containing…

Q: Consider a 32 bit microprocessor that has on chip 32 K byte 4 way set associative cache. Block size…

A: Introduction Given, 32 bit address. 32 KB ,4 way set associative cache. Block size = two 32 bit…

Q: Consider a 1-address CPU that has a memory unit with 128K words of 32 bits each. An instruction is…

A: Size of 1 word = 32 bits Size of instruction = 1 word = 32 bits Addressing mode = 2 bits Register…

Q: The contents of memory location B0007H are FFH and those at B000AH are O0H. What is the data word…

A: The contents of the memory location B0000H are FFH, and those atB0001H are 00H, what is data word…

Q: Under the von Neumann architecture, a program and its dataare both stored in memory. It is therefore…

A: The von Neumann architecture is not that all data and instruction are stored in memory, rather these…

Q: Suppose a computer using fully associative cache has 224 bytes of byte-addressable main memory and a…

A: The computer has the fully associative cache with cache files of 128 blocks A fully associative…

Q: In the figure below, the typical organization of a modern von Neumann processor is illustrated. Note…

A: (1)Active part of the computer,which does all the work of data manipulation and decision making…

Q: Consider a hypothetical microprocessor generating a 16-bit address (for example, as- sume that the…

A: "16-bit memory" and "8-bit memory" could mean a number of different things, however, I'll assume…

Q: Consider a machine with a byte addressable main memory 24º bytes, block size of 16 bytes and a…

A: Introduction :

Q: Suppose a byte-addressable computer using 4-way setassociative cache has 216 words of main memory…

A: Due to the byte memory, this meant 1 Phrase = 1 byte. The main size of the memory therefore = 216…

Please don't copy

Trending now

This is a popular solution!

Step by step

Solved in 2 steps with 1 images

- How does pipelining improve CPU efficiency? What’s the potential effect on pipelining’s efficiency when executing a conditional BRANCH instruction? What techniques can be used to make pipelining more efficient when executing conditional BRANCH instructions?A(n) ________________ instruction always alters the instruction execution sequence. A(n) ______________ instruction alters the instruction execution sequence only if a specified Condition is true._____ is a CPU design technique in which instruction execution is divided into multiple stages and different instructions can execute in different stages simultaneously.

- The von Neumann architecture stores a program and its data in memory. Thus, if a program misinterprets a memory address for a piece of data when it really contains a program instruction, it may unintentionally (or intentionally) change itself. What effects will this have on you as a programmer?For a microprocessor 68000 Motorola system, how many memory addresses which can be accessed by it? Prove it and justify the last address of the memory location. Then, sketch the memory map of it by using the address calculated.Under the von Neumann architecture, a program and its data are both stored in memory. Itis therefore possible for a program, thinking a memory location holds a piece of data when it actually holds a program instruction, to accidentally (or on purpose) modify itself. Whatimplications does this present to you as a programmer?

- Under the von Neumann architecture, a program and its dataare both stored in memory. It is therefore possible for a program,thinking that a memory location holds a piece of data when itactually holds a program instruction, to accidentally (or onpurpose) modify itself. What implications does this present to youas a programmer?Q1:Suppose the initial physical address of a segment register is given by 0E41:A02EH. Determine the physical address, base and final address of that segment register of 8086 microprocessorWhat happens if a cache miss occurs? Is there a significant lag in the execution of the instruction as a consequence of this? If that's the case, why is that?

- Let's pretend for a moment that we have a byte-addressable computer with 16-bit main memory addresses and 32-bit cache memory blocks, and that it employs two-way set associative mapping. Knowing that each block has eight bytes, please calculate the size of the offset field and provide evidence of your calculations.What are the advantages of the Harvard architecture in relation to the von Neumann architecture? If you equip a von Neumann machine with a dual-ported RAM (that is a RAM which allows two concurrent accesses), does this make it a Harvard machine, or is there still something missing?How big of an improvement is a segmented memory address translation as compared to a translation that is done directly?