JumpOffset X This instruction will jump to the address calculated by adding the given address, X, to the contents of the accumulator. Show how this instruction would be executed using RTN.

JumpOffset X This instruction will jump to the address calculated by adding the given address, X, to the contents of the accumulator. Show how this instruction would be executed using RTN.

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 15VE: A(n) ________________ instruction always alters the instruction execution sequence. A(n)...

Related questions

Question

dont answer without knowledge sure dislike if not answer properly

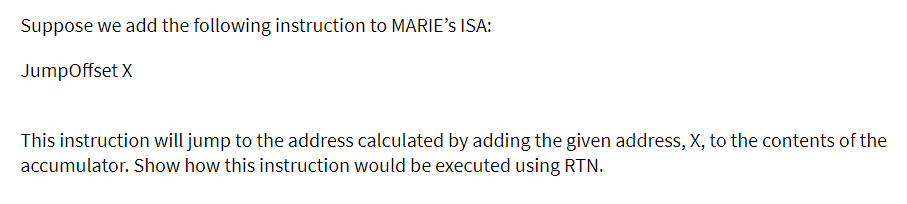

Transcribed Image Text:Suppose we add the following instruction to MARIE's ISA:

JumpOffset X

This instruction will jump to the address calculated by adding the given address, X, to the contents of the

accumulator. Show how this instruction would be executed using RTN.

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Principles of Information Systems (MindTap Course…

Computer Science

ISBN:

9781285867168

Author:

Ralph Stair, George Reynolds

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Principles of Information Systems (MindTap Course…

Computer Science

ISBN:

9781285867168

Author:

Ralph Stair, George Reynolds

Publisher:

Cengage Learning