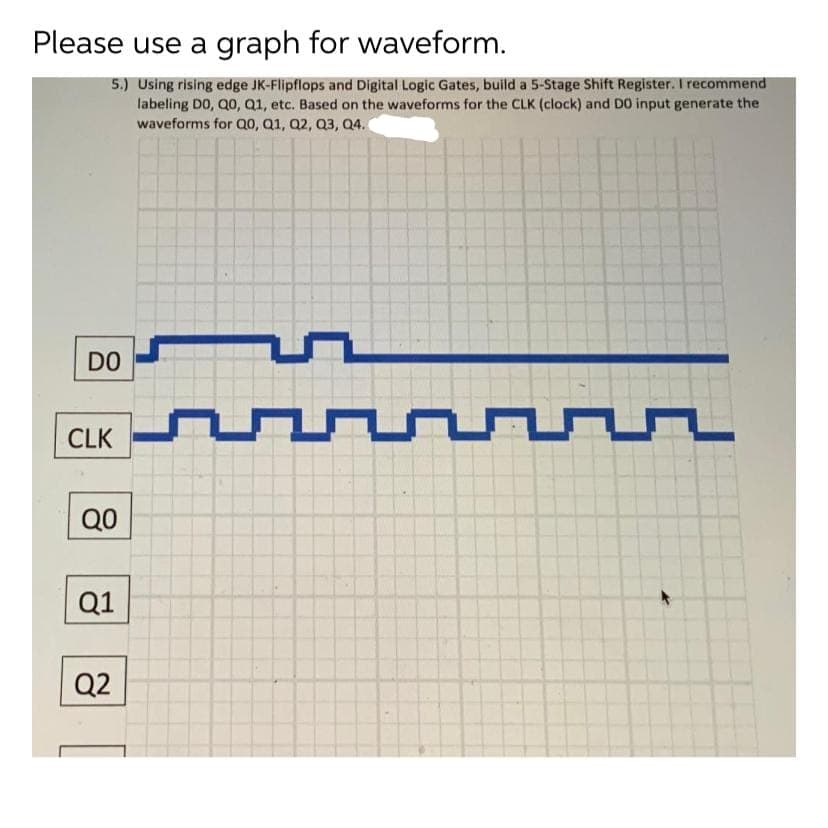

Please use a graph for waveform. 5.) Using rising edge JK-Flipflops and Digital Logic Gates, build a 5-Stage Shift Register. I recommend labeling DO, Q0, Q1, etc. Based on the waveforms for the CLK (clock) and DO input generate the waveforms for Q0, Q1, Q2, Q3, Q4. DO CLK

Q: ng one put Ok gdte, ne 2- input AND gate and one 2-input NAND gate. (B) Implement the same function…

A:

Q: Design a 3-bit ripple up counter using negative edge trigger T flip-flops.

A: Given that Design a 3-bit ripple up counter using negative edge trigger T flip-flops. T flip-flops…

Q: Using MUX, design a circuit that has the following min-term: F =EA,B.C,D)…

A:

Q: 3. Design a Full Adder circuit having the inputs as A, B and Cin. The output shoul Carry_Out.…

A: Designed a full adder circuit with A,B and Cin

Q: By using external gates and a 4-to-1 line multiplexer, implement the Boolean function F(A, B,C, D) =…

A: We start by creating a truth - table for the given condition :- For the case of AB = 00, the…

Q: 9. Construct a logic circuit that implements a 2-bit, 4-function ALU that has oper- ations ADD, AND,…

A: An arithmetic logic unit is a multi-operation, combinational logic function. It can perform a set of…

Q: Question 5: F(a,b,c,d)=[(0,1,3,6,10,11,14) Implement the above boolean function using a. 4:1 MUX(s)…

A:

Q: 8- Assuming using the multiplexer design approach should be 9- The number of transistor required to…

A: The Transistor-Transistor Logic is a logic family made up of BJTs.

Q: a Construct circuits from inverters, AND gates, and OR gates to produce the output (x + yz)(xy + z).

A:

Q: Hw: Design the complete subtractor circuit using MUX a) Using 8-to-1 MUX b) Using 4-to-1 MUX c)…

A: Actually, the answer has given below:

Q: A В. Y

A: What is verilog code? Verilog code is not a programming language. It is a hardware description…

Q: Please find the simplest "sum-of-products" expression of f(A, B, C, D) = 2 (1,4,6,8,11,13,14) +…

A:

Q: 2-Realize the EX - OR gates using minimum number of NAND gates?

A:

Q: Q2: Minimize the following function using K-Map and draw the output Logic cct. Using Logisim…

A: Minimize the given function using k-map with output logic circuit

Q: 3- Design a circuit using Demux's of (2-selectors) and OR gates only to implement the two S.O.P…

A: The demultiplexer is a combinational logic circuit designed to switch one common input to one of…

Q: . Obtain a logic data book and list down all the available multiplexers, decoders, and…

A: list down all the available multiplexers, decoders, and decoder/demultiplexers Multiplexers 2-1…

Q: Depending on X which is the last digit of your student number, implement the following function F by…

A:

Q: (a) Provide a block diagram and a function table for the D-type flip-flop with falling edge…

A: Falling edge Triggered D flip flop | Negative Edge Triggered D flip flop The D flip-flop, which…

Q: 2. Using an 8-to-1 Multiplexer and external gates, implement the following Boolean function: F(w, x,…

A: We are given a boolean function F and we have to implement it using 8:1 multiplexer (mux) and…

Q: OR A. B - A. B. module OR (ar bay) Follow the same steps, but use t gates, and each gate has its ow…

A: I have solved all the three parts - NAND, NOR, XOR. First their circuit, then truth table and then…

Q: 3. The table that is referred when deriving inputs to the Flip-Flops in a clocked sequential circuit…

A: Subject: Digital circuit and fundamentals of microprocessor 3)The table that is referred when…

Q: Draw a SR latch circuit using only 4-inputs with truth table?

A: I have given an answer in step 2.

Q: F(A, B, C, D) = Em(0, 1, 2, X-2, X+1, X+2, X+3, X+5, 15), implement the following function F by…

A:

Q: a. In a 8 bit Ripple Carry Adder, what is the worst case and best case gate delay from A0,B0,C0 to…

A: It is defined as a combinational logic circuit. It is used for the purpose of adding two n-bit…

Q: The function f from the following circuit is equivalent to (' stands for bar or inverlted ihput). O…

A: Actually the answer you have marked is wrong From the given logic gate diagram We have one NOR gate,…

Q: mplement the following function F by using one 4-to-1 multiplexer and external gates (OR, AND,…

A: It is a combinational circuit which have many data inputs and single output depending on control or…

Q: 2. Design a full adder and a full subtractor using minimum nu: ber of two-input NAND and two-input…

A: Hello student, hope you are doing good. The answer to the questions are attached below.

Q: Q4. Using block diagram, implement the given circuit with a decoder and external gates. Minimize…

A: Answer has been explained below:-

Q: 2. The following serial data stream is to be generated using a J-K positive edge-triggered Flip -…

A:

Q: Write the three outputs of X, Y and Z in terms of the four inputs A, B, C and D for the follow logic…

A:

Q: 2- write a ALP to implement an NOR gate and store the result in the memory location 8000H?

A: ALP to implement an NOR gate and store the result in the memory location 8000H is given below:-

Q: Question 7 Assume we want to design a sequential circuit that toggles its msb state variable (MN) on…

A:

Q: Simplify the following expression and implement it using NOR gate.…

A: A karnaugh map provides a pictorial method of grouping together expressions to minimize a given…

Q: - Implement ( without simplification) F= (A+B).(C+A.D) using NAND gates only. - Design a logic gates…

A: As per our guidelines we are supposed to answer only one question. Kindly repost other questions as…

Q: Problem 3 Design a mod-16 asynchronous (ripple) UP counter .Use positive edge triggered J-K…

A: MOD Counters are cascaded counter circuits which count to a set modulus value before resetting. The…

Q: Find the content for the 4-bit shift register of the following sequential circuit during 4 clocks.…

A: Shift register: Shift register is a sequential logic circuit. It is capable of storing and…

Q: Express the A and B outputs of the following circuit as sum-of-minterms. 4 x 1 MUX S, & 4 x 1 MUX S,…

A: The minterm expression from the following 4×1 MUX function is - Y= s1¯…

Q: a) Construct a truth table for 2-bit half adder and write down the functions of SUM and CARRY using…

A: A 2-bit half adder is used to add two binary bits. If any one input is 1, then the output is 1, else…

Q: Implement the following function using NAND gate only: a) F (D,C,B,A) = E (4,5,7,12,14,15), d…

A: Here, we are given two functions F and Y and we asked to design logic circuits for them using NAND…

Q: Problem_#02] Given the inputs shown below to a full-adder, what are the outputs. (a) A = 1, B = 0,…

A: Given:

Q: Q2/ (Answer Two Only ) from the following : 1- Implement F= (A+B).(C+A.D) using NOR gates only. 2-…

A: 1) given F = ((A+B)'.(C+(AD)'))' Implementation of the given expression using only nor Gates is as…

Q: Given the following logic functions: six (1X2 decoders), three AND gates, one NOT gate, two (2X1…

A: ANSWER:-

Q: Solve 29(a,b)

A: 29. (a) Simplification of the given function is given below: -

Q: A) Using positive edge T Flip Flop design 3-bits synchronous down counter if the input is '1' and…

A: The Answer is in step-2.

Q: Using 4 exclusive –Or gates and a 4-bit full adder MSI circuit, Construct a 4- bit paralle3l adder/…

A:

Q: Draw the schematic of the optimized output function derived from Q1(c) only using NOR and NOT gates.

A:

Q: Using half-adders and full-adders as a block together with external gates, design the following…

A: Half adder : It has two inputs that generates two outputs sum and carry Full adder: It has three…

Q: (a) use gate equivalence to convert the circuit into a four-level circuit containing only NAND gates…

A: Answer: (a)

Q: the following state table and sequential circuit, choose the correct optimized input and output…

A:

Trending now

This is a popular solution!

Step by step

Solved in 2 steps with 2 images

- Based on your perspective, briefly discuss the structure of the different types of binary codes. What are the differences between asynchronous and synchronous sequential logic circuits? Rationalize your answer. Design a simple logic circuit for a Set/Reset (SR) Latch, based on any actual application of latches. Describe your design using at least three (3) sentences. Give three (3) applications of Flip-flops, and describe the process of each.1. Obtain a logic data book and list down all the available multiplexers, decoders, and decoder/demultiplexers. 2. Show how 74251 8-to-1 line multiplexers may be connected to implement a 16-to-1 MUX. 3. What are the advantages and disadvantages of the MUX and the decoder methods over one another? 4. Describe how a combinational circuit may be implemented using decoders given the minterm list form of two functions. 5. What are the advantages and disadvantages of the MUX and the decoder methods over conventional methods of implementing a function using logic gates?5 (b)How many 3-to-8 line decoders with an enable input are needed to construct a 6-to-64 line decoder without using any other logic gates? Also draw the circuit.

- First, you must create a logic circuit using only basic gates such as AND, OR, NOR, NAND, NOT, etc. to implement an ADDER capable of adding two 4 bit binary numbers. Second, you must create a logic circuit using only basic gates such as AND, OR, NOR, NAND, NOT, etc. to implement a Subtractor that is capable of subtracting the second number from the first, by converting the second number into its 2's complement form and then adding the resulting number to the first number. You do not need to worry about accomodating the addition or subtraction of negative numbers. Finally, create a limited ALU (Arithmetic logic unit) circuit using Logism that implements a Full Adder circuit capable of adding 2 – 4 bit binary numbers and subtracting 2- 4 bit binary numbers. Also, implement the ability to select a bitwise AND operation and a bitwise OR operation. For the ALU it is acceptable to use the Adder and Subtractor circuits that are listed under the "Arithmetic" folder in Logism. (Logism tips and…1. Draw a circuit to get mod-12 counter?What is the modulus if Q3 and Q0 drive the nand gate?A multiplier is to be designed for two 2-bit inputs using the algorithm. (Draw schematic, truth table, and write Verilog HDL code) (Use: and, not, xor gates)A result will be written at 7-segment on the Altera FPGA board. (Draw schematic, truth table) (Use: and, or, not, xor gates)

- 3(a): Consider the following circuit, which uses two D flip-flops with falling edge triggers along with -bit full adder. The flip-flops are controlled by a single clock, C. Suppose C, Q0 and Q1 all initially have the value 0. First, fill in the blanks in the "i " = 0 (initial state)" row to show the values of D0 and D1 at this initial time (assume the results of the adder have had time to stabilize) . Next, show the values of Q0 , Q1, D0 , and D1 once they have stabilized after the ith falling edge of the clock, where i ranges from 1 to 4. Note that both the A and Carry In inputs of the adder are (Q not ) Q'0 not Q0 None of these first four rows should be the exactly the same.Design a two-bit counter (sequential circuit) using falling edge triggered T-flipflops, with one input line x. When x= 1, the state of the circuit remains the same. When x = 0, the circuit goes through the state transitions byincrementing the state count, i.e., from 00 to 01, 01 to 10, 10 to 11, and 11 to 00, and repeats. Draw circuit diagramof the designed counter. if z=83,Convert z to Base-2, e.g., z= (156)10 = (10011100)2.Provide this bitstream as input to K and draw the timing diagram of the outputs of both the T-flipflops.Generate a 2-bit up counter (C1C0) with output S = 1 if d1d0 > C1C0 and S = 0 if d1d2 <= C1C0.a) Design the 2-bit counter circuit that cycles C1C0 = 00, 01, 10, 11 and loops back to 00, with inputsd1d0 and output S. Show the state transition tableb) Show the state machine diagramc) Derive the logical functional expressions, and logic circuitd) Draw the timing diagrams for S for both 25% and 75% duty cycles. At minimum, these should havethe CLK for the 2-bit counter, C1, C0 and S i created table, but I am not sure if it is correct.

- 5) Assume that the exclusive-OR gate has a propagation delay of 10 ns and that the AND or OR gates have a propagation delay of 5 ns. What is the total propagation delay time in the four-bit adder of the below circuit?Draw a circuit that implements a 3-bit Adder that takes two 3-bit numbers as input, each on 3 input lines and outputs a 4 bit number on 4 output lines. You may use the Half Adder, the Full Adder and the following gates: NOT, AND, OR, XOR. Make sure to clearly label the interface wires on your diagram and the types of gates you use.Using 4 exclusive –Or gates and a 4-bit full adder MSI circuit, Construct a 4- bit paralle3l adder/ Subtractor. Use a select input variable V so V=0 the circuit adds and when v=1, the circuit subtracts.