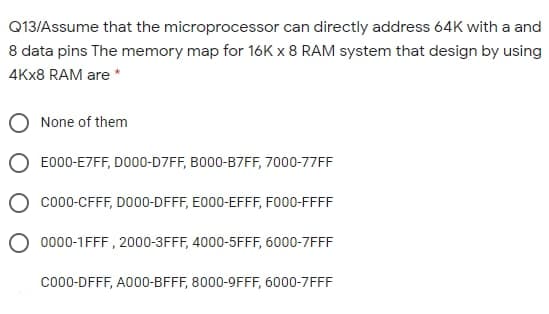

Q13/Assume that the microprocessor can directly address 64K with a and 8 data pins The memory map for 16K x 8 RAM system that design by using 4KX8 RAM are *

Q: 3. Translate following program into compiled MIPS code. Assume that g, c, i are in $s0, $s1, $s2…

A: Given: We have to translate the following program into Compiled MIPS code . Assume that g, c , i…

Q: Q13/Assume that the microprocessor can directly address 64K with a and 8 data pins The memory map…

A:

Q: 5. Assume 32 bit memory addresses, which are byte addresses. You have a 2-way cache with a block…

A: Introduction :

Q: b) Sketch a diagram showing that the data transfer from CPU to memor memory to CPU including the…

A: Here explain the diagram given below: ================================== 1.here we uses two buses…

Q: Q8/Assume that the microprocessor can directly address 64K with a R/W' and 8 data pins The memory…

A: option b

Q: Q3/Assume that the microprocessor can directly address 64K with a 16 data pins The memory map for…

A: The question is to choose the correct option for the given question.

Q: CPU Datapath The following figure shows the overall datapath of the simple 5-stage CPU we have…

A: ANSWER: a) MUX 1 Input 1: Register A input 2:Register B b) MUX 2 Input 1: Register C input…

Q: Question (la) A cache system is to be designed to store data from a 256 MB memory space. If each…

A: The solution for the above questions are:

Q: Assume that two numbers: dividend and divisor are saved in memory address M1 and M2 respectively.…

A: Given that Assume that two numbers: dividend and divisor are saved in memory address M1 and M2…

Q: Q13/Assume that the microprocessor can directly address 64K with a and 8 data pins The memory map…

A: asssume that the microprocessor can directly address 64k with a and 8 data pins the memory map for…

Q: Q3. Suppose $10 stores the base address of word array A and $1 is associated with h, convert to the…

A: Here, I have to provide a solution to the above question.

Q: Question 2: Answer each of the following 1) The memory locations 1000, 1001, and 1004 have data…

A: Here in this question we have given some instructions in low level language.and based on this we…

Q: A memory unit has a capacity of 65,536 words of 25 bits each. It is used in conjunction with a…

A: *As per the company norms and guidelines we are providing a first question answer only please repost…

Q: 5. Assume the following values are stored at the indicated memory addresses and registers: Address…

A: Solution : From the given data of the Address and their value & Register and their value.…

Q: Q8/Assume that the microprocessor can directly address 64K with a R/W and 8 data pins The memory map…

A: Given:

Q: Q13/Assume that the microprocessor can directly address 64K with a and 8 data pins The memory map…

A: Assume that the microprocessor can directly address 64k with a and 8 data pins the memory map for…

Q: Q13/Assume that the microprocessor can directly address 64K with a and 8 data pins The memory map…

A: check further steps for the answer :

Q: 8.3 An Acc-ISA CPU executes the following instructions using 3-bit op-codes and 5-bit address or 2's…

A: Here is the answer:-

Q: Please help me in this question: 18/The Hamming ECC is used to __________ . a. place data…

A: Task :- choose the correct option for given option.

Q: 1) into the data memory at address stored in ($s0). Hint: In this problem, the third byte value in…

A: Note: We are given the data in bytes so de defined the variable size by bytes "db"

Q: 2. Design your own 16 bits Memory Map, and choose the amount of memory space required for various…

A: 16bit processor,16bit(word-sized), can address 64k of RAM. 220(1048576)bytes, so can construct 20bit…

Q: To get the physical address from the logical address generated by CPU we use ____ . a. MAR b. MMU c.…

A: Task :- Choose the correct option for given question.

Q: The lastest data access is provideu DRAM's. A B SRAM's. C Registers. Caches. D

A: Please find the answer below

Q: Q: Suppose the hypothetical processor has two I/O instructions: 0011=Load AC from I/O 0111=Store AC…

A: Given data uppose the hypothetical processor has two I/O instructions: 0011=Load AC from…

Q: f the processor has 31 instructions and a 64MB memory and each data is 2 bytes wide, what is the…

A: The correct in questions Option is("c")"54"

Q: Q8/Assume that the microprocessor can directly address 64K with a R/W' and 8 data pins The memory…

A: Please check the solution below

Q: Q3: The original contents of CX, AX, memory location Beta, and carry flag (CF) are FFE IAB16,…

A: It is defined as a flip flop. It indicates some condition produced by the execution of an…

Q: QUESTION ONE (1) 1. The hypothetical machine has two I/O instructions: 0011 = Load AC from I/O 0111…

A: 34 Opcode Address (a) Instruction format Magnitude (b) Integer format Program counter (PC) = Address…

Q: Question 35 A processor running a program makes 100 accesses to memory addresses. 80% are to L1…

A: A processor running a program makes 100 accesses to memory addresses.80% are to L1 only,10% are to…

Q: Which one of the following statement is TRUE for microprocessor architecture? Von Newman…

A: INTRODUCTION: The von Neumann architecture, which is the foundation for practically all digital…

Q: 27. A memory connected to microprocessor has 20 addı 16 data lines. What will be t canacit?

A: It will have a memory capacity of 2MB

Q: Question 1 Solution should use this website for solution Sim8085 - A 8085 microprocessor simulator…

A: The program to find 2's complement of 8 bit number is given below:-

Q: 21 - In the microprocessor, the leftmost 3 bits of the 14-bit address bus are reserved for Chip…

A: Given: leftmost 3 bits of the 14-bit address address bus contains 2FBAH find the selected device ID

Q: 27. A memory connected to a microprocessor has 20 address lines and 16 data lines. What will be the…

A: INTRODUCTION: Here we need to calculate the total memory capacity.

Q: Microprocessor Hw Q1 Execute the following code and show the contents of the registers: LDI R16,$03…

A: A CPU or processor register is one of a small set of data holding places that are part of the…

Q: 3) Assume SS=5000H, DS=6000H, ES=7000H, CS=9000H, BX-1000H, DI=2000H, BP=3000H, IP=4000H, SI=2000H,…

A: Given: We are given various registers with values stored in them. Register such as SS, DS, ES, CS,…

Q: 2. The following instructions are executed on a CPU which has R = 23 and PC = 10 for each…

A: ANSWER:-

Q: Q3/ Design a machine with a byte addressable main memory of 216 bytes and block size of 8 byte.…

A: Given that, Size of main memory= 216 bytes Block size= 8 bytes Number of lines= 32

Q: Q1\ Suppose 8086 microprocessor perform the following task: ADD AX, 3FF2H Where the value of AX is…

A: The flag register has following: Status Flag Sign (S) Parity (P) Zero (Z) Overflow (O) Auxiliary…

Q: 6. Assume you have an instruction cache miss rate of 2%, and a data cache miss rate of 6%. The miss…

A: We have to calculate the actual CPI using the below data. Given data, I-cache miss rate = 2% D-cache…

Q: For sub $rd, $rs, $rtReg[rd] = Reg[rs] + Reg[rt] - Which resources (blocks) perform a useful…

A: Answer:)

Q: 11. Which of the following is not a form of memory ? a. Instruction cache b. Instruction register c.…

A: c) Instruction opcode

Q: b) Sketch a diagram showing that the data transfer from CPU to memory/ from memory to CPU including…

A: The соmрuter dоes its рrimаry wоrk in а раrt оf the mасhine we саnnоt see, а соntrоl…

Q: 2. Consider the initial value of register Stia Ox12345678 and the content of memory location…

A: Consider the initial value of register $t1 is 0x12345678 and the content of memory location…

Q: (B)- Choose the correct answer for the following questions (Choose FIVE Only) 1. Assume AL register…

A: 1) Ans:- Option c Assume AL register 7FH, it would become 81H after executed NEG AL instruction. 2)…

Q: 13/Assume that the microprocessor can directly address 64K with a and 8 data pins The memory m or…

A: Lets see the solution.

Q: 7. (a) How is it possible to store data at address 000H even program instruction is residing at the…

A: Given question has asked how is it possible to store both data and program instruction at same…

Q: PROBLEM STATEMENT- WRITE/STORE 10 NUMBERS IN THE MEMORY STARTING FROM ANY 16 BIT ADDRESS (E.G 2000…

A:

Q: 7-1. *The following memories are specified by the number of words times the number of bits per word.…

A: Here memories are specified as number of words and number of bits per word. We know that for address…

Q: We want to build a word organized main memory of 8 GB for a 32-bit CPU architecture composed of word…

A: Solution:: Let's see the direct answer for the above question first then will see the basic part…

Step by step

Solved in 2 steps with 1 images

- If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the fetch cycle is 40% of the processor cycle time, what memory access speed is required to implement load operations with zero wait states and load operations with two wait states?Suppose a computer using fully associative cache has 4G bytes of byte-addressable main memory and a cache of 512 blocks, where each cache block contains 128 bytes. a) How many blocks of main memory are there? b) What is the format of a memory address as seen by the cache, i.e., what are the sizes of the tag and offset fields? c) To which cache block will the memory address 0x018072 map?1. T/F - if (B)=006000 (PC)=003600 (X)=000090, for the machine instruction 0x032026, the target address is 003000.2. T/F – PC register stores the return address for subroutine jump.3. T/F – S register contains a variety of information such as condition code.4. T/F – INPUT WORD 1034 – This means Operating system should reserve 1034 bytes in memory5. T/F - In a two pass assembler, adding literals to literal table and address resolution of local symbol are done using first pass and second pass respectively.

- Suppose a computer using direct mapped cache has 4M byte of byte-addressable main memory, and a cache of 512 blocks, where each cache block contains 64 bytes. a) How many blocks of main memory are there? b) What is the format of a memory address as seen by the cache, i.e., what are the sizes of the tag, block, and offset fields? c) To which cache block will the memory address 0x00007266 map?Suppose a computer using fully associative cache has 220 words of main memory and a cache of 128 blocks, where each cache block contains 16 words. (a) How many blocks of main memory are there? (b) What is the format of a memory address as seen by the cache, that is, what are the sizes of the tag and word fields? (c) To which cache block will the memory reference 01D872_{16} map?Please solve Q) which is a valid offset pair? A) DS:DI C) ES:SI B) CS:SP D) SS:BP Q) The number of General Purpose Registers present in 8086 microprocessor? 6 10 34 4 Q) With 20-bit address lines memory size of microprocessor would be? Q) Calculate the physical address of the segment offset pair 7213:5686 77686H 0C899H 777B9H 777B6H Q) ALU of 8086 is 20 bit 8 bit 16 bit 32 bit Q) Memory size of 8086 microprocessor is 4KB 256 bytes 128bytes 1MB Q) In 8086 data access by which register uses SS as the default segment register? Both SP and BP SP Dl BP Q) Flag resister is None of the above 20 bit 16 bit 8 bit Q) The starting address of the segment is called None of the above Effective address Base address Offset address Q) Instruction queue size in 8086 is 4 bytes 4 bits 6 bytes 6 bits Q) MOV CX, [481d] ; assuming DS= 2162H, logical address will be: Q) AL= 53 CL=29 ADD AL, CL DAA What is the value of AL after…

- A computer is using a fully associative cache and has 216 bytes of main memory (byte addressable) and a cache of 64 blocks, where each block contains 32 bytes. a. How many blocks of main memory are there? b. What will be the sizes of the tag, index, and byte offset fields? c. To which cache set will the memory address 0xF8C9(hexadecimal) map?Suppose that a 64M x 16 main memory is built using 512K × 8 RAM chips and memory is word-addressable. a) How many RAM chips are necessary?b) If we were accessing one full word, how many chips would be involved?c) How many address bits are needed for each RAM chip?d) How many banks will this memory have?e) How many address bits are needed for all of memory?f) If high-order interleaving is used, where would address 32(base 10) be located? (Your answer should be "Bank#, Offset#")g) Repeat (f) for low-order interleaving.Show how the following values would be stored by byteaddressable machines with 32-bit words, using little endian and then big endian format. Assume that each value starts at address 10 . Draw a diagram of memory for each, placing the appropriate values in the correct (and labeled) memory locations.Q.) 0x0000058A

- Consider the following instruction:Instruction: Add Rd, Rs, RtInterperation: Reg[Rd] = Reg[Rs] + Reg[Rt] RegWrite MemRead ALUMux MemWrite ALUOp RegMux Branch a, What are the values of control signals generated by the control in Figure 4.2 for the above instruction? b, Which resources (blocks) perform a useful function for this instruction? c, Which resources (blocks) produce outputs, but their outputs are not used for this instruction? d, which resources (blocks) produce no output for this instruction?Suppose a computer using direct mapped cache has 2^32 bytes of byte-addressable main memory, and a cache size of 512 bytes, and each cache block contains 64 bytes. a) how many blocks of main memory are there? b) what is the format of a memory address as seen by cache, i.e., what are the sizes of the tag, block, and offset fields? c) to which cache block will the memory address 13A4498A map?Consider a processor that uses a 48-bit virtual memory address. The main memory installed onthe system is 4GB. Page size is set to be 32KB. Determine the following:I. Address space of virtual memory and physical memory. II. Total Number of virtual pages and the total physical pagesIII. How many bits are necessary to store (i) Page Table entry and (ii) TLB entry, consideringthe TLB entry stores valid, reference and dirty bits.IV. What is the size of the page table? And how many pages of memory is needed to storethe entire Page table? What fraction of physical memory is needed to store the entirepage table?