Single-cycle MIPS Architecture 1. Assume that core components of single-cycle processor (shown below) have the following latencies: I-Mem 40ps Adder 50ps Мих 20ps ALU 100ps Regs Rd/Wr 80ps/60ps D-Mem Sign-Extend Shift-Left-2 20ps 200ps 20ps Single-cycle processor data path: |25-0 p-26 [25-21 Red Reg 1 Read Rey 2 CLK- 20-16 Addr Data Read Wte Reg Cache MEM Read Wte De Read Dea Register Fe Wre RegWrite RegD Brancs (15-0 Sign End DCache D-Mem ALU control ALUSre Contrel atye Memtokeg Memlead ump Suppose that this data path executes only two types of instruction: sub $rd, $rs, $rt lw $rt, offset($rs) What would be the clock period to correctly execute the two instructions on the above single-cycle processor? Assume that PC register doesn't take any latency (i.e. Propagating a new PC valuc to I-Cache/I-Mem docsn't take any cycle).

Single-cycle MIPS Architecture 1. Assume that core components of single-cycle processor (shown below) have the following latencies: I-Mem 40ps Adder 50ps Мих 20ps ALU 100ps Regs Rd/Wr 80ps/60ps D-Mem Sign-Extend Shift-Left-2 20ps 200ps 20ps Single-cycle processor data path: |25-0 p-26 [25-21 Red Reg 1 Read Rey 2 CLK- 20-16 Addr Data Read Wte Reg Cache MEM Read Wte De Read Dea Register Fe Wre RegWrite RegD Brancs (15-0 Sign End DCache D-Mem ALU control ALUSre Contrel atye Memtokeg Memlead ump Suppose that this data path executes only two types of instruction: sub $rd, $rs, $rt lw $rt, offset($rs) What would be the clock period to correctly execute the two instructions on the above single-cycle processor? Assume that PC register doesn't take any latency (i.e. Propagating a new PC valuc to I-Cache/I-Mem docsn't take any cycle).

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 3PE: Processor R is a 64-bit RISC processor with a 2 GHz clock rate. The average instruction requires one...

Related questions

Question

Transcribed Image Text:Single-cycle MIPS Architecture

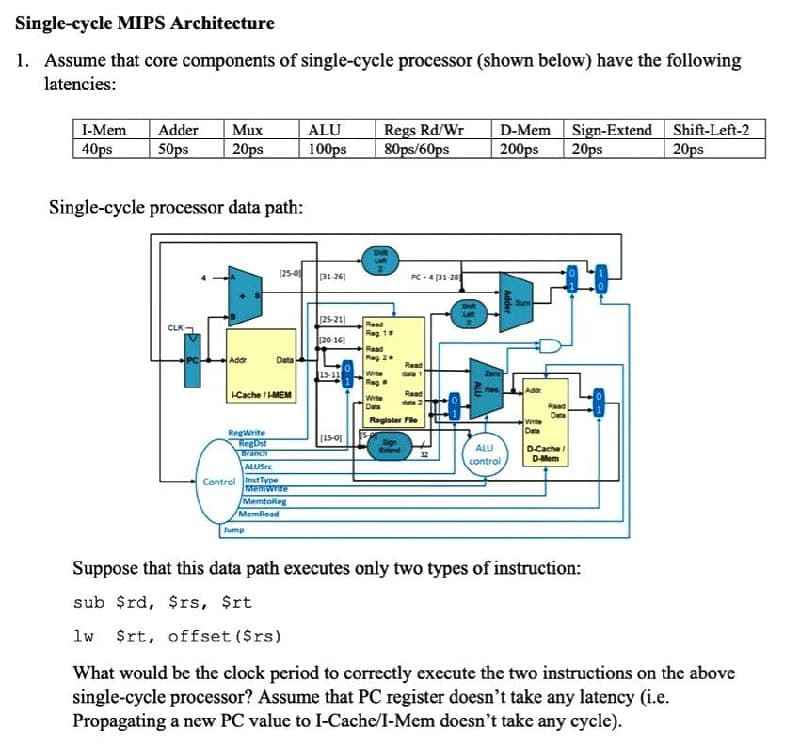

1. Assume that core components of single-cycle processor (shown below) have the following

latencies:

I-Mem

40ps

Adder

50ps

Mux

20ps

ALU

100ps

Regs Rd/Wr

80 ps/60ps

D-Mem Sign-Extend Shift-Left-2

20ps

200ps

20ps

Single-cycle processor data path:

125-0

[31-26

PC- 4 (11-2

Sum

25-21

CLK

Read

Reg 11

20-16

Read

Reg 2

Addr

Data

Read

15-31

Wte

Reg

Addr

Cache HMEM

Wte

Deta

Read

data 2

Read

Data

Register Fle

Wrte

Data

Regwrite

(15-0)

RegDs!

Branch

ALU

DCache

D-Mem

End

12

control

ALUSre

Contrel Inst Type

MemtoReg

Memlead

Jump

Suppose that this data path executes only two types of instruction:

sub $rd, $rs, $rt

lw $rt, offset ($rs)

What would be the clock period to correctly execute the two instructions on the above

single-cycle processor? Assume that PC register doesn't take any latency (i.e.

Propagating a new PC value to I-Cache/I-Mem docsn't take any cycle).

Adder

ALU

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 3 steps with 2 images

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning