6. Fill in the table below, assuming each instruction can impact the subsequent instructions. instruction destination result value source value addl %ecx.(%eax) sarl 2, %ebx leal 4(%eax,%edx,4),%esi movl %eax, %ebx movl (%eax), %edi

6. Fill in the table below, assuming each instruction can impact the subsequent instructions. instruction destination result value source value addl %ecx.(%eax) sarl 2, %ebx leal 4(%eax,%edx,4),%esi movl %eax, %ebx movl (%eax), %edi

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 15VE: A(n) ________________ instruction always alters the instruction execution sequence. A(n)...

Related questions

Question

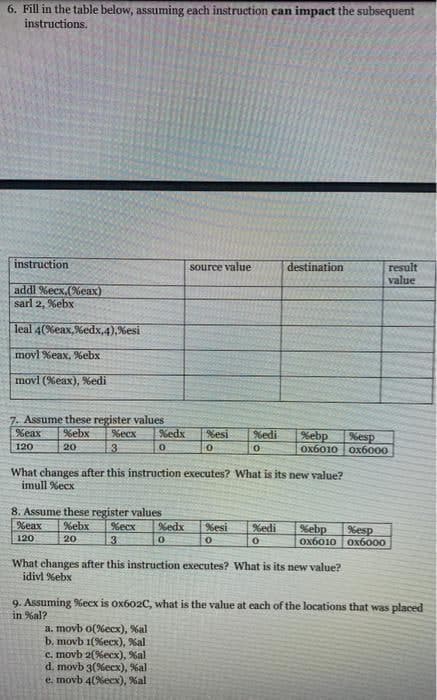

Transcribed Image Text:6. Fill in the table below, assuming each instruction can impact the subsequent

instructions.

instruction

destination

result

value

source value

addl %ecx,(%eax)

sarl 2, %ebx

leal 4(%eax, %edx,4), %esi

movl %eax, %ebx

movl (%eax), %edi

7. Assume these register values

%ecx

3

%eax

%ebx

%edx

%esi

%edi

Xebp

%esp

120

20

Ox6010 ox6000

What changes after this instruction executes? What is its new value?

imull %ecx

8. Assume these register values

%ebx

%eax

120

%ecx

%edx

%esi

%edi

%ebp

%esp

20

Ox6010 ox6000

What changes after this instruction executes? What is its new value?

idivl %ebx

9. Assuming %ecx is ox602C, what is the value at each of the locations that was placed

in %al?

a. movb o(%ecx), %al

b. movb 1(%ecx), %al

c. movb 2(%ecx), %al

d. movb 3(%ecx), %al

e. movb 4(%ecx), %al

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 3 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning