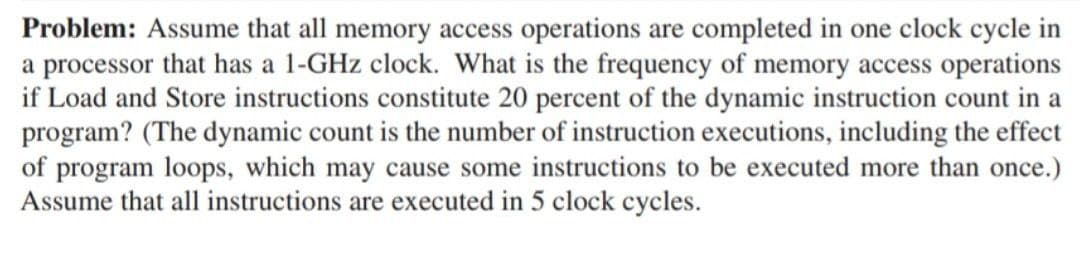

Problem: Assume that all memory access operations are completed in one clock cycle in a processor that has a 1-GHz clock. What is the frequency of memory access operations if Load and Store instructions constitute 20 percent of the dynamic instruction count in a program? (The dynamic count is the number of instruction executions, including the effect of program loops, which may cause some instructions to be executed more than once.) Assume that all instructions are executed in 5 clock cycles.

Q: More registers appear to be a good thing, in terms of reducing the total number of memory accesses a…

A: Consider the statement, Sum = (A + B) - (C + D)

Q: Problem 3: If we assume a CPU can process 100000 Instruction/sec. Compute the CPU utilization in the…

A: CPU Utilization is the percentage of instructions currently executing divided by total number of…

Q: a- Find the total execution time for the program on 1,2,4, and 8 processors, and show the relative…

A:

Q: Compilers can have a profound impact on the performance of an application. Assume that for a…

A: NOTE Below is the answer for the given question. Hope you understand it well. If you have any…

Q: Computers Problem 3. Suppose you wish to run a program P with 7.5 billion instructions on a 5GHZ…

A: The Answer is in Below Steps

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 x 106 INT instructions,…

A: The answer is...

Q: 2- Show how each of the following MIPS instructions is converted into machine code. Assume the…

A: Answer:- Solution: Conversion of machine code to MISP can done by following below steps…

Q: Assume for a given program, 60% of the executed instructions are of Class A, 10% are of Class B, and…

A: Class A Instructions = 60% = 0.6 Class B Instructions = 10% = 0.1 Class C Instructions = 30% =…

Q: Answer the following questions. A. A computer system has a main memory access time as 60ns. you as a…

A: ANSWER:-

Q: Consider the following assembly code: Instruction Description LD R1, 45(R2) Read data from memory…

A: the answer is given below :

Q: (c) The process of fetching the next instruction when the present instruction is being executed is…

A: There are two ways to boost a CPU's performance:1) Introduce quicker circuits into the hardware.2)…

Q: 1. On the following instructions, there are 6-lines of assembly code, along with space for the…

A: a. Identify the instruction type(R/I/J) b. Break the space into the proper fields

Q: 2- Show how each of the following MIPS instructions is converted into machine code. Assume the…

A: Actually, given question regarding MIPS instructions.

Q: 14- Change the content of memory location [300h] to FFh without using MOV instruction. Use just one…

A: Algorithm : Move 300h into CX register Move CX into DS segment (now we are in 300h data segment)…

Q: (a) An instruction at address 021 in the basic computer has I=0, an operation code of the AND…

A: Answer

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 × 106 INT instructions,…

A: the answer is....

Q: 3. Performance evaluation ( Assume for a given program, 60% of the executed instructions are…

A:

Q: 3.2 What is the average number of penalty cycles per instruction?

A: - Given the miss penalty : 20 cycles per miss TLB miss rate : 1% I cache miss rate : 5% D cache…

Q: Assume for a given processor the CPI of arithmetic instructions is 1, the CPI of load/store…

A: Hence, It is NOT a good choice. I Type I Count (M) CPI Cycles Arithmetic 375 1 375…

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 × 106 INT instructions,…

A: The answer is...

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 × 106 INT instructions,…

A: the answer is...

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 x 106 INT instructions,…

A: The answer is...

Q: (b) For the following code, draw the resulting memory diagram. ; Main Program, Start 1000H:200H…

A: Answer: I have given answer in the brief explanation.

Q: b. i. Using a detailed state diagram, explain how the instruction cycle can be expanded including…

A: Given data: An instruction is stored at memory address 100. Assume that the address field of…

Q: 8. For a single cycle processor, the instruction breakdown of a program is listed as following. add…

A: The above question is answered in step 2:-

Q: Q3 Assume the following latencies for a single-issue processor. Instruction Producing Result FP…

A: Answer: I have given answered in the handwritten format in brief explanation

Q: Consider the following assembly code: Instruction Description LD R1, 45(R2) Read data from memory…

A:

Q: 1.14 Assume a program requires the execution of 50 x 106 FP instructions, 110 x 106 INT…

A: The answer is...

Q: 2. Two word-wide unsigned integers are stored at the physical memory addresses 00A0016 and 00A0216,…

A: Two word-wide unsigned integers are stored at the physical memory addresses 00A0016 and 00A0216,…

Q: Rearrange the following code to minimize the total number of cycles, assuming that a dependent…

A: Given Set of Instructions : Load r1, 64 (r2) Add r2, r2, r2 Sub r3, r4, r1 Load r4, 32 (r4)

Q: 5-Consider a computer running a program that requires 400 s, with 80 s spent executing FP…

A: I solved only one question according to Bartleby policy.

Q: 2-Two word wide unsigned integers are stored at the physical memory addresses 00A00 and 00A02,…

A: Given two unsigned integers stored at the physical memory address 00A00 and 00A02. Need to write…

Q: An instruction at address 021 in the basic computer has I = 0, an operation code of the AND…

A: According to the information given:- We have to follow the instruction to determine over the…

Q: The condition known as orthogonality arises when the design of an instruction set includes a…

A: The CPU is required to perform the following tasks: The programme is executed using the code.

Q: staps Consider a computer which has a memory which is capable of storing 4096 K words and each word…

A: It is defined as the operation field of an instruction specifies the operation to be performed. This…

Q: 3. Performance evaluation Assume for a given program, 60% of the executed instructions are…

A:

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 x 106 INT instructions,…

A: The answer is

Q: Assume that a computer architect has already designed 6 two-address and 24 zero-address instructions…

A: Given:Instruction length = 11 bits = 211 = 2048 bitsAddress register size = 4 bits5 two-address…

Q: 3. The following table shows the number of instructions for a program. ARITH STORE LOAD BRANCH TOTAL…

A: The Answer is in below Steps

Q: (c) Assume 80% of instruction fetch operations are completed in one clock cycle and 20% are…

A:

Q: Suppose that the following clock cycles per instruction, and frequencies of usage by a particular…

A: Here the table is given for the instructions and their frequency and the number of cycles. We will…

Q: Question 2: Problem Solving Suppose that you have a computer with a memory unit of 24 bits per word.…

A: Answer :

Q: a) In a computer instruction format, the instruction length is 11 bits and the size of an address…

A: a) Given information: Instruction length = 11 bits = 211 = 2048 bits Address register size = 4 bits…

Q: 1. Develop a mathematical model for measuring performance based on overall memory access time with a…

A: check further steps for the answer :

Q: 2- Show how each of the following MIPS instructions is converted into machine code. Assume the…

A: Conversion of machine code to MISP can done by following below steps Step 1: Conversion of Hex code…

Q: Microprocessors Fill in the following blanks with appropriate answers 4. If there is a carry from…

A: Q4 Auxiliary carry is the right answer This is because the BCD number system use auxiliary flag…

Q: Instead of a single-cycle organization, we can use a multi-cycle organization where each instruction…

A: The solution for the given question is given in the following step.

Q: isters. The computer supports instructions, where each instruction consists of following fields: •…

A: We are given memory size, number of registers, and number of addressing modes. Also, the field in…

Q: 1.14 Assume a program requires the execution of 50 x 106 FP instruction 110 x 106 INT instructions,…

A: The answer is

Q: 2) COMP1, COMP2, COMP3 and COMP4 are different types of general register computers using 3, 2, 1 and…

A: a) Write a program to evaluate these equations (all 3 of them sequentially together) for…

If you don't knowledge skip it.. Don't reject this.. Do fast thanks..

Trending now

This is a popular solution!

Step by step

Solved in 2 steps with 1 images

- 1. In this exercise we examine in detail how an instruction is executed in a single cycle datapath. Problems in this exercise refer to a clock cycle in which the processor fetches the following instruction word: 10001100101001100000000000111000 Assume that the data memory is all zeros and that the processor’s registers have the following values at the beginning of the cycle in which the above instruction word is fetched: R0 R1 R2 R3 R4 R5 R6 R8 R12 R3 1 0 1 -2 4 -6 4 -10 -12 -14 31 a. What are the outputs of the sign-extend and the jump “Shift-Left-2” (near the top of the following Figure) for this instruction word? b. What are the values of ALU control unit’s inputs (ALUOp and Instruction operation) for this instruction? c. For the ALU and the two add units, what are their data input values? ALU Add (PC+4) Add (Branch) Input#1 Input#2 Input#1 Input#2 Input#1 Input#2Assume for arithmetic, load/store, and branch instructions, a processor has CPIs for 1, 12, and 5respectively. Also assume that on a single processor a program requires the execution of 2.56*10^9arithmetic instructions, 1.28*10^9 load/store instructions, and 256 million branch instructions. Assumethat each processor has a 2GHz clock frequency. Assume that, as the program is parallelized to run overmultiple cores, the number of arithmetic and load/store instruction per processor is divided by 0.7xp(where p is the number of processors) but the number of branch instructions per processor remains thesame. a- Find the total execution time for the program on 1,2,4, and 8 processors, and show the relativespeedup of the 2,4, and 8 processor result relative to single processor result. b- If the CPI of the arithmetic instruction was doubled, what would be the impact be on theexecution time of the program on 1,2,4, and 8 processors? c- To what should the CPI of load/store instructions be…Assume that the operation times of one add instruction for the major functional units are 325 ps for memory access, 185 ps for ALU operations and 125 ps for register file read/writes. Please fill the table first and perform the following a )What is the total cycle in single-cycle implementation? b )What is the total cycle in pipelining implementation? c) What is the total cycle in pipelining implementation if there are 5 million add instructions? d) What is the total cycle in pipelining implementation for 5 million add instructions, if the stages are balanced? e)What is the speed up of pipelining implementation over single-cycle implementation?

- Assume that a program requires the execution of 125x106 FP (floating point) instructions, 130x106 INT (integer) instructions, 150x106 L/S (load/store) instructions, and 110x106 branching instructions. These instructions have CPIs of 1, 1, 8 and 4, respectively. Assume that the processor has a 5 GHz clock rate. a. Is it possible to run the program twice as fast if we improve the CPI of just the L/S instructions? If so, by how much? Show your calculations. b. What is the Speedup in the execution time of the entire program if the CPI of INT and FP instructions is reduced by 40% and that of L/S and branching instructions is reduced by 50%?The importance of having a good branch predictor depends on how often conditional branches are executed. Together with branch predictor accuracy, this will determine how much time is spent stalling due to mispredicted branches. In this exercise, assume that the breakdown of dynamic instructions into various instruction categories is as follows: R-Type BEQ JMP LW SW 40% 25% 5% 25% 5% Also, assume the following branch predictor accuracies: Always - Taken Always - not - taken 2-bit 40% 60% 75% 1.1 Stall cycles due to mispredicted branches increase the CPI. What is the extra CPI due to mispredicted branches with the always-taken predictor? Assume that branch outcomes are determined in the EX stage, that there are no data hazards, and that no delay slots are used. 1.2 Repeat 1.1 for the “always-not-taken” predictor. 1.3 Repeat 1.1 for the 2-bit predictor. 1.4 With the 2-bit predictor, what speedup would be achieved if we could convert half of the branch instructions in a way…- Compilers can have a profound impact on the performance of an application.Assume that for a program, compiler A results in a dynamic instruction count of1.0 × 109 and has an execution time of 1.15 s, while compiler B results in adynamic instruction count of 1.2 × 109 and an execution time of 1.56 s.a) Find the average CPI for each program given that the processor has aclock cycle time of 1 ns.b) Assume the compiled programs run on two different processors. Ifthe execution times on the two processors are the same, how muchfaster is the clock of the processor running compiler As code versusthe clock of the processor running compiler B’s code?

- (15pt) Assume that instruction cache miss rate is 2%, data cache miss rate is 10%, CPI (clock cycle per instruction) is 2 without any memory stall, and miss penalty is 100 cycles. In addition, assume that the frequency of loads/stores is 30%. (a) Compute CPI with memory stall. (b) When CPI without any memory stall becomes 1, compute CPI with memory stall. (c) If the CPU clock rate is doubled with the same memory when CPI without memory stall is 2, compute CPI with memory stall.Consider a HW ISA program P1 with the following Instruction Memory IM: a. fill in the execution table for program P1 using the IM. Use the same notational conventions used in the example execution table for P0 below. Any numbers beginning with 0x will be interpreted as hexidecimal; any numbers not beginning with 0x will be interpreted as decimal. b. Show the final values of the registers R2, R3, and R4 when the program execution halts. Again, any numbers beginning with 0x will be interpreted as hexidecimal; any numbers not beginning with 0x will be interpreted as decimal.1. We wish to compare the performance of two different machines: M1 and M2. The following measurements have been made on these machines: Program Time on M1 Time on M2 1 10 seconds 5 seconds 2 3 seconds 4 seconds Which machine is faster for each program, and by how much? 2. For M1 and M2 of problem 1, the following additional measurements are made:. Find the instruction execution rate (instructions per second) for each machine when running program 1. Program Instructions executed on M1 Instructions executed on M2 1 200 x 106 160 x 106 3. For M1 and M2 of problem 1, if the clock rates are 200 MHz and 300 MHz, respectively, find the CPI for program 1 on both machines using the data provided in problems 1 and 2. 4. You are going to enhance a machine, and there are two possible improvements: either make multiply instructions run four times faster than before or make memory access instructions run two times faster than before. You…

- The importance of having a good branch predictor depends on how often conditional branches are executed. Together with branch predictor accuracy, this will determine how much time is spent stalling due to mispredicted branches. In this exercise, assume that the breakdown of dynamic instructions into various instruction categories is as follows: Also, assume the following branch predictor accuracies: Stall cycles due to mispredicted branches increase the CPI. What is the extra CPI due to mispredicted branches with the always-taken predictor? Assume that branch outcomes are determined in the EX stage, that there are no data hazards, and that no delay slots are used. b. With the 2-bit predictor, what speedup would be achieved if we could convert half of the branch instructions in a way that replaces a branch instruction with an ALU instruction? Assume that correctly and incorrectly predicted instructions have the same chance of being replaced.In a register/memory type CPU, the instruction lengths are typically variable. This presents a problem when the program is incremented during the Fetch-Decode-Execute cycle. What statements(s) is/are NOT TRUE with regard to Program Counter (PC) incrementing? Select one or more A. The binary loader overcomes the problem by positioning instructions at word boundaries so that PC can be calculated. B . PC is incremented by the largest possible foxed value, irrespective of the variability of the instruction C. Increment value is known when the current instruction has completed execution. D. increment value is known when the current instruction is decoded with the Instruction Register (IR) E. PC incrementing method is implementation dependent4.19.16: [5] <COD §4.6>. In this exercise, we examine how pipelining affects the clock cycle time of the processor. Problems in this exercise assume that individual stages of the datapath have the following latencies: Also, assume that instructions executed by the processor are broken down as follows: (a) What is the clock cycle time in a pipelined and non-pipelined processor? (b) What is the total latency of an lw instruction in a pipelined and non-pipelined processor? (c) If we can split one stage of the pipelined datapath into two new stages, each with half the latency of the original stage, which stage would you split and what is the new clock cycle time of the processor? (d) Assuming there are no stalls or hazards, what is the utilization of the data memory? (e) Assuming there are no stalls or hazards, what is the utilization of the write-register port of the "Registers" unit? No hand written and fast answer with explanation