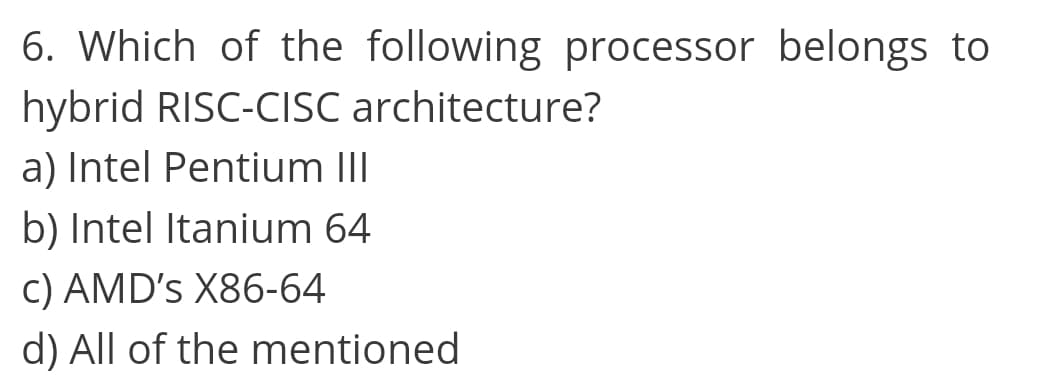

6. Which of the following processor belongs to hybrid RISC-CISC architecture? a) Intel Pentium II b) Intel Itanium 64 c) AMD's X86-64 d) All of the mentioned

Q: write in brief details about each of the following specification of the CPU. laptop details are as…

A: The ask is to provide the below specifications for core is i7 8750H 8th generation, its has 64 bits…

Q: 1- Which of the following instructions can't be COueu II 8086 assembly language? Give the reason.…

A:

Q: Question 2: Answer each of the following 1) The memory locations 1000, 1001, and 1004 have data…

A: The question is to write the output of the given assembly level instruction.

Q: Q1) If BX=1000, DS=0200, SS=0100, CS=0300 and AL=EDH, for the following instruction: MOV [BX] +…

A: Given Values are:- BX= 1000, DS= 0200, SS=0100, CS=0300, AL=EDH The instruction is MOV [BX]+1234H,…

Q: Which of the following is true? 1. The 80/20 rule states that 80% of the instruction is executed and…

A: The con Neumann architecture is a digital computer architecture whose design is based on the concept…

Q: The CPU we are talking about today is intel core i7- 8750H 64 bit write in detail about the below…

A: The i7-8750H functions at 2.2 GHz with a TDP of 45 W and a turbo boost of up to 4.1 GHz. This chip…

Q: If the first instruction "LXI H, 1100H" is positioned at address 7000H in memory, at what address…

A:

Q: 3- The 8086 Processor has several control lines, in considering that. Explain the following: a.…

A: Main points about : It is 16 bit , N channel , HMOS(High Speed Metal Oxide) processor.It is 40 pin…

Q: 7. Suppose that. DS = 0200H, BX = 0300H, and DI = 400H Determine the memory address accessed by each…

A: Given data, DS= 0200H BX= 0300H DI= 400H To find :- Memory address for following instructions at…

Q: 2. a) List the internal registers in 8085 microprocessor, their abbreviations and lengths(bits) b)…

A: Give question is based on microprocessor 8085 and 8086

Q: a) How many bits does a processor need internally to address a 32M x 32 memory if the memory is word…

A: As per Bartleby guideline we can only provide only 3 subparts.

Q: 3. Our favorite program runs in 10 seconds on computer A, which has a 2 GHz clock. We are trying to…

A: GIVEN:

Q: 3. Our favorite program runs in 10 seconds on computer A, which has a 2 GHz clock. We are trying to…

A: Clock Rate of Computer A is 2 GHz i.e 2 x 109 Hz Process time = 10 seconds…

Q: where R1, R2, and R3 are CPU registers, (R1) is the content of R1, a, ß,7, and are the starting…

A: We have , For each operations of given instruction code segment has number of instructions are:-…

Q: 9- Design a simple memory of type RAM starting from address 0001 to 0110 with memory width is 8…

A: Actually, memory is used to stores the data.

Q: 1 a) Differentiate between Intel 8085 microprocessor and Intel 8086 microprocessor b) The 8085…

A: To answer the following question: a. Differentiate between Intel 8085 and 8086 micropocessor b. Name…

Q: Q3: The original contents of CX, AX, memory location Beta, and carry flag (CF) are FFE116, 11AB16,…

A: Answer: I have given answered in the handwritten format

Q: a. What is the address and size of num1 and num2? b. What is the address of the instruction…

A: As per bartleby guidelines, For multiple questions asked I am allowed to solve only first question.…

Q: Topic: Microprocessor Interfacing & Embedded System Please explain if it is true or false Q) 255…

A: Given: To tell whether statement is true or false. Q) The 8255 is a general-purpose programmable I/O…

Q: 11. a. Draw flowchart of IAS operation for the following pair of instructions located in address…

A: Answer: a) The flowchart of the instruction goes this way:

Q: The CPU we are talking about today is intel core i7- 8750H write in detail about the below given…

A: specifications : The i7-8750H operates at 2.2 GHz with a TDP of 45 W and a turbo boost of up to 4.1…

Q: 11.a) Discuss the sequencing of control signals for the following instructions. i) Load R1,10(R2)…

A: Answer 11.a Sequence control alludes to client activities and PC rationale that start, intrude, or…

Q: write in details about the following specification of the CPU. My laptop core is i7 8750H 8th…

A: Given: Laptop core is i7 8750H 8th generation 6 cores, its 64 bits and clock frequency is 2.20GHz.…

Q: To get the physical address from the logical address generated by CPU we use ____ . a. MAR b. MMU c.…

A: Task :- Choose the correct option for given question.

Q: 1. The segment addresses are assigned as 0000H to F000H and the offset addresses values are from…

A: According to Bartleby Guidelines we need to answer only 3 sub questions so I have answered first…

Q: Problem4: A microcomputer has the following memory map: 4100 to 410F I/O 2100 to 22FF RAM 0000 to…

A:

Q: Q3: The original contents of CX, AX, memory location Beta, and carry flag (CF) are FFE IAB16,…

A: It is defined as a flip flop. It indicates some condition produced by the execution of an…

Q: Which of the following is true? 1) the 80/20 rule states that 80% of the instructions is excutede…

A: 80/20 rule: 80/20 rule is also called as pareto principle, and this rule states that 20 % effort…

Q: Question 35 A processor running a program makes 100 accesses to memory addresses. 80% are to L1…

A: A processor running a program makes 100 accesses to memory addresses.80% are to L1 only,10% are to…

Q: Which one of the following statement is TRUE for microprocessor architecture? Von Newman…

A: INTRODUCTION: The von Neumann architecture, which is the foundation for practically all digital…

Q: 16. If the first instruction "LXI H, 1100H" is positioned at address 7000H in memory, at what…

A: Correct answer of above given question is Option(1) 7003H i.e next instruction is located at address…

Q: Assume that an Intel CPU has address bus 25-bits wide. What is the maximum addressable memory?…

A: Given: Intel CPU has address bus 25-bits wide .what is maximum addressable memory

Q: Question 1 Solution should use this website for solution Sim8085 - A 8085 microprocessor simulator…

A: The program to find 2's complement of 8 bit number is given below:-

Q: 3) Assume SS=5000H, DS=6000H, ES=7000H, CS=9000H, BX-1000H, DI=2000H, BP=3000H, IP=4000H, SI=2000H,…

A: Given: We are given various registers with values stored in them. Register such as SS, DS, ES, CS,…

Q: 5. How many bits are required to address a 4M X 16 main memory if a) main memory is byte…

A: Dear student, As per guidelines. I can do only first question with both subparts. Please repost your…

Q: Q1. Design the following memory devices using multiplexers and D flipflops. a) 2 Bytes (2…

A: 2 Bytes With 1 multiplexer (2 inputs, 1 selector) we can fetch data from 2 memory locations. 16…

Q: Q.1- Make the right choice for the followings: 1. 8086 processor could be interfaced with memory…

A: The 8086 is a 16 bit microprocessor. The total number of output that are (a) 64 M The 8086 have 20…

Q: Which of the following is not true about RISC processors? a) addressing modes are less b) pipelining…

A: The Answer to given question is given below:-

Q: 4 Assuming the following integers in memory: 3000 2000 1000 1000 100 10 And the following integers…

A: About leal instruction:

Q: (B)- Choose the correct answer for the following questions (Choose FIVE Only) 1. Assume AL register…

A: 1) Ans:- Option c Assume AL register 7FH, it would become 81H after executed NEG AL instruction. 2)…

Q: 1. How many bits are required to address a 8M × 16 main memory if a) Main memory is…

A: Below is the answer to above question. I hope this will be helpful for you..

Q: The register content for an Intel 8086 microprocessor is as follows: CS = 5000H, DS = 6000H, SS =…

A: Below i have answered:

Q: The Figure 1 below shows the Amdahl's law for multiprocessor (speedup vs. number of processors),…

A: - We need to select the correct analysis for the provided graph. - The options :: First option…

Q: 3. What are the high and low addresses of the memory ranges defined by each of the chip selects…

A: Actually, memory is used to stores the data\information.

Q: a) Main memory is byte addressable? b) Main memory is word addressable?

A: Given main memory : 1 M x 8 From given memory, total locations are 1M each location size = 8 bits

Q: Consider the following instruction : MOV CX,0001H What are the opcode, W bit and D bit in the above…

A: Solution:b) Given MOV CX, 0001H The opcode for MOV instruction is 100010 Now we are taking CX as a…

Q: The following equation was suggested both for cache memory and disk cache memory Ts = Tc + M* T,…

A: The Answer is

Step by step

Solved in 2 steps

- 4 Memory and Addressing Modes The state of the CPU and memory is represented by this diagram. ey Wemory Address | Value Value |0 [0 |1(0]|0|0(1]1 a) Value of A after execution of LDA #50D? b) Value of A after execution of LDA #50F? ©) Value of ¥ after execution of LOY $0D? d) Value of Y after LDY $(000F), X? ) Value of Y after LDY ($0F), X2 please show workings!Question 777 ele Subject: Microprocessors For the following instruction write the code in binary and in hex: addi x3, x23 and 9 (This means you must find th values of opcode and rs1 as well as all other relevant fields which may include: rs2, rd, immediate field, funct 3, funct 7, depending on the instruction type Full explain this question and text typing work only thanks25. The type of memory assignment used in Intel processors is _____ . a. Little Endian b. Big Endian c. Medium Endian d. None of the above

- A particular application has the following mix of instruction types: a) What percent of the instructions use data memory? b) What percent of instructions use instruction memory? c) What percentage of the instructions use all five stages (Fetch, Decode, ALU, Memory, Writeback) of instruction execution?We want to build a word organized main memory of 8 GB for a 32-bit CPU architecture composed of word organized memory modules of 30-bit address and 8-bit data buses each. a) Draw the interface of the main memory by clearly indicating the widths of the buses. b) Howmanymemorymoduleswouldbenecessarytobuildthememorysystem? c) Design the main memory internal organization built out of the above memory modules (use multiplexers and/or decoders as needed) by clearly indicating the widths of the used busses d) CanweusethismemorysystemasRAMfortheCPUinProblem1?Explainyouranswer.11. Which of the following is not a form of memory ? a. Instruction cache b. Instruction register c. Instruction opcode d. Both a and b

- 1. Please provide comments for the instruction 2. What is the memory mapped address for the console output and keyboard input? 3. Please identify the specific line of code that prints to console and reads the keystroke . I will rate you if u provide answers thanksMost Intel CPUs use the __________, in which each memory address is represented by two integers.1. Briefly explain the following terms used for Intel 8086 microprocessor with appropriateexample(s):a. PUSHb. POPc. Subroutines

- Computer Organization and ArchitectureAssignment Submit your work by uploading it in Blackboard or bringing it as a hard copy to my office by the deadline. Answer the following question:1-What is the datapath?2-What is the Instruction cycle?3-What is the memory hierarchy? 4-Give small description or example and indicate the format of the following MIPS functions:(The first two of them are examples) Please here is three columns one to instructions and two to format of instruction and three column is to description of function to all instructions but i don't copy to here only Please solve it. FormatFormatDescription lw $1,100($2)Iload word from $2+100 and put it in $1 and $1,$2,$3Gadd $2 and $3 and put the result in $1 | $1= $2+$3 Sw $1,100($2) la $1,label andi $1,$2,100 or $1,$2,100 srl $1,$2,10 li $1,100 move $1,$2 Beq $1,$2,100 Bne $1,$2,100 div $2,$3 Bgt $1,$2,100 addi $1,$2,100 addu $1,$2,$3Question 3 Suppose you have hardware that you are trying to improve by adding additional processors. The goal is to achieve a speed-up of 89 times faster, while being restricted to having .6% of the original computation remain sequential. How many additional processors should be added? (You don’t have to give a single number as the solution; just show an equation that will evaluate to the answer ....Answer only (e,f,g, h, i) questions. (e) List the elements of the execution unit.(f) What is the highest and the lowest address in the 8086’s memory address space.(g) Is memory in the 8086 microprocessor organized as byte, words or double words ?(h) What is the value of the double word stored in memory starting at address B000316 if the contents ofmemory location B000316, B000416, B000516 and B000616 are 1116, 2216, 3316 and 4416 respectively ?i) What is the function of the stack?