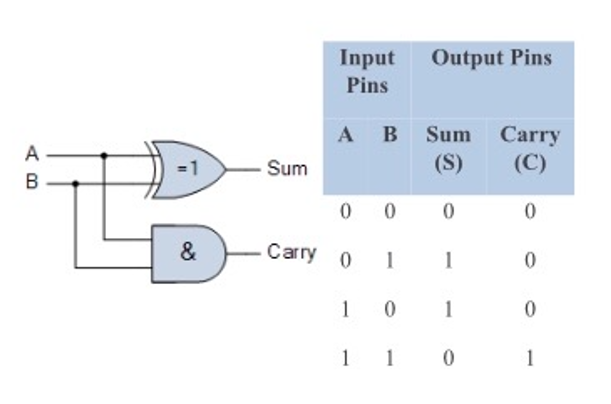

A logical circuit for a half adder performs addition on single bits. It produces two bits a sum (S) and a carry(C). Need to simulate the FSM for 8-bit adder sequential flip-flops Using C Programming.

A logical circuit for a half adder performs addition on single bits. It produces two bits a sum (S) and a carry(C). Need to simulate the FSM for 8-bit adder sequential flip-flops Using C Programming.

Chapter3: Data Representation

Section: Chapter Questions

Problem 9VE

Related questions

Question

A logical circuit for a half adder performs addition on single bits. It produces two bits a sum (S) and a carry(C).

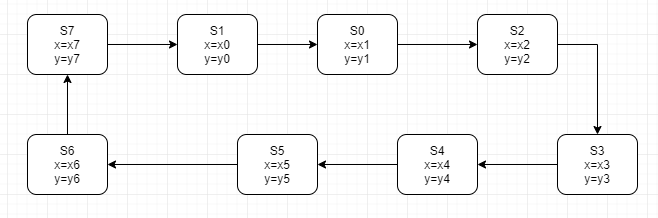

Need to simulate the FSM for 8-bit adder sequential flip-flops Using C

Transcribed Image Text:Input

Output Pins

Pins

A B Sum

(S)

Carry

(C)

A

Sum

0 0

&

Carry 0

1

1

1 0

1

1 1

1

Transcribed Image Text:一国一国一国

S7

S1

SO

S2

X=x7

X=x0

y=y0

X=x1

y=y1

y=y7

X=x2

y=y2

S6

S5

X=x5

X=x6

S4

S3

X=x4

y=y6

X=x3

y=y5

y=y4

y=y3

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by step

Solved in 4 steps with 13 images

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning