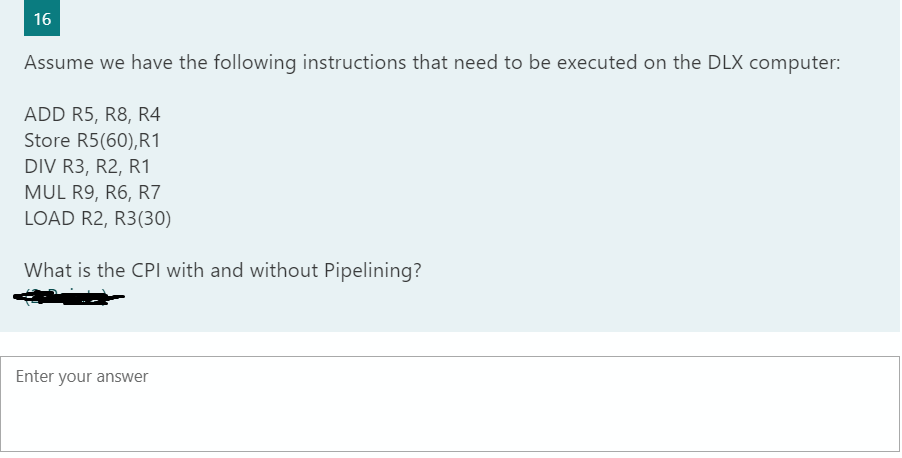

Assume we have the following instructions that need to be executed on the DLX computer: ADD R5, R8, R4 Store R5(60),R1 DIV R3, R2, R1 MUL R9, R6, R7 LOAD R2, R3(30) What is the CPI with and without Pipelining?

Q: Assume the following initial values of registers r1-r5: re= 0x0 r1= 0x0 r2= 0x0000000A r3=…

A: Please check the step 2 for solution

Q: a) What is the contents of AL, and CL registers after executing the following instruction sequence?…

A: Note : As per company guidelines, we can answer 1 question per post. Please repost other questions…

Q: For a given number of instructions, assume CPI is increased by 20%, and clock cycle time is…

A: The CPI is increased by 20%, so we can add 0.20 to CPI The clock cycle time is decreased by 20%, so…

Q: Question 3: please solution with explain What answer appears in memory locations 1200 hex to 1203…

A: According to our guidelines we can solve first one: ================================== Answer 3:…

Q: MOV DS.(202) MOV SI,[200] THESES SEQUENCE OF INSTRUCTIONS ARE EQUAL TO ONE INSTRUCTION WHICH IS…

A: Answer is in next step

Q: Identify the memory locations that are cleared by the following instructions. MVI B,00H LXI H,XX75H…

A: Required:- Also, verify your answer on sim8085 Identify the memory locations that are cleared by the…

Q: QUESTION 5 "Assuming: in a MIPS machine, all the memory locations have data -1; all the registers…

A: Answer is given below

Q: State the addressing mode and type of instruction based on no. of bytes and its operation for each…

A: Solution:-- 1)The given question is also related with an multiple choice question to be…

Q: 3.2 Write a program that contains two instructions: (1) add the number 5 to the EAX register, and…

A: Source Code: The code instructions are as follows: INCLUDE Irvine32.inc.codemain PROC ; consider the…

Q: Show all work and explain in detail for the following and assume: R0 contains 001A2F0B R1 contains…

A: LR instruction: Format: LR target_register, source_register This instruction is used to copy the…

Q: Given the following memory values and a one-address machine with an AC. Word 20 contains 40 • Word…

A: Qualities stacked by the directions: Consider the given words and the information appeared in the…

Q: The following instructions are executed on a CPU which has R= 23 and PC = 10 for each instruction.…

A: The Answer is

Q: After executing the following MIPS assembly instructions E ues remain in the registers $s0, $t0, $t2…

A:

Q: 2- Show how each of the following MIPS instructions is converted into machine code. Assume the…

A: Actually, given question regarding MIPS instructions.

Q: a) Determine the number of cycles to execute 175 instructions for non-pipelined processor and…

A: Hi, As per the QnA policy, we are allowed to solve the first three sub-parts of a multipart…

Q: Q2. In The following, the instructions are dependent on each other, if A = B8 H. and Cy 1, next to…

A:

Q: Compare and contrast AND and TEST instructions?

A: *As per the company norms and guidelines we are providing a first question answer only please…

Q: Assume that an LC-3 machine instruction "0011000000000110" is stored at address Ox3702, label A…

A: Solution:- Answer is (c) - ST RO,A

Q: A) Specify the contents of CPU registers that can be effected when the following program is…

A: Given program MOV DX,A000H MOV SS,DX MOV SP,01FBH MOV AX,04EAH MOV BX,8000H CMP AX,BX STI CLD PUSH F…

Q: 3. What is the result of executing the following instruction sequence? SUB AL , CL DAS Assume that…

A: We have 2 assembly instructions and we need to find the result of these commands. The instructions…

Q: 11. a. Draw flowchart of IAS operation for the following pair of instructions located in address…

A: Answer: a) The flowchart of the instruction goes this way:

Q: If memory accesses take 5 times more than register accesses, then a ST instruction will take machine…

A: Given:-

Q: h. What is the throughput of a 100 instruction program executing on a nonpipelined machine? i. What…

A: h) The throughput of a 100 instruction program executing on a nonpipelined machine throughput =…

Q: R-type I-type LDUR STUR CBZ B 24% 28% 25% 10% 11% 2% What fraction of all instructions…

A: What fraction of all instructions read from register file? Answer : 24% What fraction of all…

Q: 8. For a single cycle processor, the instruction breakdown of a program is listed as following. add…

A: The above question is answered in step 2:-

Q: question 3: please : solution with explain What answer appears in memory locations 1200 hex to 1203…

A: Solution: I am going to solve both the questions one by one with explanation.

Q: TASK#6: Perform the following debug activities ACT 1.1 :Use debug command U100 to un-assemble the…

A:

Q: Q3) Given the following MIPS Instructions: Memory address MIPS instruction 0x00403000 loop: add $a0,…

A: Address of label loop = 0x00403000Address of instruction bne $a0, $zero, loop is 0x00410000 Target…

Q: 6. (1) (Please explain why a branch delay slot is needed after a branch instruction. (2)) Please…

A:

Q: 2. For each of the highlighted load instructions below, determine the effective address of any…

A: ANSWER:-

Q: Category: CPU Wiring Look at the following (incomplete) diagram of the Hack CPU taken from figure…

A: The central processing unit (CPU) is an electronic machine that executes instructions, which are a…

Q: Microprocessor Hw Q1 Execute the following code and show the contents of the registers: LDI R16,$03…

A: A CPU or processor register is one of a small set of data holding places that are part of the…

Q: 3. Given the following memory values and a one- address machine with an accumulator and a register,…

A: The following instructions are given in binary:1. 0101 0000 0001 00002. 0101 0000 0001 01003. 0101…

Q: 3. The following table shows the number of instructions for a program. ARITH STORE LOAD BRANCH TOTAL…

A: The Answer is in below Steps

Q: Assume that before the instruction is executed, the flags are CF=1, ZF=0 and SF=0 and the Registers…

A: In given problem, we have some flags values and some register contents. We have to perform XOR…

Q: 2. Define Pipelining as related to improving processor performance, and then, calculate the number…

A: Given Data : Number of instructions = 5 Number of cycles per stage = 1 To find : Number of…

Q: (B)- Choose the correct answer for the following questions (Choose FIVE Only) 1. Assume AL register…

A: Q.1 = C Q.2= B Q.3= C

Q: To perform the actions of fetch and execute, all CPU are equipped with the following resources,…

A: This question comes from Digital Electronics which is a paper of Computer Science. Let's discuss it…

Q: The sum of the data, anti and output dependencies for the following sequence of instructions is 11:…

A: Introduction

Q: b) An 8051 subroutine is shown below: MOV RO, #20OH MOV @RO, #0 LOOP: INC RO CJNE RO, #80H,LOOP RET…

A: a) This subroutine is to clear the RAM locations 20H to 7FH b) total machine cycles: MC Bytes…

Q: Explain the meaning of the following instructions a. add 50,R1 b. ldr R5, 23 c. lar R2, 99 d. st R7,…

A: Content of register R1 is added to 50

Q: (b) Suppose that the following instructions are found at the given location in memory. Illustrate…

A: Below I have Provided the handwritten solution of the given question

Q: 2. Consider the initial value of register Stia Ox12345678 and the content of memory location…

A: Consider the initial value of register $t1 is 0x12345678 and the content of memory location…

Q: cs 218 assembly language Given the code fragment: lst dd 2, 3, 5, 7, 9 mov rsi, 4 mov eax, 1 mov…

A: eax will be 0x000E

Q: 2. What is the minimum number of MIPS assembly instructions needed to write if (a<b) then c = 1;…

A: 4

Q: 1. SP=F002H; after PUSH BX, what is the value of SP? _____________ (1 Mark) 2. BL=00, after…

A:

Q: Given the following sequence of instructions: R1 = X + 1 Y = R1 + R2 R1 = R2 + X Complete the…

A: STEP 1:- Given:- R1=X+1 Y=R1+R2 R1=R2+X

Q: Question 1 Suppose that on a given single cycle CPU it takes: • 40 nanoseconds to read a word from…

A: Note : as per company's guidelines we are supposed to answer only one question at a time in case…

Q: For the following machine specs: a. The 2-bus processor supports 10 instructions only: add, sub, Id,…

A: It is defined as the commands or programs written in machine code of a machine (computer) that it…

Q: Assume that D1=$6 Show the state of the machine (D1 and V) after executing the MC68K instruction:…

A: The MC68K program consist of two register groups user and supervisor. User programs executed in the…

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

- CPU is executing these sequences of instructions A, BEQ G, C, D, E. CPU tasks aredivided into 5 steps: Fetch(IM), Decode(Reg), Execute(ALU), DM(Memory), andREG(Write-back).Branch instructions are applied in the Memory(DM) stage.How many cycles will it take to finish it? Show it using a table.B) Define the following instructions properly. How many addresses the following instructions contains? PUSH BP INC CX OR BL, BH MOV BP, SP SUB SP, #345 (Subject: Computer ARchetecture)Q: Fill in the blanks: 1. Fast SRAM can be found in most CPU's called 2. When Ao and WR are activated then the signal is activated. 3. When DT/R signal is 0, then it's in mode. 4. The address range of memory mapped input/output is.. 5. If we have a main memory of N=16 and the size of the memory chip is 4 Kbyte, then the number of memory chips is............

- Computer Organization and ArchitectureAssignment Submit your work by uploading it in Blackboard or bringing it as a hard copy to my office by the deadline. Answer the following question:1-What is the datapath?2-What is the Instruction cycle?3-What is the memory hierarchy? 4-Give small description or example and indicate the format of the following MIPS functions:(The first two of them are examples) Please here is three columns one to instructions and two to format of instruction and three column is to description of function to all instructions but i don't copy to here only Please solve it. FormatFormatDescription lw $1,100($2)Iload word from $2+100 and put it in $1 and $1,$2,$3Gadd $2 and $3 and put the result in $1 | $1= $2+$3 Sw $1,100($2) la $1,label andi $1,$2,100 or $1,$2,100 srl $1,$2,10 li $1,100 move $1,$2 Beq $1,$2,100 Bne $1,$2,100 div $2,$3 Bgt $1,$2,100 addi $1,$2,100 addu $1,$2,$3Assume there are two secondary memory processes; wait for them to execute.In terms of phase one, the priority is high, while the other priority is low.Only one process can run at the same time in main memory.Explain how the CPU works on it. Can you explain the system that connects all CPU components?Q2: Choose the correct answer 1. Suppose that a system uses 32-bit memory words and its memory is built from 16 1M × 16 RAM chips. How large, in words, is the memory on this system? A) 8M B) 16M C) 32M D) 64M 2. The __________ converts machine instructions of 0s and 1s into control signals. A) microprogram B) control store C) microsequencer D) control unit 3. Memory that is accessed by searching for content is called: A) read only memory. B) erasable memory. C) associative memory. D) virtual memory. 4. Binary code that has addresses relative to the location where the operating system has loaded the program in memory is called _______________ code. A) loadable B) absolute C) relocatable D) movable 5. Which phase of a compiler generates syntax errors? A) Lexical analysis B) Syntax analysis C) Parsing D) Semantic analysis 6. Cache memory is typically positioned between: A) the CPU and RAM. B) the CPU and the hard drive. C) ROM and RAM. D) None of these is correct. i need it ASAP please…

- Multiple choice question OS uses a timer to prevent a process from hogging the CPU by: a. Send priviledge instruction to CPU b. ALL is correct. c. Re-setting the timer counter to regain access. d. Interrupting the computer after some time period.8 The process of deciding which process should use the CPU is called as _______________ a. Planning b. Transmitting c. Scheduling d. Switching Just answer without explanation pleaseWhen processing many instructions in parallel, how can the computer save the computational cycles that would otherwise be wasted? Explain what happened because of their behavior in the preceding statement.

- microprocessor 8086/8088 which one and how ? Assume the content of the segment register ES = ACEE H, the possible value for segment register CS= ? CS=B822H CS=A215H CS-ACEEH CS=2ED5HIf a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the fetch cycle is 40% of the processor cycle time, what memory access speed is required to implement load operations with zero wait states and load operations with two wait states?How does pipelining improve CPU efficiency? What’s the potential effect on pipelining’s efficiency when executing a conditional BRANCH instruction? What techniques can be used to make pipelining more efficient when executing conditional BRANCH instructions?