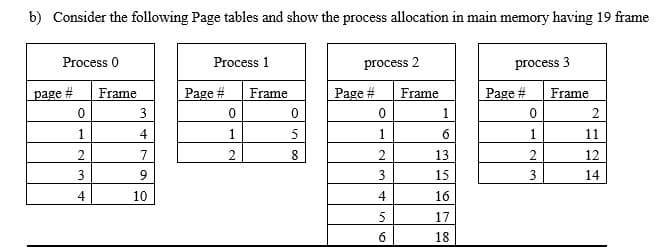

b) Consider the following Page tables and show the process allocation in main memory having 19 frame

Q: When is it ever necessary for a system to page its page table?

A: Paging : Paging is a process of memory management that eliminates the need for contiguous allocation…

Q: Following is a mapping of Logical Memory to Physical Memory using a Page Table. You are required to…

A: It is the data structure that is used by the virtual memory system in the OS of a computer in order…

Q: The following page reference changes occur during a given time interval. 4 2 0 1 2 5 1 4 0 2 3 5 7…

A: Page replacement algorithms are used in order to replace an existing page in the memory with a new…

Q: 15. Within a given virtual memory system, pages of varying sizes are used to avoid wasting space…

A: Question 15: In virtual memory system, a larger page size will cause more fragmentation hence…

Q: 1. Suppose a process page table contains the entries shown below. Using the format shown in Figure…

A: Over here we have asked how virtual memory mapped to physical memory.

Q: Suppose the page table for process B that is currently executed on the processor is as in Table 1.…

A: List the logical address ranges for each page. Given the following new ordered page…

Q: . Suppose we have 2 bytes of virtual memory and 28 bytes of physical main memory. Suppose the page…

A: Given: Virtual memory size=210 Physical memory size=28 Size of the page=24.

Q: Consider a system with 256Mbytes of main memory with page size of 4Kbytes. It has a logical address…

A: Answer: Given Main Memory 256Mbytes Page Size =4Kbytes and logical address=26 bits

Q: 21. Suppose we have 210 bytes of virtual memory and 28 bytes of physical main memory. Suppose the…

A: Virtual memory combines your computer%u2019s RAM with temporary space on your hard disk. When RAM…

Q: When would a system ever require the use of a page table for its page table?

A: Introduction: pageA page can be physical, memory, logical, or virtual.A page is a fixed-length…

Q: A computer system with paging-based memory management, whose architecture allows for a 4GB virtual…

A: According to the information provided in the initial question, we must determine the amount of space…

Q: How many bits are in a physical address?

A: There are 4 pages frames of size 64 each, or 22 x 26=28. So each physical address has 8 bits.

Q: a) Assuming a 1 KB page size, what are the page numbers and offsets for the following logical…

A: The answer is

Q: Following is a mapping of Logical Memory to Physical Memory using a Page Table. You are required to…

A: In this question, we have given logical memory and physical memory and we are asked about page table…

Q: Consider the virtual memory scheme using paging. The page size is 128 bytes. The entries in the page…

A: In this case, the machine is a 16-bit system with a 4KB page size and 64KB of physical memory.…

Q: a) Assuming a 1 KB page size, what are the page numbers and offsets for the following logical…

A: Question Asked:

Q: Assume we have 1 GB of physical memory. Inverted page table is used. Page size is 16 KB. Each entry…

A: In the inverted page table, indexing is done with respect to the frame number instead of the logical…

Q: Assuming a 4-KB page size (4096 bytes), what are the page numbers and offsets for the following…

A: page size= 4KB =4096B

Q: Based on the given paging model of logical and physical memory, draw a page table to show its…

A: Here in this question we have given a logical memory and physical memory.and we have asked to draw a…

Q: The effective access time in a virtual memory system depends on the TLB hit rate but does not depend…

A: TLB : TLB stands for Translation Lookaside Buffer. This is a fast memory like cache memory which…

Q: A process references five pages A, B, C, D and E in the following order, A, C, B, E, A, B, E, A, B,…

A: The Answer is

Q: 9. Consider a system that uses 32-bit addresses and page table structures as discussed in class. If…

A: 32 bits= 2^5 256 pages= 2^8

Q: Consider a 48-bit virtual address space. The system hierarchical paging. Therefore, the page table…

A: 1)P1 x 1 15/16" 3)8-bit

Q: Fill the table below using the direct mapping function (starting memory address of the block) of the…

A: ANSWER: Memory Address:

Q: Consider the following Page tables and show the process allocation in main memory having 19 frame…

A:

Q: If a system has Total Memory = 120 MB, Process memory= 60 MB, Frame Size = 4 MB What will be…

A: Actually, given information: Total Memory = 120 MB, Process memory= 60 MB, Frame Size = 4 MB

Q: 5. Given that (12, 17) is a record in the segment table of a process and the size of any segment of…

A: The answer is

Q: Suppose that an MMU has page table entries like the ones shown at right (formatted as in the slides…

A: The solution of the above question is:

Q: Consider the following Page tables: Process A : Page# Frame 0 3 1 4 2 8 3 10 Process B: Page…

A: Allocation of a given process (pages) in the main memory having 12 frames where A-process A,…

Q: b) Consider the following Page tables and show the process allocation in main memory having 19 frame…

A: Given:

Q: Consider a virtual memory system with a 50-bit logical address and a 38-bit physical address.…

A: A virtual memory system with a 50-bit logical address and a 38-bit physical address.Suppose that the…

Q: What is the primary advantage of using a two-level page table (instead of a one-level page table) in…

A: Two level paging means applying paging to page table. The 1st level page table includes information…

Q: Computer Science Given Page requests: Reference string: 4, 3, 4, 1, 2, 4, 1, 2, 3, 2, 1, 1 Show the…

A: Over here page fault is to be calculated for LFU and Aging algorithm (which is by default LRU but…

Q: (A) For each reference, list (i) its tag, index, and offset, (ii) whether it is a hit or a miss, and…

A: For Direct mapping of cache, Line no = block no mod(no of cache lines) Here, offset= 0-4 = 5 bits=32…

Q: assume we have 1 GB of physical memory. Inverted page table is used. Page size is 16 KB. Each entry…

A: Given, Physical Memory Size = 1 GB = 1.230 B…

Q: We design a 2-level page table scheme. The size of each page is 4K bytes. Given the 32-bit virtual…

A: Size of page = 4KB Now total number of pages = 232/212 = 220

Q: Assuming a 4-KB page size (4096 bytes), what are the page Numbers and offsets for the following…

A: As per guidelines I can answer only three sub-parts. Thank You. Page size: 4KB : 4096 bytes a) Page…

Q: Consider a system with 4-byte pages. A process has the following entries in its page table: logical…

A: Answer (a): An address of 32 corresponds to the byte that has the logical address of two. This is…

Q: How many frames will be created in memory?

A: 1. Page size is always equal to frame size so that one frame exactly fits into a page . So page size…

Q: Consider a system with 4-byte pages. A process has the following entries in its page table: logical…

A: We are given page size, page table and logical address and asked the physical address for it. First,…

Q: Assume variables have logical addresses with 16-bit page numbers and 16-bit offset using the memory…

A: The logical address is represented as combination of page number and page offset. physical address…

Q: Explain how a segment may be in the address space of two different processes at the same time.

A: Intro In paging systems, each method is assigned its page table, which establishes the mapping…

Q: Consider a system with 256Mbytes of main memory with page size of 4Kbytes. It has a logical address…

A: Below is the answer to above questions.

Q: a. Design a two-level page table (Suppose we need to fit each page table into a physical frame). b.…

A:

Q: Assume a memory subsystem with a cache of 8 blocks and a main memory of 64 blocks, where each block…

A: Given: Goal: We have to solve the above parts/questions given.

Q: Question 8: A CPU generates 32-bit virtual addresses. The page size is 4 KB. The processor has a…

A: Answer is

Q: Explain the function of the Page Map Table in all of the memory allocation schemes described in this…

A: To keep track of numerous work pages, memory management required a "page map table." It's a table in…

Q: Suppose a byte-addressable memory with 4 frames of size 8 bytes each and a paged virtual memory…

A:

Q: 1 6 2 8 3 10 Process B Page # Frame 0 3 1 4 2 9

A: Consider the following Page table: Process A Page # Frame 0 5 1 6 2 8…

Step by step

Solved in 2 steps with 2 images

- In the below figure look at Show the memoryallocation of process requests of size 90KB, 39KB, 27KB, 16KB and 36KB which will bereceived in order using:a) Best-Fit memory allocation methodb) Worst-Fit memory allocation method.Consider the following Page tables and show the process allocation in main memory having 19 frame Process 0 Process 1 process 2 process 3 page # Frame Page # Frame Page # Frame Page # Frame 0 3 0 0 0 1 0 2 1 4 1 5 1 6 1 11 2 7 2 8 2 13 2 12 3 9 3 15 3 14 4 10 4 16 5 17 6 186.plHeap memory management Show the memoryallocation of process requests of size 90KB, 39KB, 27KB, 16KB and 36KB which will bereceived in order using:a) Best-Fit memory allocation methodb) Worst-Fit memory allocation method.

- Consider the following Page tables: Process A : Page# Frame 0 3 1 4 2 8 3 10 Process B: Page Frame 0 5 1 6 2 7 Process C: Page Frame 0 0 1 1 2 2 3 9 4 11 Show the allocation of the above process (pages) in the main memory having 12 frames.Consider an operating system using memory mapping on a page basis and using a single level page table. Assume that the necessary page table is always in memory. The system takes 200 ns to make a memory reference, how long does a paged memory reference take? Group of answer choices 400 ns (nanoseconds) 809.2 ms (microseconds) 200 ns (nanoseconds) 1638.4 ms (microseconds)Consider a virtual memory system with a 50-bit logical address and a 38-bit physical address. Suppose that the page/frame size is 16K bytes. Assume that each page table entry is 4 Bytes. a. How many frames are in the systems? a.How many pages in the virtual address space for a process? b. If a single-level page table is deployed, calculate the size of the page table for each process c. Design a multilevel page table structure for this system to ensure that each page table can fit into one frame. How many levels is needed? Draw a figure to show your page systems;

- Consider the following Page table: Process A Page # Frame 0 5 1 6 2 8 3 10 Process B Page # Frame 0 3 1 4 2 9 Process C Page # Frame 0 0 1 1 2 2 3 7 4 11 Show the allocation of above process (pages) in the main memory having 12 frames.Question 4 Execute SRT for the following group of processes and complete the following table: Process A B C D E TArrival 0 2 4 6 8 Ts 2 3 5 1 4 TFinish Answer Answer Answer Answer Answer TR Answer  Answer  Answer  Answer  Answer  1. If the process arriving has the same remaining execution time as the process in the CPU, then the process that is using the CPU will have the highest priority. 2. If there is no process in the execution state and two or more processes have the shortest remaining time, then you will use the lowest PID criterion (using lexicographical order). Question 5 Execute HRRN for the following group of processes and complete the following table: Process A B C D TArrival 0 2 4 6 Ts 3 5 4 1 TFinish Answer Answer Answer Answer TR Answer  Answer Answer Answer  If two or more processes in the ready queue…Assume a process containing 5 pages with 1024 bytes per page and physical memory with 10 page frames. Frames and pages are of the same size. Given the following page map table (PMT): a) determine the physical address associated with the logical address of page 1, offset 100? b) what is the logical address associated with the physical address 2300? Please dont over complicate this question!!

- In a memory hierarchy, what is the underlying principle of caching?For two processes that each have a global variable global_int and share a variable shared_int, draw the virtual address space and the relevant page table mappings for each process and the physical address space.. Compare the memory organization schemes of contiguous memory allocation and paging with respect to the following issues:a. External fragmentationb. Internal fragmentationc. Ability to share code across processes