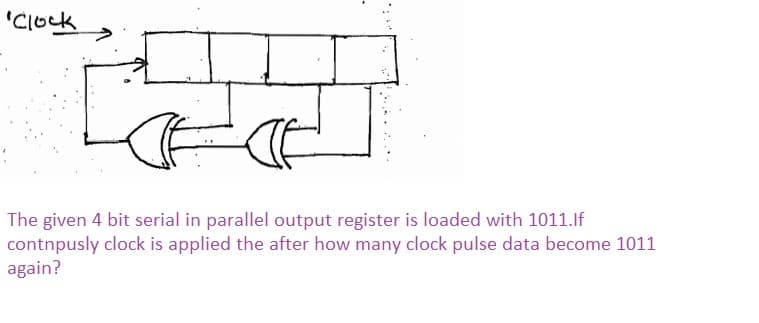

'Clock The given 4 bit serial in parallel output register is loaded with 1011.lf contnpusly clock is applied the after how many clock pulse data become 1011 again?

Q: Design a 8 bits DAC and convert the following binary numbers to Analog 1- (10011101)2 = ? 2-…

A: DAC is a circuit which converts the digital input analog output.

Q: What is the hexadecimal value stored in Register A after the following assembler has executed? LDA…

A:

Q: What is the max input delay for MY_DESIGN, for the given constraints? Clock period =2.5ns clock…

A: what is the max input delay for my design for the given contraints ? clock period =2.5 ns clock…

Q: Design irregular synchronous binary counter and draw the timing diagram for each flip-flop output.…

A: Counters are used to count specific events happening in a circuit. There are two types of counters ,…

Q: clock signal frequency for a 4-bit up counter is 20kHz. What is the frequency of the most valuable…

A: Option :b Answer

Q: Assume register $t0 and $t1 contains 0×020A007E and 0×FFFFFFF0 respectively. The content of $tO…

A:

Q: Assuming even parity, find the parity bit for each of the following data units. a. 1001010 b.…

A: (a) Write the given sequence. 1001010 Since the number of 1’s in the given sequence is 3, that is…

Q: Determine the total time required to serially transfer the eight bits contained in waveform A of…

A: In the question, Determine the time required to serially transfer the eight bits. Clock frequency…

Q: After execution the short label jump instruction: JMP 84h; (when updated IP =A4h), the new value of…

A: JMP instruction is a short jump instruction. It is used to jump within the range of +127 to -128.

Q: Draw a flow diagram for a 2-bit binary counter/clock that counts from 0 to 3 in decimal system using…

A: The counter is used to count by advancing the count of the counter with respect to each clock pulse,…

Q: Define Shift register and draw four-bit shift register using D-Flipflop.

A: Since these are two different questions, in the following section, the first question will be…

Q: What is the function of the odd parity generator circuit? O a. produces an output of '1' for even…

A: As per Bartleby guidelines we are allowed to solve only one question, since these parts are…

Q: The number of clock pulses required to load the value (1011) into a 4- bit parallel load shift left…

A: In this question choose the correct option How many pulse required to load the 4 bit value 1011

Q: QUESTION1: After the instructions 'MOV IE, #83H’ and 'MOV IP, #01H’ being executed, what interrupt…

A: Once the instruction “MOV IE #83H” is executed. MSB enables all the interrupts. The IE register will…

Q: With a neat diagram, explain the working of 4-bit SIPO shift register when the data input is 1001 is…

A: Serial Input Parallel Output Shift Register: In SIPO shift register the data is entered serially…

Q: 3. Draw the block diagram of an 8255 PPI chip and describe its different programming modes.…

A: block diagram for 8255 PPI is as shown in figure below

Q: B/ Design 6-bit parallel in serial out shift register

A:

Q: 1-Why do we use DPSK? For the following message 1111000101110 give the DPSK system. (Note the…

A: DPSK

Q: 2. What is the duration of bus cycle in 8086 MPU if the clock is 20 MHz and two wait states are…

A: Actually all the questions are different, so I am solve 1St questions. 2.

Q: The group of bits 10011 is serially shifted into a 5-bit parallel output shift register with an…

A:

Q: Design an error detector for 6-3-1-1 binary-coded-decimal digits. The output (F) is to be 1 iff the…

A: The code which follow the positional weighting rule is known as Weighted Binary Code. In weighted…

Q: question1:In a memory system, data is 16-bit wide. Break the information into bytes with their…

A: solution:1)Big-Endian method:-In Big Endian machine, first byte of binary representation of he…

Q: The number of clock pulses required to load the value (1001) into a 4- bit serial in shift right…

A: The explanation is as follows.

Q: The upper 16 -bit binary count value are displayed on the four seven -segemnt displays as four…

A: The DAC is an digital to analog convertor. The machines understand the digital binary bits in their…

Q: A 9-bit asynchronous counter has a 128-kHz clock signal applied. (i) What is the MOD number of this…

A: Given here a 9-bit asynchronous counter has a 128-kHz clock signal and here we have to find the mod…

Q: Load the number of ffh into the 'a' register and write the code that reduces the number in the 'a'…

A: Load the number of ffh into the 'a' register and write the code that reduces the number in the 'a'…

Q: Implement a BCD decoder. It should take as input a 4-bit bus representing a BCD digit. It should…

A:

Q: .Assume that one input of a two-input AND gate is connected to a square wave. If the other input is…

A: Given: Two input AND gate. One input is a square wave. Other input is a logic high.

Q: If R0 = 0x20008000, after run STMDB r0!, {r3, r9, r7, r1, r2} command what is the r7 register memory…

A: According to the question, we need to find the memory start address for the resister r7.

Q: in Intel 8086 microprocessor, the memory address for the code segment 771F h and offset 3584 h is O…

A: memory address = code segment + offset 1. Given code segment = 771F and offset = 3584 H code…

Q: Name the addressing mode for the following instruction MOV AL, [BX+si] *

A: The explanation is as follows.

Q: 1-With most monostable multivibrators, what is the output when no input trigger has 2- The bit…

A:

Q: 1What will be the state of a MOD64 counter after 90 input pulses if the starting state=000000?…

A: As per our company guidelines we are supposed to answer only first question kindly repost other…

Q: STC instruction belongs to O a. Direct Addressing O b. Direct 1/O addressing O c. Implied Addressing…

A: Implied addressing mode - The instructions of this addressing mode do not have a operand at all .…

Q: In a 4-bit ripple up-counter how many clock pulses will you apply, starting from state 0 0 0 0, so…

A:

Q: B. Determine the amount of time delay operation of 12-bit serial in / serial out shift register Data…

A: For 12bit SISO register We require 12 flip flops and each flip flop has a time delay Tpd. Therefore…

Q: The sequence 1110 is applied to the input of a 4-bit serial shift register that is initially…

A: Answer : The data bits are 1110 ,∴ the 4-bit shift regista (serial shift) is initially cleaned it…

Q: SV What is clocking block ? what is program block?

A: Reg is driven by always block it can't be driven by continuous assignment statement. Always block…

Q: Write VHDL code for a 16-bit register, with an Asynchronous Reset active Low and a Load signal…

A: Write VHDL code for a 16-bit register, with an Asynchronous Reset active Low and a Load signal…

Q: You want the instruction OUT AL, 25 to activate the LS373 latch. Which control signal on our MCS…

A: We canthe instruction OUT,AL,25 to activate LS373 latch. which control signal must be connected with…

Q: Show the truth table for JK flipflop for positive edge clock triggering. 3b) if for time period…

A: According to the company guidelines we can solve only first question kindly post another question…

Q: Consider the following instruction mix of the LEGV8 assembly code: R-type I-type LDUR STUR CBZ B 24%…

A: We are authorized to answer one question at a time, since you have not mentioned which question you…

Q: 1. The bit sequence 1101 is serially entered (right-most bit first) into a 4-bit parallel out shift…

A:

Q: For the 10 bit +ve edge triggered serial in/serial out shift register, determine the data-output…

A: For the 10 bit positive edge triggered serial in/serial out shift register to determine the…

Q: a) Convert the following unsigned binary numbers to decimal. i) 101101112 ii) 010011012 iii)…

A: “Since you have posted a question with multiple sub-parts, we will solve first three subparts for…

Q: / 4-bit up/down binary counter is in the down mode and in the 1011 tate. To what state does the…

A: As it is 4 bit hence total no of states is 16. 1011 in digital it is 11 so the next state is 10.

Q: Identify the contents of the registers, the memory location (C055H), and the flags as the following…

A: The contents of flag registers are modified when arithmetic and logical instructions are executed.…

Q: Q3: The original contents of CX, AX, memory location Beta, and carry flag (CF) are FFE1 16 11AB1,…

A:

Q: b) For the 4-bit bidirectional shift register, determine the state of the register after each clock…

A:

Q: 14.) Using rising edge JK-Flipflops and Digital Logic Gates, build a 4-Stage Shift Register. I…

A: By using rising edge JK-Flip flops and the Digital Logic Gates Building a 4-stage Shift Registor is…

Step by step

Solved in 2 steps

- A 9 bit asynchronous counter has a 128 - kHz clock signal applied. i) What the mod Number of this counter ? ii) What will be the frequency at the MSB output ? iii) Assume that the counter starts at zero.What will be the count after 6.15 input pulse?If Timer 0 Register TMR0L is initialized with -1 in 8-bit mode, then after how many clock cycles rollover happens?Draw the Moore and Mealy State Diagram of a Finite State Machine thatfunctions as a Binary Sequence Detector for the following sequence:a. 01011b. 101 and/or 010Obtain the State Table for each of your diagrams?

- S Display will be designed for a thermometer. The display will show that degree for minimum temperature and 99 degrees for maximum temperature. According to this; a) What is the number of bits that will be needed in the binary code to express the temperature? b) What are the binary, octal and hexadecimal equivalents of 95 degrees? () What is the BCD representation of 95 degrees? d) What is the hex equivalent of this temperature when it shows 111 degrees octal? e) If the thermometer showed a temperature between -99 and +99 degrees, how many bits would we need?true or false ?? an even two bit parity checker will output a parity error if data A=LOW data , B=HIGH. parity bit = HIGHplease show work included 4. If a 6-bit binary number is used to represent an analog value in the range from -63 to 126, what is the accuracy of the system? In other words, if the binary number is incremented by one, how much change does it represent in the analog value?

- A)What will be the frequency at C if the clock is 320 kHz? B) What is the modulo of the circuit? C) What is the output (in binary) after 737 pulses?5 clock signal frequency for a 4-bit up counter is 20kHz. What is the frequency of the most valuable bit output? d) none1. Using the byte rotation scheme described for the ARM7TDMI, calculate the instruction and rotation needed to load the following constants into register r2: a) 0xC3300000 b) 0xFFFFFF44

- Using a combination of shift registers and latches explain how a small number ofmicrocontroller I/O pins can be used to read from or write to a large number of digitalsignal lines. Illustrate your answer. What is the main disadvantage of this I/O expansionapproach?The 8085-instruction set does not include a Clear Carry instruction. Which single-byte logical instruction can clear the carry without modifying the contents of the accumulator?Please determine output logic #40 please