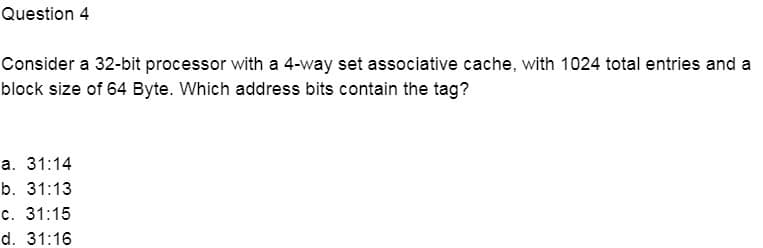

consider a 32-bit processor with a 4-way set associative cache, with 1024 total entrie lock size of 64 Byte. Which address bits contain the tag? . 31:14 . 31:13 . 31:15 . 31:16

Q: Suppose a computer using direct-mapped cache has 232 bytes of byte-addressable main memory and a…

A:

Q: Consider a 4-way set associative cache made up of 64-bit words. The number of words per line is 8…

A: INTRODUCTION: The cache is a small piece of memory that is part of the CPU and is physically closer…

Q: Given a computer using a byte-addressable virtual memory system with a two-entry TLB, a 2-way set…

A:

Q: Consider a paging system with the following: Physical memory= 32 bytes. Page size=4 bytes. Page…

A: Page size = 4B. So page offset = 2 bits. The offset for physical and virtual address is same. A)…

Q: Consider a machine with a word addressable and a word consists of 2 bytes, main memory of 236 bytes…

A: Given in the question: Main memory size = 236bytes Total address space = 36 bits Block size = 32…

Q: In a page addressing system of 15 bits, where eight bits are used for the page number, what would be…

A: The above question is solved in step 2 :-

Q: Consider a logical address space of 64 pages with 2048 words per page; mapped onto a physical memory…

A: A virtual address is known as logical address, it provide reference for CPU to access the physical…

Q: Suppose direct-mapped cache has 64KB data and oneword blocks. How many total bits does it contain?…

A: Block size: 1 word = 1*4B = 4B Number of block = 64KB/4B = 16K Number of bits in index = log(16K) =…

Q: Consider a 4-way set ansociative cache made up of 64-bit words. The number of words per line is 8…

A: Cache memory is the faster then RAM. Its size is small as compared to RAM.

Q: Consider a computer with the following characteristics • total of 1Mbyte of main memory • word size…

A: Answer : Memory = 1MB => 20 bits. Block size = 64B=> Block Offset = log 64 = 6 bits. A) Total…

Q: Suppose we have a computer system with 44-bit logical addresses, page size of 64KiB, and 4 bytes per…

A: The answer is explained in detailed below:

Q: Consider a byte-addressable computer with 24-bit addresses, a cache capable of storing a total of…

A: Advantages of using direct memory mapping: 1) No replacement algorithm is needed. Disadvantages of…

Q: A cache of 2048 blocks, an eight-word block size, and a 32-bit address. Compare between the total…

A: Given: Number of blocks = 2048 = 211 Block size = 8 words Address = 32 bits

Q: Suppose a computer using direct mapped cache has 4MB of byte-addressable main memory, and a cache of…

A: A) Total number of blocks in main memory = 2^22/2^4 = 2^18 B) Size of offset field =log(block size)…

Q: Consider a cache, in which the block has 512 bytes. The main memory has a latency of 32 ns and a…

A: We are given block size of a cache and main memory latency with bandwidth. We are asked the time…

Q: In a microprocessor of 32 bit addresses, the tag length will change if we design a two-way…

A: two-way set-associate cache versus a four-way set- associative cache: Two way set associative cache…

Q: Consider a 64-bit word-based four-way set associative cache. The number of words each line is 8, and…

A: Given: Consider a 64-bit word-based four-way set associative cache. The number of words each line is…

Q: How many total bits are required for a direct-mapped cache with 16 KiB of data and 4-word blocks,…

A: Given :16 KiB As, we already know that,16 KiB = 4096 (212) words. So, Block size = 4 words (22),…

Q: Consider a 4-way set associative cache consisting of 128 lines with a line size of 64 words. The CPU…

A: Given that, Number of lines= 128 Line size= 64 words Number of bits in main memory address= 20 bits…

Q: Consider a four-way set associative cache comprised of 64-bit words. The number of sets is 4096 and…

A: Intro Consider a four-way set associative cache comprised of 64-bit words. The number of sets is…

Q: A computer system has a 128 byte cache. It uses four-way set-associative mapping with 8 bytes in…

A: Given Cache size =128 = 27 bytes Block size = 8 bytes = 23 bytes Physical address = 32 bits.…

Q: a microprocessor of 32 bit addresses, the tag length will change if we design a two-way…

A: A 2 way set associative cache means total number of block inside each set is 2 A 4 way set…

Q: Suppose we have a byte-addressable computer using fully associative o 20-bit main memory addresses…

A: Actually, 1 byte =8 bits. cache memory is a fast access memory.

Q: Consider a 64-bit word-based four-way set associative cache. The number of words each line is eight,…

A: inception: The cache is a small chunk of memory that is physically closer to the CPU than RAM. It is…

Q: Consider a machine with a byte addressable main memory of 216 bytes and block size of 8 bytes.…

A: Cache memory serves as the fastest memory access in the computer architecture. Cache memory is…

Q: Consider a system with 36-bit virtual addresses, 32-bit physical addresses, and 4KB pages. The…

A: Given,The virtual Address space = 236 bytesPage size = 212 bytesPages = 236 / 212 = 224 Pages

Q: Consider a logical address space of 1K pages with a 4KB page size, mapped onto a physical memory of…

A: Below is the answer to above question. I hope this will be helpful for you..

Q: A system with 64GB memory with a block size of 4 words, and a 256KB direct map cache. The word size…

A: Given: Memory =64 GB that means total bits = log2(64GB)=log2(236)=36 Cache size = 256 KB Block Size=…

Q: Consider 1MB cache with 128-byte byte-aligned blocks, 4-way set associative ways for a m memory…

A: Cache size:- Reserve size is vital to your application since, supposing that it is set to…

Q: Consider a system consisting of thirty-two bits virtual address, page size is 16 KB and a 512 lines…

A: The virtual address is of 32 bits. Whenever CPU wants any data from the memory, it generates 32bit…

Q: Consider a memory system with cache access time of 0.1 us and memory access time (time needed to…

A:

Q: If my cache block offset is 4 bits, and I read the address OXF2CA87A what is the smallest number of…

A: Here offset bits is 4 bits.

Q: Consider a machine with a byte addressable main memory of 216 bytes and block size of 8 bytes.…

A:

Q: consider a processor using 32-bit memory addresses, also a 4 KiB (of actual data) direct-mapped…

A:

Q: Consider a machine with a byle addressable main memory of 2 bytes and block size of 8 bytes. Assume…

A: required:

Q: Show how the following is divided into tag, index, and offset (i.e. # of Bits for each): • Total…

A: Cache is the primary storage with cache lines that are grouped into blocks. A data request will be…

Q: Consider a word addressable system. The main memory is of size 2 MB and direct-mapped cache…

A: consider word addressable system. The main memory size of 2MB and direct -mapped cache containing…

Q: Suppose a computer using fully associative cache has 220220 words of main memory and a cache of 128…

A: solution:

Q: Consider a logical address space of 1K pages with a 4KB page size, mapped onto a physical memory of…

A: (1) Logical address space (size)=2m then: Logical address space(size)= no of pages ×page size…

Q: How many total bytes would be necessary for a 4-way set associative cache with 64 KBytes of data…

A: 1 word is 32 bits as we are using 32 bit address Therefore, 1 Word = 4 Bytes Size of a cache block =…

Q: Suppose we have a byte-addressable computer with a cache that holds 16 blocks of 4 bytes each.…

A: The given system is a byte addressable computer. Number of blocks = 16 Block Size = 4 Bytes Length…

Q: Suppose a computer using fully associative cache has 2^24 bytes of byte-addressable main memory and…

A: Full associative cache size=224 bytes.Size of each block=64 bytesBlocks of main memory=cache…

Q: Consider a cache of 4 K blocks, a 4 word block size and a 32 bit address main memory. What is the…

A: The total number of tag bits per set for 4-way set associative cache

Q: Suppose we have a byte-addressable computer using a direct mapped caching with 20-bit main memory…

A: Actually, binary numbers are 1's and 0's. 1 byte =8 bits

Q: Given a computer using a byte-addressable virtual memory system with a two-entry TLB, a 2-way set…

A: Below is the answer with explanation and calculation:

Q: What is the Effective memory access time for a machine with a cache hit rate of 90%, where the cache…

A: As we know the formula of Effective memory access time is Average Memory Access Time = Hit ratio *…

Q: Consider a machine with a byte addressable main memory 24º bytes, block size of 16 bytes and a…

A: Introduction :

Q: Given a 2-way set-associative cache with 2 entries (sets) and 1 byte block size (no offset), what is…

A:

Step by step

Solved in 2 steps with 1 images

- Q: A digital computer has a memory unit of 64k * 16 and a cache memory of 1k words. The cache uses direct mapping with a block size of 4 words. i) How many bits are there in the tag, index, block & words fields of the address formats.ii) How many bits are there in each word of cache? iii) How many blocks can the cache accommodate? Note: this question is related from computer architecture subject kindly solved this correctly and completly.A 1 GByte RAM with 64 word/line is mapped to an 8 kLine Cache with Associative Mapping. What will the address look like?How many total bytes would be necessary for a 4-way set associative cache with 64 KBytes of data and one word blocks, assuming a 32-bit addressing used?. A 96 KBytes B 106 KBytes C 105 KBytes D 102 KBytes E 100 KBytes F 109 KBytes

- A processor has an 30-bit physical address space (A memory address is 30-bit). It also has a physically addressed, 8-way set associative cache. If the size of the entire cache is 64 KB, and the block size is 4Byte How many sets (i.e. lines) exist in this cache? How many bits are used to address each cache line?(index bits?) How many bits are stored in the tag area?We have a fully associative cache memory with 216entries). Each entry is hosting 32 data. How manybits are necessary for the TAG for a 28 bits address?5 A12 B23 C None of previous answers D , also is there a difference if it was fully associative mapping cache memory or no? solve this question in great detail explaining every single bit of info as i'm a complete beginner and i need to understand how to solve questions of this type. also provide small examples of how the solution would differ if the question was slightly altered.A computer system has 32 address lines and 16K bytes cache. Each cache block size is 32 bytes. For the following cases, (a) a direct mapped cache (b) a fully associative cache (c) a 4-way set associative cache (1) How many comparators are required in each cases? (2) When the CPU references an address 0xABCDEF12, what is the tag value for each cases?

- A computer has a 256 KB, K-way set associative write-back data cache with block size of 32 B. The address sent to the cache controller by the processor is of 32 bits. In addition to the address tag, each cache tag directory contains 2 valid bits and 1 modified bit. If 16 bits are used to address tag. What is the minimum value of K?Q: A digital computer has a memory unit of 64k * 16 and a cache memory of 1k words. The cache uses direct mapping with a block size of 4 words. i) How many bits are there in the tag, index, block & words fields of the address formats. ii) How many bits are there in each word of cache? iii) How many blocks can the cache accommodate?Question p .A computer has an 8 GByte memory with 64 bit word sizes. Each block of memory stores 16 words. The computer has a direct-mapped cache of 128 blocks. The computer uses word level addressing. What is the address format? If we change the cache to a 4- way set associative cache, what is the new address format? Full explain this question and text typing work only We should answer our question within 2 hours takes more time then we will reduce Rating Dont ignore this line

- 1. CPU with 2ns clock, hit time = 1 cycle, miss penalty = 40 cycles, cache hit rate = 90% AMAT = ___ ns.? 2. A memory system with cache memory has an 8-bit word address. Each memory block (or cache line) consists of 4 words. How many bits are used for the word offset in an address? 3. A memory system with cache memory has an 8-bit word address. The direct-mapped mapping technique is used. The cache memory has 8 cache blocks. How many bits are used for the block index field in an address?We have a full associative mapping cache memorywith globally 65536 = 2^16 lines. Each line is hosting32 data. How many bits are necessary for the TAG fora 24 bits address bus?3 A19 B21 CNone of previous answers solve this question in great detail explaining every single bit of info as i'm a complete beginner and i need to understand how to solve questions of this type. also provide small examples of how the solution would differ if the question was slightly altered. THANK YOU!Suppose you are designing a small, 16KB, 2-way set-associative L1 and a large, 32MB, 32- way set- associative L3 cache for the next processor your company will build. Which one of the following design decisions would you make and why? Justify your choice. Access L1 tag store and data store: in parallel OR series (circle one and explain) Access L3 tag store and data store in parallel OR series (circle one and explain)