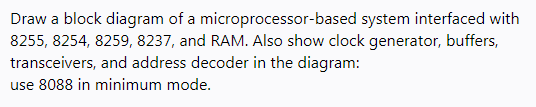

Draw a block diagram of a microprocessor-based system interfaced with 8255, 8254, 8259, 8237, and RAM. Also show clock generator, buffers, transceivers and address decoder in the diagram: use 8088 in minimum mode.

Q: On a typical microprocessor, a distinct I/O address is used to refer to the I/O data reg- isters and…

A: There are two I/O instruction formats utilized in the Intel 8088. In one format, an 8-bit port…

Q: suppose, a soft real-time system has 100 m bytes of program memory that is loaded at 75% 16M bytes…

A: Given Total memory=100 Used memory=16 +10 = 26 Formula to calculate Total memory utilisation=…

Q: Let the base addresses for I/O devices mentioned in (a) are 240, 244, 250, and 2F8 respectively.…

A: Required : Commands to load given address to devices

Q: a) Draw a block diagram of a microprocessor based system interfaced with 8255, 8254, 8259, 8237 and…

A: Answer B part only!a) Draw a block diagram of a microprocessor based system interfaced with 8255,…

Q: For a memory with a 5bit wide address bus and a 32bit wide data bus, answer the followin uestions:…

A: A) Total number of distinct address = 2 address bus width = 25 = 32

Q: B) Let the base addresses for I/O devices mentioned in (a) are 240, 244, 250 and 2F8 respectively.…

A: Solve only Part B(a) Draw a block diagram of a microprocessor based system interfaced with 8255,…

Q: Q#03) (a) Explain and demonstrate the use of the RISC and CISC architectures in computer…

A: Given: Q#03) (a) Explain and demonstrate the use of the RISC and CISC architectures in computer…

Q: Design a memory system for the 8088 Microprocessor such that it can select two EPROMS (128K x 8)…

A:

Q: Consider a 32-bit microprocessor, with a 16-bit external data bus, driven by an 8-MHz input clock.…

A:

Q: A microprocessor scans the status of an output I/O device every 20 ms. This is accom- plished by…

A: Introduction: In this question, we are asked to calculate the time to scan and service the device in…

Q: Consider a 32-bit microprocessor whose bus cycle is the same duration as that of a 16-bit…

A: The Answer is

Q: Consider a 32 – bit microprocessor, with a 16 – bit external data bus, driven by an 8 MHz input…

A: Introduction :Given , A 32-bit microprocessor,Data bus size = 16 bits clock rate = 8MhzWe have to…

Q: Compare the PRAM models with physical models of real parallel computers in each of the following…

A:

Q: The main reason a single-cycle processor datapath as taught in lectures must have separate…

A: Please find the answer below :

Q: interface four chips of 128k×8 SRAM to 8086 microprocessor using separate bank write strobes such…

A:

Q: Draw a block diagram of a microprocessor based system interfaced with 8255, 8254, 8259, 8237 and…

A: Solution :-- Draw the block diagrams of microprocessor based system interfaced with 8255,8254,…

Q: Consider a system in which the 64kb emory space is implemented using eight numbers of 8kb memory.…

A: The memory is implemented using 8KB of memory. The original memory size is 64KB which is…

Q: Consider a 32-bit microprocessor whose bus cycle is the same duration as that of a 16 bit…

A: The answer is given in the below step

Q: With the help of a block diagram show and briefly explain: Stack Push Operation showing the status…

A: An Abstract Data Type (ADT) is a type of data that is used in almost all computer languages. It's…

Q: 2. Suppose that we are given 32KB SRAM ICs and 8KB ROM ICs. We want to construct the address range…

A: Lets see the solution.

Q: Let us suppose, for the sake of simplicity, that each instruction on a RISC processor is processed…

A: The solution to the given question is: Given that the execution takes 2 microseconds = 0.002…

Q: Suppose the implementation of an instruction set architecture uses three are called A, B, and C. The…

A: The answer is

Q: The Kiwi™ memory architecture design team has a dilemma. The team is considering several different…

A: a) Design 1 logical address width = 12 bits logical memory size = (2^12)bytes page size = 16 bytes…

Q: Interface 8KX8 RAM and 4KX8 ROM chips with 8085 microprocessor by demonstrating proper block…

A:

Q: memory range from 0xA000 to 0xCFFF (inclusive) Your design must be subject to the followi

A: The system has 3 microprocessors and shared memories are there for all the processors. there will be…

Q: Let us consider a memory that includes two instructions. First instruction is located at memors…

A: It can be approached as: The instruction consists of opcode and operands. Given the instruction…

Q: (a) In the given 8086 block diagram, write down the sizes of the (i) registers (ii) segments (iii)…

A: The answer is given below:-

Q: 2. Determine the data memory location addressed by Intel 8086 microprocessor for the following DS:BX…

A: A. Data segment B. 013F H C. 5658F H D. Based indexed relative addressing mode 2nd question A. 24D9…

Q: Assume that a RISC processor takes 2 microseconds to execute each instruction and that an I/O device…

A: RISC processor takes 2 microseconds to execute each instruction and that an I/O device can wait at…

Q: Consider a 32-bit microprocessor whose bus cycle is the same duration as that of a 16-bit…

A: Calculate the improvement achieved when fetching instructions and operands: Assuming with 100%…

Q: For the below microprogrammed architecture, what is the ALU sequence of actions/micro instruction…

A: Solution:-- 1)The given question is an type of the multiple choice question so some of the options…

Q: Suppose you are given with a ROM chip of size 1024*8 and 5 RAM chips of size 512*8. Show…

A: The formula for calculating RAM devices: This chip has eight bits. Because one byte requires eight…

Q: Assume that a RISC processor executes each instruction in two microseconds and that an I/O device…

A: Introduction: In a RISC processor, interruptions keep the CPU from stalling when I/O devices are not…

Q: Consider a 32-bit microprocessor, with a 16-bit external data bus, driven by an 8-MHz input clock.…

A: Introduction :Given , 32 bit microprocessordata bus is 16 bits clock rate is 8 MHzWe have to…

Q: Show a schematic diagram for interfacing an 8KB ROM starting at 0000H and 4KB RAM with 8085. The…

A: It is defined as the set of all possible addresses that a microprocessor can generate. 8085…

Q: Assume that a RISC processor executes each instruction in 2 microseconds and that a 1/O device can…

A: Introduction: Assume that a RISC processor executes each instruction in 2 microseconds and that a…

Q: For simplicity, let us assume that each instruction on a RISC processor is executed in 2…

A: Introduction: Handling interrupts in a RISC processor: Interrupts are used to keep the CPU from…

Q: Draw a block diagram of a microprocessor based system interfaced with 8255, 8254, 8259, 8237and…

A: In above question we make a microprocessor diagram which one have 4 ,8255 ,8254,8259,8237 and RAM.…

Q: Answer B part only! a) Draw a block diagram of a microprocessor based system interfaced with 8255,…

A: Question:

Q: Assume that a RISC processor executes each instruction in 2 microseconds and that an I/O device can…

A: Handling interrupts in a RISC processor: Interrupts serve as a safeguard against the CPU stalling…

Q: Assume the processor is driven by a clock, such that each control step is 4 ns in duration. How long…

A: Given Data : Control Step time = 4ns Read operation time = 12 ns To find : Percentage of time…

Q: Why are memory address decoders important? Calculate the starting and ending а) address of the 4K…

A: Since you have asked multiple questions in a single request, we will be answering only the first…

Q: In the figure below, the typical organization of a modern von Neumann processor is illustrated. Note…

A: (1)Active part of the computer,which does all the work of data manipulation and decision making…

Q: Show its implementation through a 4-stage pipelined porcessor having: Fetch Unit – Decode Unit –…

A: Data Hazard occurs whenever the operation of particular instruction depends upon the result of the…

Q: Draw a block diagram of a microprocessor based system interfaced with 8255, 8254, 8259, 8237 and…

A: 8255 Pin Diagram: Fig shows the 8255 Pin Diagram of Microprocessor. 8255 Block Diagram: Fig.…

Q: . Consider a pipelined RISC CPU with 11 stages. What is maximum speedup of this CPU over a…

A:

Q: Suppose a system with separated parts of Data and Code. Instructions fetch or data fetch is used by…

A: Advantages and disadvantages are in Step 2.

Draw a block diagram of a microprocessor-based system interfaced with 8255, 8254, 8259, 8237, and RAM. Also show clock generator, buffers, transceivers and address decoder in the diagram:

use 8088 in minimum mode.

Trending now

This is a popular solution!

Step by step

Solved in 3 steps with 8 images

- Processor R is a 64-bit RISC processor with a 2 GHz clock rate. The average instruction requires one cycle to complete, assuming zero wait state memory accesses. Processor C is a CISC processor with a 1.8 GHz clock rate. The average simple instruction requires one cycle to complete, assuming zero wait state memory accesses. The average complex instruction requires two cycles to complete, assuming zero wait state memory accesses. Processor R can’t directly implement the complex processing instructions of Processor C. Executing an equivalent set of simple instructions requires an average of three cycles to complete, assuming zero wait state memory accesses. Program S contains nothing but simple instructions. Program C executes 70% simple instructions and 30% complex instructions. Which processor will execute program S more quickly? Which processor will execute program C more quickly? At what percentage of complex instructions will the performance of the two processors be equal?Draw a block diagram of a microprocessor based system interfaced with 8255, 8254, 8259, 8237 and RAM. Also show clock generator, buffers, transceivers and address decoder in the diagram: use 8086 in maximum mode Please helpSolve only Part B(a) Draw a block diagram of a microprocessor-based system interfaced with 8255, 8254, 8259, 8237and RAM. Also show clock generator, buffers, transceivers, and address decoder in the diagram:use 8088 in minimum mode B) Let the base addresses for I/O devices mentioned in (a) are 240, 244, 250, and 2F8 respectively. Write assembly commands to load these control/command words in these devices.

- Consider a 32 – bit microprocessor, with a 16 – bit external data bus, driven by an 8 MHz input clock. Assume that this microprocessor has a bus cycle whose minimum duration equals four input clock cycles. What is the maximum data transfer rate for this microprocessor?Draw the internal block diagram of 8086 microprocessor and explain the functions of bus interface unit.Show a schematic diagram for interfacing an 8KB ROM starting at 0000H and 4KB RAM with 8085. The starting address of RAM is 22D5H, given that memory is available only in multiples of 2KB

- . Examine any 64-bit microprocessor architecture and analyse the following points: • Hardware Support for Memory Management Pipeline Architecture in Bus ArchitectureSolve only Part B(a) Draw a block diagram of a microprocessor based system interfaced with 8255, 8254, 8259, 8237and RAM.Also show clock generator, buffers, transceivers and address decoder in the diagram:use 8088 in maximum mode B) Let the base addresses for I/O devices mentioned in (a) are 240, 244, 250 and 2F8 respectively. Write assembly commands to load these control/command words in these devices.Suppose we have a byte-addressable memory of 20 bytes, built using 4 modules. Draw diagrams showing the distribution of addresses within each module, if we are using (a) highorder interleaving, and (b) low-order interleaving.

- When it comes to a processor's access to main memory, the loosely connected setup and the symmetric multiprocessing configuration are similar. Explain why, in the real world, the symmetric design might be better.Consider a simple read-only memory (ROM) unit with 2-bit addressand 2-bit data buses.Draw the internal architecture of such a ROM unit includingtransistors, address and data signals, and the row decoder.? I have attached the answer to the question, but I am confused by it, if you could explain every step including how many transistors to use, where to place them and the basic procedure which could be used with other similar questions that would be helpfulDesign a memory map for a system with 64 K of memory space, a 16-bit address bus, and a 8-bit data bus. The system needs to meet the following design requirements: The system needs 20 K of RAM, organized in a contiguous block starting at address 0x1000 . The system needs RAM filling the memory range from 0xA000 to 0xCFFF (inclusive) Your design must be subject to the following constraints in terms of access to memory chips: You can use a maximum of two (2) 8 K×8 RAM chips. You can use a maximum of two (2) 4 K×8 RAM chips. You can use a maximum of two (2) 8 K×8 ROM chips. You can use a maximum of two (2) 4 K×4 ROM chips.