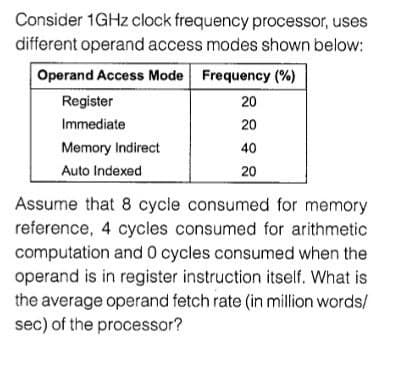

ed for memory a for arithmetic umed when the n itself. What is n million words/

Q: Given the following expression, Z = [(G+E) * A] – [H * (A + S / L)] Write the following machine…

A: Z=[(G+E)*A]-[H*(A+S/L)] Zero-address instruction: It represents the postfix notation of the…

Q: L = {o € {0, 1}* | o¢0"} 6. I.e., the language of words that are not palindromes. Provide a brief…

A: For creating the PDA for words that are not palindromes, the PDA for language of all palindrome…

Q: 5. Given the following "Super Simple CPU" program: LDI 6 SUB ONE ADD TWO DONE STO ONE STP DAT 1 DAT…

A: I have provided the answer based on Pseudo Programming. Detailed comments are included for a better…

Q: Which component of the CPU handles floating-point arithmetic?

A: Intro Addition, subtraction, multiplication, and division are the arithmetic operations that may be…

Q: ?Word aaabbccddd accepted by this machine No O Yes Answer about these questions: b, e>b c, bE d, aE…

A: Here we are going to check whether the given word is accepted by PDA or not

Q: excess notation

A: ANSWER: Excess Notation: This decent length notation makes it conceivable to store negative and…

Q: Explain the following arithmetic instructions in your own words: a) INR B b) DCR B c) ADD C

A: Note: Since we only answer up to 3 sub-parts, we’ll answer the first 3. Please resubmit the question…

Q: What issues occur when a computer can only handle and store integers? We have a problem on our…

A: The challenges that computers face when they are capable of handling and storing integers, as well…

Q: Why is it that when a binary digital computer does floating-point arithmetic, the output always…

A: INTRODUCTION: Arithmetic in floating points: The addition of two decimal values written in…

Q: For a given binary number 1101111 what is it in decimal? What does it mean when we refer to a…

A: The 8 steps of the operation of a CPU are as follows: A sequence of instructions is stored in…

Q: n the concept of memory segmentation. How is the ations of program bytes generated?

A: The programmable peripheral interface is a programmable input/output device that can be used for a…

Q: Which part of the CPU is in charge of floating-point arithmetic?

A: Intro Addition, subtraction, multiplication, and division are the arithmetic operations that may be…

Q: 14) RAM stands for random access memory, while ROM stands for read only memory. (Is it a T or a F)?

A: Please find the answer to the above question below:

Q: In a 64-bit machine, what is the total memory in bytes of 10 integer variables and 5 char variables?

A: Introduction: The total memory in bytes consists of 10 integer variables and 5 char variables.

Q: It is well known that computers operate in binary. Why aren't alternative systems like decimal,…

A: Computers Operate in Binary: The binary numbers 0 and 1 are used by computers to store data. A bit,…

Q: 2. Consider the system to be 64 bit, answer the following question in accordance to C language, a)…

A: int implies that it is actually the variable which has the datatype as integer. sizeof(int) this…

Q: A PDA has "XY" MB of memory, Where XY are the last two numbers of your student number (e.g for…

A: GIVEN: The memory address space= 89 MB. CONVERSIONS: 1MB= 1024 KB = 2^10 KB I KB= 1024 BYTES =…

Q: A = {d'b?"\n > 0}. п

A: Pumping lemma is used to show that certain languages are not regular. It should never be used to…

Q: en the image below, what is the Linear Address of the memory tion currently being pointed to in the…

A: It is defined as the process that is represented by .data section and the .bss. The .data section is…

Q: e. What is the instruction to compute double-precision floating-point addition? Show an example…

A: Double precision Floating Point The double-precision floating-point format, also known as FP64 or…

Q: 1. A set of 10 readings is stored in memory locations starting at XX50H. The readings are expected…

A: Required:- Write a program in assembly language. The below conditions also make. It's a flow…

Q: 2. Consider the system to be 64 bit, answer the following question in accordance to C language, i)…

A: To find the size of int, char, int *, and char *, consider the system to be 64-bit and in accordance…

Q: a) Given the following expression, X= [ ((S / B "(Q - R)) + E) / (D - M * U)] i. Convert the…

A: The Given expression: X = [((S/B*(Q-R)) +E)/(D-M*U)] The Postfix notation is as follows: X= [SB /…

Q: Why is random memory numbered at all?

A: Introduction: It must be loaded with the software and data byte from the magnetic discs on which the…

Q: 7. Convert the following signed decimal numbers into binary numbers: a. +11 b. -28 c. +0601 d. -0106

A: 7. Example Convert 32 into binary form.Solution:32/2=16: remainder(0)16/2=8: remainder(0)8/2=4:…

Q: Hz. The following table gives number of instruction for a Program A, as well as structions take, for…

A: Here,is the solution:- Clock cycle time is given as:- 5 ns LOAD instructions take 5 clock cycles,…

Q: The diagram below represents the various portions of a single-precision floating-point number as…

A: Both questions are answered below:

Q: Given two numbers: s0=1001 0101 0011 1101 s1=1101 0101 0101 1111 a) What numbers do the…

A: According to the information given:- We have to define two number represent by anded and ored…

Q: (3) Four different measures of memory are listed below. Order the measures by writing then them,…

A: I have answered the 3rd question and have tried explaining each step. Please refer to the image for…

Q: 2. Design a Read Only Memory (ROM) to implement the following, A097803, polynomial A = 3(2x² + 1),…

A: Answer: I have given answer in the handwritten format.

Q: 8. Which of the following is the Valid Measurement unit of memory A. GB В. МB С. КВ D. All

A: TO do: Valid measurement unit of memory from given options

Q: 4. Reverse an array of ten 32 bit numbers in the memory.

A: Given: Reverse an array to 32 bit numbers in the memory.

Q: GIVEN 1. FCFS PID AT BT 2 2 3 6 5 4 3 10 n m63

A: We are going to use fcfs scheduling algorithm and we will see CPU utilization for it.

Q: Even numbers are recognized by: Select one: O a. None of the options here O b. Least Significant Bit…

A: The question has been answered in step2

Q: Other name of PROM is _______________ Memory.

A: Given fill in the blank question wants other name of prom.

Q: n this article, we'll explain what nonvolatile memory is and how it works.

A: Non Volatile memory and its working

Q: Thẻ čóntént of PC in the simple computer is 3AFH. The content of AC is 6EC3H. The ntent of memory at…

A: a) List of the initial conditions that are given below: AR IR 3AFH 632EH 32EH…

Q: (i) Which of the following statements are true ? a) Nibble : A collection of 4 bits b) Word:…

A: here in this we have given two question . in the first one we have asked about bi involved in nibble…

Q: (iv) How many bytes in memory will be required to store 10 integers and 6 boolean variables.

A: Find the size of memory in bytes required to store 10 integers and 6 boolean variables.

Q: 1000 unsigned numbers located in memory starting at address F000H. Draw the flow diagram and write…

A: 1000 unsigned numbers located in memory starting at address F000H. Draw the flow diagram and write…

Q: 11. Which of the following is the correct sequence of operations in a microprocessor? a) Opcode…

A: In Microprocessors, it contains mainly four operations. The sequence of that operations are: Fetch…

Q: Other name of GB is _______________ Byte.

A: Given fill in the blank question is based on computer memory.

Q: Odd numbers are recognized by: Select one: O a. Most Significant Bit b. 2's compliment bit C. Least…

A: Low level language is the one which is used as a Machine language, and only contains two symbols…

Q: How much ROM is provided in the PC? What are the standard data word lengths for which…

A: NOTE:- AS PER OUR POLICY WE CAN SOLVE ONLY ONE QUESTION AT A TIME. SO, PLEASE REPOST THE REST…

Q: b-) Convert the following instruction to machine code in decimal. (No need to convert it to binary)…

A: Solution:-

Q: How many bits would you need to address a 2M × 32 memory if a) the memory is byte addressable? b)…

A: Memory Bits Memory is built from random access memory (RAM) chips. Memory is often referred to using…

Q: Why is random memory numbered in the first place?

A: Introduction: It must be loaded with the software and data byte from the magnetic discs on which the…

Q: e. What is the instruction to compute double-precision floating-point addition? Show an example…

A: I have answer this question in step 2.

Q: write a program that does the following: AL=9 AL++ X=AL Using 8086emu program check the status of…

A: Question :-

Q: a) Given the following expression, X = [ ((S / B *( Q– R)) + E) / (D - M * U) ] i. Write the…

A: Accumulator (A) is used to store the value whenever we load any variable The given expression is…

Step by step

Solved in 2 steps

- Processor R is a 64-bit RISC processor with a 2 GHz clock rate. The average instruction requires one cycle to complete, assuming zero wait state memory accesses. Processor C is a CISC processor with a 1.8 GHz clock rate. The average simple instruction requires one cycle to complete, assuming zero wait state memory accesses. The average complex instruction requires two cycles to complete, assuming zero wait state memory accesses. Processor R can’t directly implement the complex processing instructions of Processor C. Executing an equivalent set of simple instructions requires an average of three cycles to complete, assuming zero wait state memory accesses. Program S contains nothing but simple instructions. Program C executes 70% simple instructions and 30% complex instructions. Which processor will execute program S more quickly? Which processor will execute program C more quickly? At what percentage of complex instructions will the performance of the two processors be equal?Consider three different processors P1, P2, and P3 executing the same instruction set. P1 has a 3.1 GHz clock rate and a CPI (cycles per instruction) of 1.6. P2 has a 2.4 GHz clock rate and a CPI of 1.2. P3 has a 4.0 GHz clock rate and has a CPI of 2.0 If you could answer these id appreciate that greatly. a.Which processor has the highest performance expressed in instructions per second? b.If the processors each execute a program in 10 seconds, find the number of cycles and the number of instructions. c.We are trying to reduce the execution time by 30% but this leads to an increase of 20% in the CPI. What clock rate should we have to get this time reduction?Let's assume that there are three processors, Pa, Pb, and Pc, like below. You can assume 1-way superscalar, no hyper-threading, and no pipelined for all processors. Pa: 4 GHz clock rate, CPI: 2.2 Pb: 3 GHz clock rate, CPI: 1.5 Pc: 2.5GHz clock rate, CPI: 1.05.1. Show each processors' performance in terms of instruction per second.

- Consider three different processors P1, P2, and P3 executing the same instructionset. P1 has a 3GHz clock rate and a CPI of 1.5. P2 has a 2.5GHz clock rate and a CPI of 1.0, P3has a 4GHz and a CPI of 2.5.a) Which processor has the highest performance expressed in instructions per second?b) If the processors each execute a program in 5 seconds, find the number of cycles and thenumber of instructions.c) We are trying to reduce the execution time by 20% but this leads to an increase of 15% inthe CPI. What clock rate should we have to get this time reduction?Consider three different processors P1, P2, and P3 executing the same instruction set. P1 has a 3 GHz clock rate and a CPI of 1.5. P2 has a 2.5 GHz clock rate and a CPI of 1.0. P3 has a 4.0 GHz clock rate and has a CPI of 2.2. Which processor has the highest performance expressed in instructions per second? If the processors each execute a program in 10 seconds, find the number of cycles and the number of instructions.Q: Consider three different processors P1, P2, and P3 that support the same instruction set. P1 has a 3 GHz clock rate and a CPI of 1.5. P2 has a 2.5 GHz clock rate and a CPI of 1.0. P3 has a 4.0 GHz clock rate and has a CPI of 2.2. (a) Which processor has the highest performance expressed in instructions per second? Show your calculations. (b) If the processors each execute a program in 10 seconds, find the number of cycles and the number of instructions for each processor. (c) We are trying to reduce the execution time by 30% (i.e., execution time is reduced from 10 seconds to 7 seconds). However, this leads to an increase of 20% in the CPI. For each processor, what clock rate should we have to get this time reduction? (Show the calculations you did to answer this question.)

- Consider three different processors P1, P2, P3 executing the same set of instructions. P1has a 3 GHz clock rate and a CPI of 1.5. P2 runs at 2 GHz and has a CPI of 1.2. P3 has a 4GHz clock rate and a CPI of 2.4.a. Which processor has the highest performance in terms of instructions per second?b. If each processor executes a program in 5 second, find the number of cycles and thenumber of instructions for each processor.c. We would like to reduce the execution time by 20%. This will, however, increasethe CPI by 25%. What clock rate do we need to obtain this amount of timereduction?Question: Suppose a program of 600 instructions runs on a 2 GHz processor. The frequency of instructions and the clock cycle counts per instruction are given as follows. What is the average CPI of this instruction mix? Operation Frequency Clock Cycles ALU operations 55% 1 Loads/Stores 30% 2 Branches 15% 3 Question: Continue from the previous question. What is the CPU time of the program in nanoseconds? Question: Suppose a processor P has a 2.5 GHz clock rate and a CPI of 1.5. If the processor executes a program in 3 microseconds, find the number of instructions in the program.Consider an unpipelined processor. Assume that it has 1-ns clock cycle and that it uses 4 cycles for ALU operations, and 5 cycles for branches, and 4 cycles for memory operations. Assume that the relative frequencies of these operations are60%,20%, and20%respectively. Suppose that due to clock skew set up, pipelining the processor adds0.2 nsof overhead to the clock. Ignoring any latency impact, how much speed up in the instruction execution rate will we gain from a pipeline? Please type answer no write by hend.

- Consider a CPU with clock cycle of 10ns that executes program A in 100 clock cycles and access the memory for 50 times during the execution. The CPU uses the cache with miss rate of 7% and Miss Penalty time of 40 ns. Compare the CPU execution time with and without Cache missAssume a 3GHz processor executes three classes of instructions(A, B, C).i. Calculate the average CPI for this sequence of program.ii. Calculate the execution time for this sequence of program.iii. If we use a system with four same processors, there will bespeed up by a factor of 4 for classes A and C, but class B willremain unaffected. Calculate the new execution time for thissystem. What is the overall speed up? Class A B C CPI for class 4 2 10 IC in sequence 100 200 300Q.Consider a computer system with DMA support. The DMA module is transferring one 8-bit character in one CPU cycle from a device to memory through cycle stealing at regular intervals. Consider a 2 MHZ processor. If 0.5% processor cycles are used for DMA, the data transfer rate of the device is bits per second.