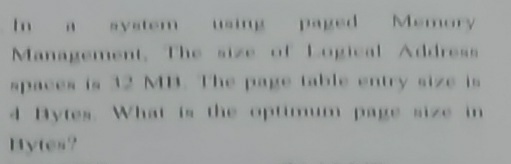

In aystem using paged Memory Management, The size ot Logical Address spaces is 12 MB The page table entry size is 4 Bytes What in the optinmum page size in Hytes?

Q: nanoseconds

A: Introduction: Speed up: Cache is the fastest memory by which a computer access its data for…

Q: A computer has a 64-bit virtual address, a 4 Kbyte page size, and page tables with four levels. How…

A:

Q: 1c) A computer has a 256 KByte, 4-way set associative, write back data cache with the block size of…

A:

Q: A system with byte addressable memory, 64-bit logical address,4 kilobyte page size and page entries…

A: Number of Entries in page table: 264/ 4Kb…

Q: A multiprocessor has a 3.3 GHz clock (0.3 nsec) and CPI = 0.7 when references are satisfied by the…

A: The effective CPI for the multiprocessor with 2% remote references is: CPI = Base CPI +…

Q: 1. Suppose a process page table contains the entries shown below. Using the format shown in Figure…

A: Over here we have asked how virtual memory mapped to physical memory.

Q: Consider a computer system that uses virtual memory with paging (no TLB). Suppose main access time…

A: Paging technique means dividing virtual memory into equal size partitions called pages and storing…

Q: A computer has an 8 GByte memory with 64 bit word sizes. Each block of memory stores 16 words. The…

A: Given that, Size of memory= 8 GB Word size= 64 bits Block size of memory= 16 words Number of blocks…

Q: Q2: a cache memory consists of 512 blocks, and if the last word in the block is 111111. I the last…

A: Considering the above scenario, Assume that Block size of main memory is 1KB Number of words in…

Q: A system has a page size of 1KB and maintains a page table for every process in the memory. The…

A: The answer is

Q: memory access time is 200 nanoseconds and average page-fault service time is 8 milliseconds, and you…

A: The Answer is

Q: In a virtual memory system, the size of virtual address is 32-bits and page size is 64KB . One page…

A: Pages are needed to store entire page table

Q: A cache block has 64 kbyte. The main memory has latency 64 usec and bandwidth 1 GBps. What is the…

A: For a 1 GBps bandwidth, loading 109 bytes on line takes 1 second, so 64 bytes will take 64*1/109=64…

Q: Timing is an issue in either segmented or paged address translation. Let's say a user needs to…

A: Security issues If the actual address is rendered available to I/0 devices in the specified…

Q: Assume we have 1 GB of physical memory. Inverted page table is used. Page size is 16 KB. Each entry…

A: In the inverted page table, indexing is done with respect to the frame number instead of the logical…

Q: A processor has an 30-bit physical address space (A memory address is 30-bit). It also has a…

A: I have answered all the 3 parts and have provided detailed solution in the image. First we will…

Q: Cache access time is 30 ns and main memory access time is 100 ns. What is the total memory access…

A: Effective memory access time = Cache hit ratio*(cache access time) + cache miss*(cache miss…

Q: Assuming that no page faults occur, the average time taken to access a virtual address is…

A: Hi there, Please find your solution below, I hope you would find my solution useful and helpful.…

Q: Assume you have a 8-way set associative cache having 16K lines each having capacity of 8 Bytes. A…

A: First of all, we need to determine what the index bits are and from above we know the offset is 9…

Q: The width of the physical address on a machine is 40 bits. The width of the tag field in a 512 KB,…

A: The width of the physical address on a machine is 40 bits. The width of the tag field in a 512 KB…

Q: Consider a computer with the following characteristics: total of 4 Mbyte of main memory; word size…

A: GIVEN THAT Given that- Maximum memory size = 1 MB. Word size = 1 Byte. Block size = 16 bytes…

Q: nsider a paging system with the page table stored in associative registers. emory reference takes…

A: paging system with the page table stored in associative registers. If a memory reference takes 200…

Q: In the demand paging memory, a page table is held in registers. If it takes 1000 ms to service a…

A: GIVEN:

Q: A computer has a 256 Kbyte, 4-way set associative, write back data cache with block size of 32…

A: 4-way set associative - 256 Kbyte Cache block size - 32 Bytes. Cache tag directory contains - 2…

Q: Cache/Memory Layout: A computer has an 8 GByte memory with 64 bit word sizes. Each block of memory…

A: Solution The address format can be computed in two format: 1. For memory addresses 8GB = 1GW (64…

Q: We have a paged virtual address system with the maximum size of virtual address space of 32 MB. The…

A: As per answering guidelines solving the first 3 sub question completely. A) Number of bits for…

Q: A 256 KB, direct-mapped write-back data cache with a block size of 32 Bytes is available on a…

A: A cache in the primary storage hierarchy contains cache lines that are grouped into sets. If each…

Q: How a physically addressed cache might beintegrated with virtual memory

A: Here have to determine about physically addressed cache might be integrated with virtual memory.

Q: a) A system implements a paged virtual address space for a process using a one-level page table The…

A: 1. Number of bits required for page table entry =log(number of pages in logical address space) =…

Q: Virtual Memory Address Space = 48 bits Physical Memory Address Space = 46 bits Page size = 4KB An…

A: A 48 bit virtual address can address 2 ^ 48 bytes. Page size = 4KB = 2^12 bytes Number of entries in…

Q: If memory access time is 200 nanoseconds and average page-fault service time is 8 milliseconds, and…

A: If memory access time is 200 nanoseconds and average page-fault service time is 8 milliseconds,…

Q: 1 GByte RAM with 64 word/line is mapped to an 8 kLine Cache with Associative Mapping. What will the…

A: 64-bit word means 8 byte.Line size: 8 words in a line, means 8 x 8 bytes = 64 bytes in a line = 26…

Q: If memory access time = 20ons and Average page fault time = 8 ms. If I access out of 1000 Causes a…

A: given data: memory access time=200ns average page fault=8ms effective access time=?…

Q: Define demand paging in memory management. What are the steps required to handle a page fault in…

A: Solution :: Demand paging follows that pages should only be brought into memory if the executing…

Q: A system with byte addressable memory , 64-bit logical address,4 kilobyte page size and page entries…

A: Solution : Given Logical Address : 64 kb page size : 4kb page entry : 4byte

Q: If a system has a 4-MB address space, where each page is 4 KB, and page table accesses take 100 nS,…

A: Given Data : Size of Address Space = 4 MB Size of the page = 4 KB One page tablet/page access…

Q: A system with byte addressable memory , 64-bit logical address,4 kilobyte page size and page entries…

A: Given Logical Address = 64 bits Logical address space= 264 B Page size = 4KB = 212B Page table…

Q: In a cache and memory system with the following characteristics: Direct Mapped 16 KByte 32 Byte…

A: Given Data cache = 16KB = 214B Memory address = 32 bits Block Size = 32 B =25B So, block offset=5…

Q: A computer has a 256 KHytes, 4-way set associative, write hack data cache with block size of 32…

A: According to the information given we have to find the number of bits in cache tag.

Q: source address to a destination address, 1 byte at a time. st = 0×5FC0, src = ®x1A10, length =…

A: It is defined as the address that is loaded into the memory-address register of the memory. A…

Q: A computer system has the segmented paging for virtual memory. The memory is byte addressable. Both…

A: Given data: virtual( Process size ) and physical address( Main Memory size) spaces : 216 bytes…

Q: A cache block has 64 kbyte. The main memory has latency 64 usec and bandwidth 1 GBps. What is the…

A: Given , Cache block size = 64 KB Main memory latency = 64 microsec. Bandwidth = 1 GBps We have to…

Q: A virtual memory has a page size of 16 words. There are 8 pages and 4 blocks. The associative memory…

A: Virtual Memory have:- Page size = 16 words Page number = 8 Block number = 4

Q: A virtual memory has a page size of 8 words. There are 16 pages and 4 blocks. The associative memory…

A: Virtual Address: A virtual address is a digital memory binary that allows a process to use a primary…

Q: A computer has a 256 KB, K-way set associative write-back data cache with block size of 32 B. The…

A: Introduction Given K-way set associative write-back data cache Cache size = 256 kB Block size 32…

Q: A main memory sized 8 GByte with 64 words/line is mapped to the following: a- A 16 KByte cache…

A: Below is the answer to above question. I hope this will meet your requirements...

Q: The hit rate of the memory closest to the ALU is increased from 75% to 80% in a practical cache…

A: Dear Student, Average memory access latency = Hit Time + Miss Rate * Miss Penalty In our question…

I need calculation must for this question

Need correct answer with calculation

Step by step

Solved in 2 steps with 1 images

- Consider the following page address stream: 2 1 4 3 5 3 2 4 5 2 1 2 4 3 1 Which of the following causes the most page faults to occur on a machine with 3 frames? Scheme that causes the most faults: a) First in First out b) LRU and FIFO are the same number of faults c) FIFO and Opitimal are the same number of faults d) All have the same number of faults e) Least Recently Used f) No faults occurs g) LRU and Optimal are the same number of faults h) Optimal NUMBER OF FAULTS CAUSED: a)Given the MAC address of an interface is F3:22:1F:20:30:40, what IPv6 link local address would be generated? a. FE80::F122:1FFF:FE20:3040/64 b. FE80::F322:1FFF:FE20:3040/64 c. FE80::F122:1F20:FFFE:3040/64 d. FE80::D322:1F20:FFFE:3040/64Given a Class C subnet Mask 255.255.255.192. what will be the subnet address and host number for a machine with IP address 197.1.2.67. Select one: a. second subnet and host 2 b. Third subnet and host number 3 c. second subnet and host 4 d. First subnet and host number 3 e. None f. Second subnet and host number 3

- A single screenshot of two consecutive curl showing the balancer in action (each request will be handled by a different server). The output should be like this: Student Name: Host: Remote Address: X-Forwarded-For: X-Forwarded-Proto: Server Address: Server Port:With the same physical memory and the same initial page assignments as in question 1, how many page faults will occur If LRU page replacement is used ? Assume the reference string (RS) is the same 0172327103? Time t 0 1 2 3 4 5 6 7 8 9 10 RS 0 1 7 2 3 2 7 1 0 3 Frame 0 0 Frame 1 1 Frame 2 2 Frame 3 3Consider a web page whose base file is of size S1 = 10 KB. Assume that the web page consists of N = 20 inline objects each of size S2 = 100 KB. Assume that the round-trip time to the web server is T = 100 ms and the bottleneck capacity is C = 10 Mbps. Ignore any packetization delays and header overhead.a. Assuming non-persistent HTTP is used with a single TCP connection, how long does it take to download the web page?b. Assuming non-persistent HTTP is used with 4 parallel TCP connections, how long does it take to download the web page?c. Assuming pipelined, persistent HTTP is used, how long does it take to download the web page? ”Pipelined” means requests for multiple objects can be sent back-to-back on the same connection.d. Assuming non-pipelined, persistent HTTP with 2 parallel TCP connections is used, how long does it take to download the web page? Assume that the 2 parallel connections equally share the total available bandwidth C.

- What is the maximum addressable host with the above NA? 10.23.0.0/16a) In a bus CSMA/CD network with a data rate of 10 Mbps, a collision occurs 20 µs after the first bit of the frame leaves the sending station. What should the length of the frame be so that the sender can detect the collision? b) There are only two stations, A and B, in a bus 1-persistence CSMA/CD network with Tp = 25.6 µs and Tr = 51.2 µs. Station A has a frame to send to station B. The frame is unsuccessful two times and succeeds on the third try. Draw a flowchart for this problem. Assume that the R is 1 and 2 respectively and ignore the time for sending a jamming signal.A host-to-host connection may transport a large number of packets. Please provide me with a breakdown of items load processing time. Should the duration of one delay be set while the length of the other be variable?

- You are assign to setup a real LAN network with 2 real servers PC with Centos. The nework IP address range selected from the network is 172.16.16.0/24.The two(2) servers to be setup is a FTP server (172.16.16.23) and a Web Server and DHCP Server setup in a VirtualBox environment in the 2nd server. WebServer(172.16.16.80) and DHCPServer(172.16.16.2).Show the instruction step by step to Setup the IP address of all the servers using the nmcli command.a) A nonpersistent web page with 13 items will load in ____ ms. RTT=9ms; Object Transmission Time=2*RTT). (ms answer) b) For a persistent connection, what would the computation yield? c) Does the computation incorporate all delays? Give reasonsConsider sending a 1300-byte datagram into a link that has a MTU of 500 bytes. Which of thefollowing is true? Please justify your answer.1. Three fragments are created with offsets 0, 500/8 1000/82. Three fragments are created with offsets 0, 480/8 and 960/8.3. Three fragments are created, with offsets 0, 460/8 and 920/8.4. None of the above