The following equation was suggested both for cache memory and disk cache memory Ts = Tc + M * Tp %3D Generally this equation to a memory hierarch' with N levels instead of just two levels.

Q: e system shown below, answer following questions CLK 3.3GHZ DATA BUS (16 bits) CPU ADDRESS BUS (23…

A: 1). 2address bus width Equals total addressable memory * The size of the data bus. For example, a…

Q: Section 5.5 states that modern server memory modules (DIMMs) employ SEC/DED ECC to protect each 64…

A: Given data: A single error correcting, double error detecting(SEC/DED) hamming code is present and…

Q: a. How many bits are required to address a 32M x 32 memory if: Main memory is byte addressable? 2^20…

A:

Q: For a memory with a 5bit wide address bus and a 32bit wide data bus, answer the followin uestions:…

A: A) Total number of distinct address = 2 address bus width = 25 = 32

Q: where R1, R2, and R3 are CPU registers, (R1) is the content of R1, a, ß,7, and are the starting…

A: We have , For each operations of given instruction code segment has number of instructions are:-…

Q: Answer the following questions. A. A computer system has a main memory access time as 60ns. you as a…

A: ANSWER:-

Q: 3) Assume SS=5000H, DS=600OH, ES=7000H, CS=9000H, BX=1000H, DI=2000H, SP=3000H, IP=4000H, SI=2000H,…

A: Given Instruction: MOV [DI + 3000H], AL. -> Here MOV means Move instruction. The content of…

Q: Q1. Suppose you are given with a ROM chip of size 1024*8 and 5 RAM chips of size 512*8. Show…

A: Answer: I have given answered in the handwritten format in brief explanation

Q: 3- Suppose that DS = 100H, SS = 300H, BP = 200H, and SI = 0100H, BX= 1500H . Determine the memory…

A: DATA Given:- DS=100H SS=300H SI=0100H BX=1500H Instruction : MOV DL,[BP+200] Operation : Real…

Q: How many bits are required to address a 8M × 16 main memory if a) Main memory is…

A: How many bits are required to address a 8M × 16 main memory if a) Main memory is…

Q: 1 Problem: Draw the complete diagram of a 256KX8 memory that uses RAM chips with the following…

A: Total # of 32Kx4 RAM Chips required = 256Kx8 / 32Kx4 = 8x2 = 16 These 16 chips will be arranged as 8…

Q: 2. Consider 2M x 8 SRAM memory block. (a) How many bits of data can be stored in this memory block?…

A: Disclaimer: “Since you have asked multipart questions, As per our company policy,we will only solve…

Q: 8.3 An Acc-ISA CPU executes the following instructions using 3-bit op-codes and 5-bit address or 2's…

A: Here is the answer:-

Q: Consider cache memory 90% hit ratio is required to be installed in a memory system to reduce the…

A: Given, Hit ratio = 90 % Then, Hit rate = 0.9 Miss rate = 1 - hit rate = 1 - 0.9 = 0.1 According to…

Q: 2. What is the resulting memory address for the following operands assuming the indicated values in…

A: Basics: A memory address is a reference to a particular memory area utilized at different levels by…

Q: The purpose of memory hierarchy is To reduce memory cost per bit To reduce average memory access…

A: We have memory hierarchy like Cache level 1 and then cache level 2 then main memory and finally…

Q: Can the virtual addresses 0x100000 and 0x100008 be mapped to 2 far apart locations in physical RAM?…

A: Answer is No

Q: 2-Suppose that DS = 100H, SS = 2000H, BP = 200H, and SI = 0100H, BX= 1500H. Determine the memory…

A: Solution Given , DS=100H SS=2000H BP=200H SI=0100H BX=1500H Instruction is : MOV AL , [ BX + 500 ]

Q: Assume, paging has been used as memory management technique and the page table is stored in memory…

A: Assume, paging has been used as memory management technique and the page table is stored in memory…

Q: For a system, RAM - 64KB, Block size - 4 bytes, Cache size - 128 bytes, Direct mapped cache.…

A: Given: RAM size = 64 KB Block size = 4 bytes Cache size = 128 bytes

Q: Following is the memory map begining from addre= ACOOH and increasing addresses to the right, all in…

A: It is defined as a unique identifier used by a device or CPU for data tracking. This binary address…

Q: 2. Design your own 16 bits Memory Map, and choose the amount of memory space required for various…

A: 16bit processor,16bit(word-sized), can address 64k of RAM. 220(1048576)bytes, so can construct 20bit…

Q: Why do we need cache memory when we already have RAM (Random Access Memory), which is a kind of…

A: Cache Memory: Data retrieval from the a computer's memory is made more effective by cache memory, a…

Q: What is the idea of Memory Segmentation ? O Having multiple base and bounds pair per CPU in the MMU.…

A: Here, we have to provide correct option for Memory segmentation.

Q: 12. Consider the following instruction: Instruction: AND Rd,Rs,Rt Interpretation: Reg[Rd] = Reg[Rs]…

A: The question is on choosing the correct option from the given options considering the given…

Q: Please solution with explain ЗFFE Question 1 A memory map shown in Fig-1 with the addresses of…

A: Question 1: Part A) Base address of EAROM=1000 (in hex) Number of location =2592=A20(in hex)…

Q: b) The average memory access time for a microprocessor with 1 level of cache L1 is 2.6 clock cycles.…

A: Explanation: Consider the expressiono for miss rate of L1 cache. Given that: Hit time = 1…

Q: Let cache of 0.7 hit having average access time 9 times faster than that of memory. If average…

A: Here in this question a cache with 0.7 hit is given with access time 9 times faster than memory…

Q: Function NSU-1 For a system, RAM-64KB, Block size-4 bytes, Cache sine- 128 bytes, Direct mapped…

A: RAM -64 KB Block size -4 byte Cache size 128 byte Hit ratio while using direct mapped cache: To…

Q: Problem4: A microcomputer has the following memory map: 4100 to 410F I/O 2100 to 22FF RAM 0000 to…

A:

Q: 1. An intel high performance processor is executing multiple processes simultaneously. The processor…

A: The hit ratio is calculated by divideing the number of cache hits with the sum of the number of…

Q: C) If you want to Design 8K-byte memory starting from (B000)H by using a memory chip with size (4096…

A: As per the answering guidelines, solving the first 3 question. 1. Number of 4096x2 chips required =…

Q: On the Motorola 68020 microprocessor, a cache access takes two clock cycles. Data access from main…

A: step: 1 of 2 Preconditions: One clock cycle = 60 ns Given that, Cache access takes two clock cycles,…

Q: Answer the question below based on given portion of the memory unit with a word size of 8 bits, and…

A: Provided below is the detailed step by step explanation for finding the missing fields in the memory…

Q: For a system, RAM - 64KB, Block size - 4 bytes, Cache size - 128 bytes, Direct mapped cache.…

A: Given: RAM size = 64 KB Block size = 4 bytes Cache size = 128 bytes

Q: b) Machine cycle defines a loop process with four major components. Explain why machine cycle is…

A: Machine cycle has 4 phases: Fetch - Decode - Execute - Store

Q: 5. How many bits are required to address a 4M X 16 main memory if a) main memory is byte…

A: Dear student, As per guidelines. I can do only first question with both subparts. Please repost your…

Q: Suppose you are given with a ROM chip of size 1024*8 and 5 RAM chips of size 512*8. Show…

A: The formula for calculating RAM devices: This chip has eight bits. Because one byte requires eight…

Q: Can the virtual addresses 0x100000 and 0x100008 be mapped to 2 far apart locations in physical RAM?

A: To map virtual addresses to physical RAM, page tables are used. Virtual address space of a process…

Q: Problem Given the following memory values and a one-address machine with an accumulator, what…

A: a) Immediate addressing mode loads the constant value 20 as an operand to accumulate. AC=20

Q: Design the memory mapping between the Cache memory of 64MB to the main memory of 4 GB using 8 way…

A: For a 8-Way associative cache allows placement in any block of a set with 8 elements• 8 is the…

Q: Let (BX)=100H, DI=200H, DS=1200H, SI= FO02H, AX= 0105H, and the following memory content. what is…

A: Solution:

Q: Question 1: (a) Draw and Explain Memory Hierarchy. (b) Explain the three techniques of mapping…

A: Memory Hierarchy: The memory in a computer can be divided into five hierarchies based on the speed…

Q: Following is the memory map beginning from address 3C00H and increasing addresses to the right, all…

A: These instructions are used to transfer the data from the source operand to the destination operand.…

Q: Q1: Fill with the required information assuming that memory byte addressable using:

A: I have solved the problem & filled the table in the two ways mentioned in the question. If you…

Q: For a system, RAM - 64KB, Block size - 4 bytes, Cache size - 128 bytes, Direct mapped cache.…

A: Given:

Q: Compare between the following techniques that are used for computer memory cache: (A) Direct-mapped.…

A: In cache memory there are three types of mappings that are: Direct mapping Fully associative…

Q: A recent paper proposed eliminating paging and using segmentation instead. Their reasoning was that…

A: The design of RISC-V instruction sets is modular. Rather than take the approach of a large and…

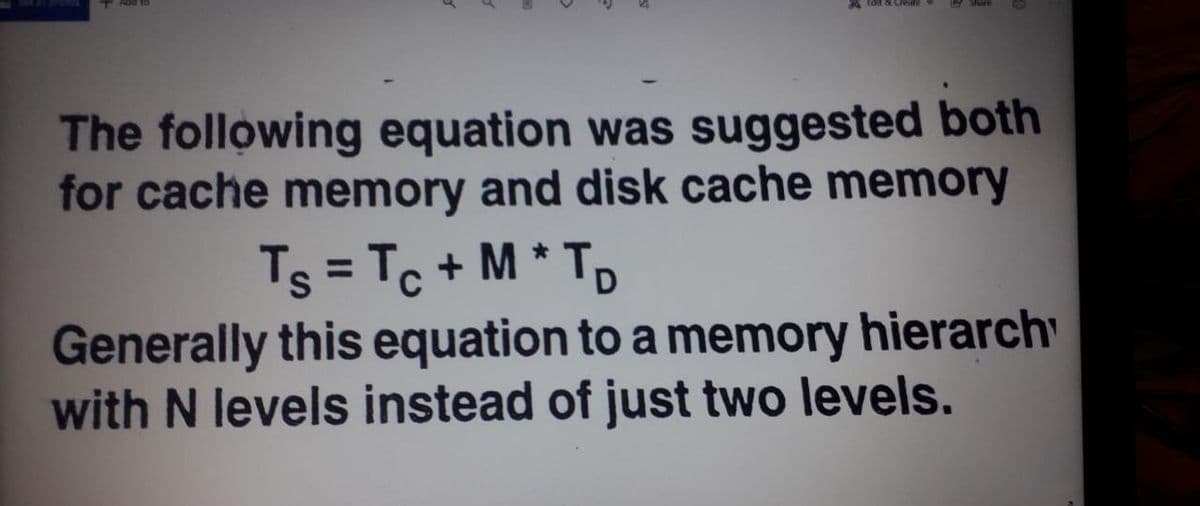

Q: The following equation was suggested both for cache memory and disk cache memory Ts = Tc + M* T,…

A: The Answer is

Trending now

This is a popular solution!

Step by step

Solved in 2 steps with 1 images

- Suppose that 16M × 16 memory built using 512K × 8 RAM chips and that memory is word addressable.1. a) How many RAM chips are necessary?2. b) If we were accessing one full word, how many chips would be involved? 3. c) How many address bits are needed for each RAM chip?4. d) How many banks will this memory have?5. e) How many address bits are needed for all memory?6. f) If high-order interleaving is used, where would address 14 (which is E in hex) be located?7. g) Repeat exercise 9f for low-order interleaving.Memory address translation is useful only if the total size of virtual memory (summed over all processes) needs to be larger than physical memory. True or False. Justify your answer.Please calculate the total clock cycles for each functionseperately then calculate how much faster would the functions be if a better data cache reduced the average memory operations time to 4 cycles? Code: # Calculating Fibonacci numbers# fib(0) = 0# fib(1) = 1# fib(n) = fib(n-1)+fib(n-2).text.globl mainprint_str:li $v0, 4 # print string at ($a0)syscall #jr $ra # return; print_eol:la $a0, eol # print "\n"li $v0, 4 #syscall #jr $ra # return; print_int:li $v0, 1 # print integer ($a0)syscall #jr $ra # return; # fib(n) - recursive function to compute nth Fibonacci number#fib: sub $sp,$sp,12 # save registers on stacksw $a0, 0($sp) # save $a0 = nsw $s0, 4($sp) # save $s0sw $ra, 8($sp) # save $ra to allow recursive calls bgt $a0,1, gen # if n>1 then goto generic casemove $v0,$a0 # output = input if n=0 or n=1j rreg # goto restore registers gen: sub $a0,$a0,1 # param = n-1jal fib # compute fib(n-1)move $s0,$v0 # save fib(n-1) sub $a0,$a0,1 # set param to n-2jal fib # and make recursive…

- Explain why various memory management techniques, such as base/bounds and paging, have difficulty with asynchronous I/O operations.Because volatile RAM (Random Access Memory) already exists, what's the point of using a slower, less reliable cache memory instead?The electrical components called transistors are used in both random access memory (RAM) and cache memory. To what extent, if at all, can a computer get by with using just one kind of memory to carry out all of its functions?What is the point of using cache memory if we already have volatile RAM (Random Access Memory)?Transistors are used in both random-access memory (RAM) and cache memory. Is it conceivable, if at all possible, to employ just one kind of memory to carry out all of a computer's functions?

- Suppose that a 32M X 32 memory built using 512K X 8 RAM chips and memory is word-addressable. 1) How many RAM chips are necessary? 2) If we were accessing one full word, how many chips would be involved? 3) How many address bits are needed for each RAM chip? 4) How many banks will this memory have? 5f) If high-order interleaving is used, where would address 0x11011 be located? (Answer should be: bank# & offset#)Assume a cache memory hit ratio is 93% and the hit time is one cycle, but the miss penalty is 40 cycles. Then, Compute the average memory access time (AMAT)Suppose that a 64M x 16 main memory is built using 512K × 8 RAM chips and memory is word-addressable. a) How many RAM chips are necessary?b) If we were accessing one full word, how many chips would be involved?c) How many address bits are needed for each RAM chip?d) How many banks will this memory have?e) How many address bits are needed for all of memory?f) If high-order interleaving is used, where would address 32(base 10) be located? (Your answer should be "Bank#, Offset#")g) Repeat (f) for low-order interleaving.

- Cache memory seems unnecessary if RAM and cache memory both use transistors for storage. Can one single memory type be used for everything?You play the role of the instructor of CPSC440. Your CPSC440 students need more practice on the cache memory concept. You, as a professor of the CPSC440 course, decide to solve one more cache memory access problem (in addition to two problems in our Assignment). The new problem is: You are given a direct-mapped cache of 4 blocks with four-word per block (a total of 16 words in the cache). The main memory size is 64 words. We have the following memory access sequence: Word1, Word 8, Word0, Word 17, Word 14, Word 62, Word 55, Word 25, Word 16, and Word 15. You need to write an essay that explains how you solve this problem. You also need to show your students the final cache content using the given table shown below.You also need to explain to your students the result of hit or miss for each word access.A computer is using a fully associative cache and has 216 bytes of main memory (byte addressable) and a cache of 64 blocks, where each block contains 32 bytes. a. How many blocks of main memory are there? b. What will be the sizes of the tag, index, and byte offset fields? c. To which cache set will the memory address 0xF8C9(hexadecimal) map?