Update the contents of memory and/or registers for LDMDB SP!, {r8-r10}: Ox8000 = 0x00 Ox8001 = 0x00 Ox8002 = 0×BE Ox8003 = OXBA Ox8004 = 0x00 Ox8005 = 0x00

Update the contents of memory and/or registers for LDMDB SP!, {r8-r10}: Ox8000 = 0x00 Ox8001 = 0x00 Ox8002 = 0×BE Ox8003 = OXBA Ox8004 = 0x00 Ox8005 = 0x00

Chapter11: Operating Systems

Section: Chapter Questions

Problem 22VE

Related questions

Question

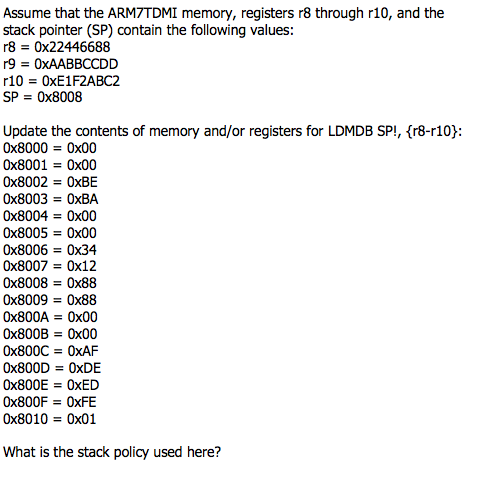

Transcribed Image Text:Assume that the ARM7TDMI memory, registers r8 through r10, and the

stack pointer (SP) contain the following values:

r8 = 0x22446688

г9 %3D ОхААВВССDD

r10 = 0XE1F2ABC2

SP = 0x8008

Update the contents of memory and/or registers for LDMDB SP!, {r8-r10}:

Ox8000 = Ox00

Ox8001 = Ox00

Ox8002 = OXBE

Ox8003 = 0XBA

Ox8004 = 0x00

Ox8005 = 0x00

Оx8006 %3D Ох34

Ox8007 = Ox12

Ox8008 = Ox88

Ox8009 = 0x88

Оx800A %3D Ох00

Ох800B %3D Ох00

Ox800C = 0XAF

OX800D = OXDE

OX800E = OXED

OX800F = OXFE

Ox8010 = Ox01

What is the stack policy used here?

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning