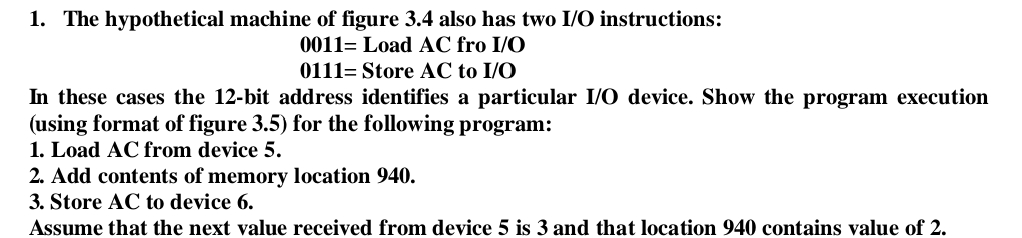

1. The hypothetical machine of figure 3.4 also has two I/O instructions: 0011= Load AC fro I/O 0111= Store AC to I/O In these cases the 12-bit address identifies a particular I/O device. Show the program execution (using format of figure 3.5) for the following program: 1. Load AC from device 5. 2. Add contents of memory location 940. 3. Store AC to device 6. Assume that the next value received from device 5 is 3 and that location 940 contains value of 2.

1. The hypothetical machine of figure 3.4 also has two I/O instructions: 0011= Load AC fro I/O 0111= Store AC to I/O In these cases the 12-bit address identifies a particular I/O device. Show the program execution (using format of figure 3.5) for the following program: 1. Load AC from device 5. 2. Add contents of memory location 940. 3. Store AC to device 6. Assume that the next value received from device 5 is 3 and that location 940 contains value of 2.

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 2PE: If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the...

Related questions

Question

WILL DOWNVOTE IF COPIED OTHER ANSWER

Transcribed Image Text:1. The hypothetical machine of figure 3.4 also has two I/O instructions:

0011= Load AC fro I/O

0111= Store AC to I/O

In these cases the 12-bit address identifies a particular I/O device. Show the program execution

(using format of figure 3.5) for the following program:

1. Load AC from device 5.

2. Add contents of memory location 940.

3. Store AC to device 6.

Assume that the next value received from device 5 is 3 and that location 940 contains value of 2.

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 3 steps with 1 images

Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning