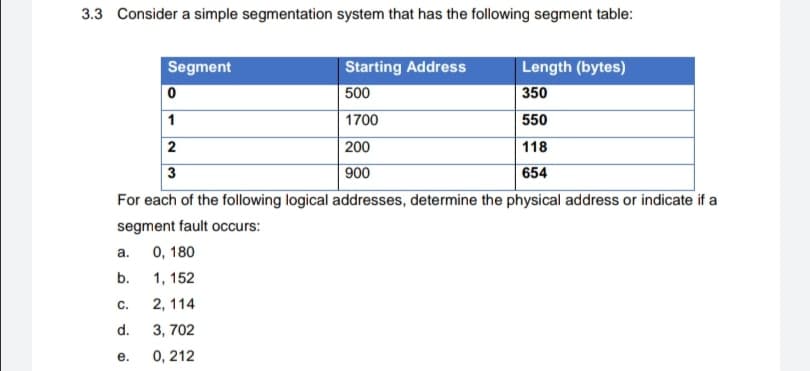

3.3 Consider a simple segmentation system that has the following segment table: Segment |Starting Address 500 Length (bytes) 350 1700 550 2 200 118 3 900 654 For each of the following logical addresses, determine the physical address or indicate if a segment fault occurs: a. 0, 180 b. 1, 152 C. 2, 114 d. 3, 702 0, 212 e.

Q: 2) Assuming X22 has 7000, what address will be stored in X9 by: LDUR X9, (X22, #7] a) 7000 b) 7007…

A: According to the information given:- we have to find out the correct option on the basic of LDUR X9,…

Q: Assume X address is 29D, find the value of AX for each of the following instruction .Data X byte 12,…

A: Given:

Q: Problem-5 A CAN node picked up the following raw bit patterns, including the stuff bits, from its…

A: a) we should consider the highest group of bit in a Destuffed bit sequence, Here the highest group…

Q: Assume that your ultra-low-cost processor doesn't have the hardware budget for an integer multiplier…

A: The instruction written here is the multiplication of two numbers but not using mul op code.

Q: [b] Consider the following portion of memory with a starting address of 80000H (referenced by Val1).…

A: Here, I have to provide a solution for the above question.

Q: 1. Suppose the Vole memory cells from addresses 0x00 to 0x05 contain the bit patterns given in the…

A: According to the Bartelby guideline we are suppose to answer only one question at a time. Kindly…

Q: Suppose that DS=300H, SS=200H, CS=100H, CX=AF39H, ARRAY=D3A4H, IP=5A76H, DI=245AH, SP-5489H,…

A:

Q: For this assignment, you are to write a MIPS assembly language program using the MARS IDE and assume…

A: Answer :

Q: An integer array [119,117,17,64] is stored in memory. Each integer has 32 bits. Suppose the first…

A: .dataArray : .word 68,251,88,204,126.globl main.textmain:#load index of arrayla $t9,Arrayli $t0,0…

Q: On a system using simple segmentation, compute the physical address for each of the logical…

A: In a segmentation scheme, the generated logical address consists of two parts: Segment number…

Q: (3) (a) Consider the following interaction with Python: x= [1,2,34 ,5,6, np.nan] y=…

A: Solution: Code: import numpy as np import pandas as pd x=[1,2,34,5,6,np.nan]…

Q: What value is stored in 0x10000008 on a MIPS (big-endian) machine? Q2: What value is stored in…

A: All computers do not store the bytes that comprise a multi-byte value in the same order. Consider a…

Q: Assume that your ultra-low-cost processor doesn't have the hardware budget for an integer multiplier…

A: Answer:)

Q: Assume that DS=4500n, SS=2000n, BX =2100n, Sl=1486, DI 8500, BP=7814n, and AH=25n. 1-Show the PA…

A: Given Data: DS= 4500, SS= 2000, BX =2100, SI = 1486, DI = 8500, and BP = 7814 PA Location of…

Q: Assume that DS=D4500h, SS=2000n, BX =2100, Sl=1486, DI 8500r, BP=7814h, and AH=25h. 1-Show the PA…

A: Given: We are given a problem in which multiple registers with their content are given. Goal: We…

Q: Consider the following segment table: What are the physical address for the following logical…

A: THIS IS A MULTIPART-BASED PROBLEM. ONLY THE FIRST THREE PARTS ARE SOLVED. KINDLY SEND THE REMAINING…

Q: 3.3 Consider a simple segmentation system that has the following segment table: Segment Starting…

A: Hey, since multiple sub parts questions posted, we will answer first three question according to our…

Q: Example#20:A computer system has consisting of 16 MB 32-bit words. It also has an 8 KB cache. Assume…

A: Given that, Main memory size= 16 MB Cache size= 8 KB 1 word= 32 bits (a) Block size= 1 word= 32…

Q: What are the values stored in memory address [1200] and [1400] after execution, respectively ? MOV…

A: Solution: MOV AL,[1200] will load 25h value in AL register MOV AH,AL will load 25h value…

Q: Q2: Suppose that DS-0201h, BX= 300h, and DI- 400h determine the memory address accessed by each of…

A: First, convert all the Hexadecimal numbers into decimal numbers. DS, BX, DI, AL, AX, BI are like…

Q: Ex 1. Show how the following values would be stored by byte-addressable machines with 32-bit words,…

A: Show how the following values would be stored by byte-addressable machines with 32-bit words, using…

Q: 1. Suppose 8 bit registers have following contents X=00001111 Y=10101010 Z= 11011011 W=00110011 What…

A: The gate OR is equal to the input AND gate. The gate OR gate is the same size as the NAND gate…

Q: 6. Suppose we are given the following subset of codewords, created for a 7-bit memory word with one…

A: • Parity bit:An Parity bit is a little, affixed at the LSB (Least Significant Bit) side of the given…

Q: 2. Answer all the questions given below. (a) -For the given code segment, find the value of ax [CO2]…

A: a.(i) From the question we know that ax register is in hexadecimal form and hence a register is…

Q: Suppose we have the main memory following Big Endian ordering and it is shown in the following…

A: The value(in signed decimal form) will be stored in the t3 register is

Q: Consider an equation, W = (X + Y ) * Z is run using CISC one address format and illustration of its…

A: We need to find the result and storage location of result for the given code.

Q: Q4) Let there be given a 16 word, 64 kw Main Memory and 128 line cache. Find the corresponding bits…

A: - we have been given the the word size as 16 word the main memory as 64 word and the cache size is…

Q: 9. If we have AX-8A3C H, CL-02 H. the result of performing SAL AX,CL is: a. C51E H c. 451E H b. E28F…

A: Answer 9) in the question option is not right the correct answer is: 28F0. explanation:

Q: Answer only 3 and 4 Suppose memory has 256KB, OS use low address 20KB, there is one program…

A:

Q: Consider the following segment table (all expressed and addressed in bytes) Segment Base Length 0…

A: Find the required answer given as below :

Q: 1. The hypothetical machine of figure 3.4 also has two I/O instructions: 0011= Load AC fro I/O 0111=…

A: Given:

Q: we have not provided for any type of error handling, such as if the address on the address lines…

A: Given Table:

Q: Suppose, 3BD15 H is a particular physical location, and 1234 is the value of the offset.What should…

A: Answer is given below .

Q: WRITE A PROGRAM WITH FOUR COLUMNS: RANKINE(R), CELSIUS(C), FARENHEIT(F) & KELVIN (K).

A: #include <iostream>using namespace std; int main(){ float fah, cel; cout << "\n\n…

Q: Suppose we have two 2-dimensional arrays a and b, and consider the following C code. int a[4][4];…

A: Here we have given the cache misses wrt to array a and b. You can find the solution in step 2.

Q: Assume SS=5000H, DS=6000H, ES=7000H, CS=9000H, BX=1000H, DI=2000H, BP=3000H, IP=4000H, SI=2000H, the…

A: Given: We are given various registers with values stored in them. Register such as SS, DS, ES, CS,…

Q: Suppose that DS=300H, SS=200H, CS=100H, CX=AF39H, ARRAY=D3A4H, IP=5A76H, DI=245AH, SP=5489H,…

A:

Q: Let's tabulate that, and then extend the concept to fill in the blank cells: Memory |сарacity…

A: Answer for above question is given below - 1073741824 220 ,230 10 ,20 ,30 1048575 ,107374183

Q: Assume we have a direct-mapped cache with 64 blocks and each block consists of 16 bytes, the cache…

A: There are a total of 8/16 bytes = 512 rows inthe repository. The repository, therefore, contains 256…

Q: Question 1: Write down the corresponding MIPS machine language of the following assembly language…

A: Given: Question 1: Write down the corresponding MIPS machine language of the following assembly…

Q: Suppose the following code fragment is executed and that the data word that is allocated and…

A: Dear Student, addi (add immediate) will add $0 with M and will store it in $1. We also know $0…

Q: Question 2 Consider the following fragment of C code: for (i=0; i<100; i++) { A[i] =B[i]+C; } Assume…

A: MIPS CODE for the above code mentioned: DADD R1, R0, R0 ; R0 = 0; initialise i = 0 SW R1, 7000(R0);…

Q: 3. Suppose the Vole memory cells at addresses OxA4 to OXB1 contain the bit patterns given in the…

A: THe solution for the above given question is given below:

Q: For a computer system, which utilizes pure segmentation, segmentation table and list of virtual…

A: Given that we have segment table above and list of virtual addresses are given above: what are the…

Q: [1.3] Consider following sequence of instructions, and assume that it is executed on a five-stage…

A: Pipelining: It is a process in which the existing CPUs are arranged in a way that performance is…

Q: Let the virtual address be V bits and the virtual addtess space be byte-addressable, the page size…

A: D) Total number of virtual memory bits to be translated is V bits.

Q: Prog1 request 80KB, prog2 request 16KB, Prog3 request 140KB Prog1 finish, Prog3 finish; Prog4…

A: Memory Memory is the electronic holding place for the instructions and data of a computer needs to…

Q: Consider a simple segmentation system that has the following segment table: Starting Address Length…

A: Given, Segment table: Segment Number Starting Address Length (Bytes) 0 830 346 1 110 110 2…

Q: Consider two integer arrays B and D of 100 elements. Let X2 and X3 contain the base address of array…

A:

Q: Consider two word wide unsigned integers where one is stored at the physical memory address…

A: Given that, The two word wide unsigned integers where one is stored at the physical memory address…

Trending now

This is a popular solution!

Step by step

Solved in 6 steps

- Answer only 3 and 4 Suppose memory has 256KB, OS use low address 20KB, there is one program sequence: (20) • Prog1 request 80KB, prog2 request 16KB, • Prog3 request 140KB • Prog1 finish, Prog3 finish; • Prog4 request 80KB, Prog5 request 120kb • Use first match and best match to deal with this sequence • (from high address when allocated) • (1)Draw allocation state when prog1,2,3 are loaded into memory? • (2)Draw allocation state when prog1, 3 finish? • (3)use these two algorithms to draw the structure of free queue after prog1 , 3 finish(draw the allocation descriptor information,) • (4) Which algorithm is suitable for this sequence ? Describe the allocation process?Q3 Consider a swapping system in which main memory contains the following hole sizes in memory order: 10K, 4K, 20K, 18K, 7K, 9K, 12K, and 15K. Which hole is taken for successive segment requests of (a) 12K, (b) 10K and (c) 9K for Next-Fit? Assume the last allocated hole is 20K.Consider a virtual memory system that can address a total of 32 bytes. You have unlimited hard disk space, but are limited to only 16MB of semiconductor (physical) memory. Assume that virtual and physical pages are each 4 KB in size. What is the total size of the page table in bytes? (Assume that, in addition to the physical page number, each page table entry also contains some status information in the form of a valid bit (V) and a dirty bit (D)).

- Let's pretend for a moment that we have a byte-addressable computer with fully associative mapping, 16-bit main memory addresses, and 32 blocks of cache memory. The following holds true if each block is 16 bits in size:a) Determine how many bytes the offset field is.Measure the tag field's width and height in pixels (b).1. Suppose 8 bit registers have following contentsX=00001111Y=10101010Z= 11011011W=00110011What will be the 8 bit values of each register after execution of following sequences ofmicrooperations ?X ← ? + ?Z←Z⋀ ?, ? ← ? + 1X←X-ZSuppose we have a byte-addressable computer using direct mapping with 16-bit main memory addresses and 32 blocks of cache. If each block contains 16 bytes. a. Determine the number of bits of the offset field. b. Determine the number of bits of the block (or slot) field. c. Determine the number of bits of the tag field. d. To which cache block would the hexadecimal address 0x2468 map? e. What is the tag of the hexadecimal address 0x2468 f.To which cache block would the hexadecimal address 0x864A map? g. What is the tag of the hexadecimal address 0x864A?

- Consider a swapping system in which memory consists of the following hole sizes inmemory order: 12 MB, 4 MB, 20 MB, 12 MB,18 MB, 7 MB, 9 MB and 12 MB.Which hole is taken for successive segment requests of(a) 10MB(b) 15MB(c) 9 MBfor first fit, worst fit, and next fit?Suppose a computer system uses 16-bit addresses for both its virtual and physical addresses. In addition, assume each page (and frame) has size 256 bytes. 8 bits are used for offset, 8 bits are used for page # and the max number of pages a process can have is 256. e. Translate the following virtual addresses to physical addresses, and show how you obtain the answers. (Hint: You do not need to convert hexadecimal numbers to decimal ones.) 0x0389 0xDF78 0x0245 0x8012 f) Now, suppose that the OS uses a two-level page table. Draw the page table. (Assume that frames 7 through 221 are free, so you can allocate space for the page table there.) In addition, suppose that the page-table directory storage comprises a whole number of consecutive full frames. (For examples: if the directory entry is 2 bytes, the entry’s storage comprises 1 frame; if the directory entry is 260 bytes, the entry’s storage comprises 2 consecutive frames.) g)What is the size of the two-level page table…Suppose we have a system with the following properties:The memory is byte addressable.Memory accesses are to 1-byte words (not to 4-byte words).Addresses are 13 bits wide.The cache is 4-way set associative (E = 4), with a 4-byte block size(B = 4) and eight sets (S = 8).Consider the following cache state. All addresses, tags, and valuesare given in hexadecimal format. The Index column contains the set index for each set of four lines. The Tag columns contain the tag value for each line. The V columns contain the valid bit for each line. The Bytes 0−3 columns contain the data for each line, numbered left to right starting with byte 0 on the left. A. What is the size (C) of this cache in bytes?B. The box that follows shows the format of an address (1 bit perbox). Indicate (by labeling the diagram) the fields that would beused to determine the following:CO. The cache block offsetCI. The cache set indexCT. The cache tag

- (Practice) Although the total number of bytes varies from computer to computer, memory sizes of millions and billions of bytes are common. In computer language, the letter M representsthe number 1,048,576, which is 2 raised to the 20th power, and G represents 1,073,741,824, which is 2 raised to the 30th power. Therefore, a memory size of 4 MB is really 4 times 1,048,576 (4,194,304 bytes), and a memory size of 2 GB is really 2 times 1,073,741,824 (2,147,483,648 bytes). Using this information, calculate the actual number of bytes in the following: a. A memory containing 512 MB b. A memory consisting of 512 MB words, where each word consists of 2 bytes c. A memory consisting of 512 MB words, where each word consists of 4 bytes d. A thumb drive that specifies 2 GB e. A disk that specifies 4 GB f. A disk that specifies 8 GBCA_10 Let the virtual address be V bits and the virtual addtess space be byte-addressable, the page size be P KB (and P is a power of 2), and the the main memory size be MM MB(where [MM MB]) is divide into [P KB]). (d)How many of the virtual memory bits need to be translated? (e) How many bits will be produced if the virtual-to-pyysical address translation is "successful" (f) How many bits does a physical address have, and how are each of these bits obtained?Fill in blank Suppose that linear page table is used where the memory addresses are 12-bit binary numbers and the page size is 256 bytes. If a virtual address in binary format is 101000011100, then the VPN (virtual page number) in binary format will be ---------