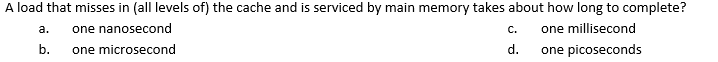

A load that misses in (all levels of) the cache and is serviced by main memory takes about how long to complete? one nanosecond C. one millisecond a. one microsecond d. one nicoseconds

Q: A CPU's clock rate is 4 GHz. This CPU's cache hit time is measured as 1 clock cycle, the miss…

A:

Q: What should happen if the processor submits a request that is denied in the cache while the write…

A: Introduction: The processor may refer to: (computing) The central processing unit (CPU) of a…

Q: You are given Byte-addressable Main Memory (MM) size 8GB, Block size 8KB, Number of Tag bits 10.…

A: Here in this question have given Main memory size = 8GB. Block size = 8 KB. Tag bit = 10 Find =…

Q: Design a direct-mapped cache with 128 KB that uses 32-bits and 16 bytes per block. Calculate: -How…

A: Given: Cache size = 128kb Pysical address = 32-bits Block Size = 16 bytes.

Q: What is the difference between a TLB, a page table, and a cache in a limited memory system?

A: Introduction: A translation lookaside buffer (TLB) is a memory reserve used to reduce the time it…

Q: Suppose a computer using fully associative cache has 224 bytes of byte-addressable main memory and a…

A: Size of tag and offset fields The memory with 224 bytes consists of 24 addressable bytes. Hence 24…

Q: Assume a cache memory hit ratio is 93% and the hit time is one cycle, but the miss penalty is 40…

A:

Q: Consider a system with 20 requests and out of 20 , 4 requests are already in cache memory. What will…

A: Introduction Consider a system with 20 requests and out of 20 , 4 requests are already in cache…

Q: A cache hit is when the desired data is already located in the cache RAM. O True False

A: There is a significant gap between processor speed and cache speed. to reduce this gap Cache Memory…

Q: What is the format of a memory address as seen by the cache; that is, what are the sizes of the tag…

A: Introduction: We must determine the format of a memory address as seen by the cache and the sizes of…

Q: The width of the physical address on a machine is 30 bits. The width of the tag field in a 64 KB, 16…

A: Given Data : Bits for physical address = 30 bits Width of tag field = 64 KB Set associativity = 16…

Q: Show work and type answer please. Suppose a computer using fully associate cache has 2G Bytes of…

A: In this question, we are given a fully associative cache with main memory and block size. We are…

Q: Consider a computer with 4 levels of memory. Calculate the average memory access time, given the…

A: Given that the computer contains 4 levels of memory. That are: Cache 1 Cache 2 RAM HDD If the data…

Q: What should happen if a request from the processor reaches the cache while a block from the write…

A: Introduction: The cache are going to be able to meet the request as a result of otherwise, it's idle…

Q: Explain the consequences of having a computer without an operating system. What is the purpose of an…

A: Introduction: The operating system manages all of the system's core functions and all of the utility…

Q: The write buffer returns a block to main memory while the processor issues a request that cannot be…

A: The above question is solved in step 2 :-

Q: memory. What is the total numbe - 4 4 way set associative cache?

A:

Q: A block from the write buffer is being sent back to main memory, and the processor makes a request…

A: When a Processor needs to comment, it first checks to see if the address to which it needs to write…

Q: Q2: a cache memory consists of 512 blocks, and if the last word in the block is 111111. I the last…

A: Considering the above scenario, Assume that Block size of main memory is 1KB Number of words in…

Q: A memory system consists of a cache and a main memory. It takes 25ns to access the cache, and 100ns…

A: Answer the above question are as follows

Q: If the RAM has a two byte data word and address bits are grouped for direct mapping with a cache…

A: The memory bits are organized as Tag(14) index(9) offset(5)

Q: What are the benefits that come with using a cache that does not block?

A: What are the benefits that come with using a cache that does not block answer in below step.

Q: Question 1 Listen Cache memory is faster than the registers. True False Question 2 Listen The…

A: Here in this multiple question we have asked weather the statement is true or false..

Q: What is the definition of a write-through cache?

A: Solution - In the given question, we have to define write-through cache.

Q: 5. Your system has an 8-way set associative cache and addresses and data of length 16 bits. The…

A: Since it is given that set index bits are 9, we have Total sets = 29 = 512

Q: Suppose a computer using fully associative cache has 224 bytes of byte-addressable main memory and a…

A: Offset bits = log (2^6) = 6 bits.

Q: The lastest data access is provideu DRAM's. A B SRAM's. C Registers. Caches. D

A: Please find the answer below

Q: Cache memory may seem unnecessary if we already have RAM (random access memory), which may be…

A: The Answer is in step-2.

Q: If the hit ratio of a cache memory is 0.7, what is its miss ratio? (write only the numerical value)

A: EXPLANATION: Cache MISS RATIO = 1 - HIT RATIO

Q: Vhat is the Average Access Time for a machine with the Cache rate of 80% and cache ccess time of 5ns…

A: The answer is...

Q: How does the CPU search an instruction or data in cache in case of direct mapping? List the steps in…

A: In direct mapping, each block of main memory is mapped into only a single cache line possible. The…

Q: answer the following question regarding cache and virtual memory:

A: cache model is good to use to determine the popularity of web page

Q: Cache manager improves the performance of a. Programmed I/O b. File base I/O c. I/O device d. I/O…

A: Answer is b) File base I/O

Q: In aystem using paged Memory Management, The size ot Logical Address spaces is 12 MB The page table…

A: The answer for optimum page size in bytes are

Q: A given computer has a single cache memory (off-chip) with a 2 ns hit time and a 98% hit rate. Its…

A: The effective time here is just the average time using the relative probabilities of a hit or a miss…

Q: Q5:35i Given a memory hierarchy with two levels of cache, L1 and L2, a main memory, and the…

A: Given: L1 access time = 1 L2 access time = 10 L1 miss rate = 10% or 0.1 L2 miss rate = 1% or…

Q: A cache has a line size of 64 bit. to determine which bytes within a cache line an address point to,…

A: Answer :

Q: What are the advantages of using a nonblocking cache?

A: Introduction: Non-blocking caches are those that can handle several memory requests at the same…

Q: Suppose a computer using fully associative cache has 2^24 bytes of byte-addressable main memory and…

A: Full associative cache size=224 bytes.Size of each block=64 bytesBlocks of main memory=cache…

Q: During this time, what should happen if the processor sends a request that isn't met in the cache?…

A: Introduction: The cache is a term that primarily refers to something that is concealed or stored…

Q: Suppose that a cache is 20 times faster than main memory and cache memory can be used 80% of the…

A:

Q: A computer has a cache, main memory, and a disk used for virtual memory. If a referenced word is in…

A:

Q: What happens if the processor sends a request to the cache while a write buffer block is being…

A: Introduction: The cache will be able to satisfy the request since it will be idle while the writing…

Q: What is the format of a memory address as it is viewed by the cache; that is, what are the sizes of…

A: According to the provided information, We have to find out the format of a memory address as it is…

Q: Aside Cache lines, sets, and blocks: What's the difference?

A:

Q: d cache of size 32 The CPU generate: per of bits needec umber of tag bits

A:

Q: The hit rate of the memory closest to the ALU is increased from 75% to 80% in a practical cache…

A: Dear Student, Average memory access latency = Hit Time + Miss Rate * Miss Penalty In our question…

Step by step

Solved in 2 steps

- The caches are valuable for two reasons: how do they address the problem? Are they causing any problems? So, if it's possible to create a cache that's the same size as the device it's caching for (for example, a disk cache), why not do that, and remove the device?Aside Cache lines, sets, and blocks: What's the difference?Design a Cache memory for your Project for a direct-mapped cachewith 1MB of data .• Design a Cache memory for your Project for a direct-mapped cachewith 64KB of data .Assume n-word block size, assuming a N-bitaddress? N=19 n=5

- There are a few different reasons why caches are useful. What exactly is the point of all of their hard work? What are the repercussions of making use of them? Why not simply make the cache the same size as the device it is caching, in the event of a cache (for example, a whole hard drive)?The caches are valuable for two reasons: Why do they exist? How do they affect the environment? The question is, if a cache can be made as big as the device it caches (for example, a disk cache), why not make it that huge and remove the device?. For an 8-wordwide cache with the following access times, calculate the effective bandwidth. L1: 2 bus cycles,L2: 100 bus cycles Detailed answer please. Thank you

- Compare in detail in the table the difference between: Cache memory and main memory and register ? 1-LOCATION 2-VOLATILITY 3-ACCESSIBILITY 4-FUNCTION 5-HARDWARE STRUCTURE 6-COST 7-SIZE 8- WRITING SPEED 9-STORAGE LIMIT You must write the references and put the link to them???.Can you explain why CMOS RAM is preferable to alternative methods of storing configuration data like jumpers or switches?Can you describe the hierarchy of a real cache and how it works?

- 1. an off chip cache might be reasonably be how big a. 4kb b. 256kb c. 4mb d. 256mb 2. such a cache is most likely to be a. 4-way associative b. 16-way associative c. fully associatie d. direct-mapped 3. a page fault that forces a read from a disk takes about how long to complete? a. 10millis b. 100millis c.100micros d. 10microsAssume there is a PCI buffer that is used for data transfers between primary memory and a webcam. The memory transfers 15 frames where each frame is 1M byte in size and the buffer size is 1K byte. 1-How many data transfers will be required? 2-A transfer operation requires 2 interrupts. Start and stop. How many interrupts will occur for the data transfer? 3-What are the two commands that will be issued by the supervisor for each interrupt?OPERATING SYSTEMS Give two reasons why caches are useful.What problems do they solve?What problems do they cause? If a cache can be made as large as the device for which it is caching (for instance, a cache as large as a disk),why not make it that large and eliminate the device?