A) Specify the contents of CPU registers that can be effected when the following program is executed: MOV DX, A000H MOV SS, DX MOV SP, 01FBH MOV AX, 04EAH MOV BX, 8000H CMP AX, BX STI CLD PUSH F AND AH, FBH SAHF HLT

Q: Assume the following initial values of registers r1-r5: re= 0x0 r1= 0x0 r2= 0x0000000A r3=…

A: Please check the step 2 for solution

Q: a) What is the contents of AL, and CL registers after executing the following instruction sequence?…

A: Note : As per company guidelines, we can answer 1 question per post. Please repost other questions…

Q: 1. Solve the following problems: a) Given a 50 MHz FOSC, how long does it take the instruction goto…

A: We need to find time and number of instructions.

Q: Q1) Given a CPU time of 1 millisecond, a clock rate of 1 Ghz, and an instruction count of 10,000,…

A: Given, CPU time = 1ms Clock rate = 1Ghz Number of instructions = 10000

Q: Question 3: please solution with explain What answer appears in memory locations 1200 hex to 1203…

A: According to our guidelines we can solve first one: ================================== Answer 3:…

Q: Question 2: Answer each of the following 1) The memory locations 1000, 1001, and 1004 have data…

A: The question is to write the output of the given assembly level instruction.

Q: Question: Identify the problems in the following instructions and correct them by replacing them…

A: Answer:- i.) mov [05], [24] In this instruction given both memory locations so that's why memory to…

Q: Q1) If BX=1000, DS=0200, SS=0100, CS=0300 and AL=EDH, for the following instruction: MOV [BX] +…

A: Given Values are:- BX= 1000, DS= 0200, SS=0100, CS=0300, AL=EDH The instruction is MOV [BX]+1234H,…

Q: PUSH the contents of the B register to TMOD Copy the contents of external code memory address…

A: GIVEN: PUSH the contents of the B register to TMOD Copy the contents of external code memory…

Q: Assume that the registers have the following values (all in hex) and that CS=1000, DS=2000, SS=3000,…

A: Physical address: Actually, a physical address is also called as real address, or binary address. It…

Q: Consider the following fragments of Intel assembly language. What is the value of the eax register…

A: We need to find value of eax register for each code.

Q: 2. Study this program then answer the questions that follow: MOV DX, 1234 H MOV BX, 3099H MOV AL, BL…

A: The program is given 1) The arithmetic addition operation is performed but the output is in the BCD…

Q: 6) Fill in the requested register values that come on the right side for the following instruction…

A: Below is the solution

Q: Assume the following contents of registers and quadwords in memory: Location Value %rax Ox8 %rbx Ox1…

A: leaq s,d Here, “s” denotes source, “d” denotes destination. This instruction loads the address of…

Q: (c) The process of fetching the next instruction when the present instruction is being executed is…

A: There are two ways to boost a CPU's performance:1) Introduce quicker circuits into the hardware.2)…

Q: 3. Assume the following 64b register contents: x5 O×0000000OODEADFAD, x6 = 0×BADBEEF011223344 For…

A: Answer is given below .

Q: 2. Identify the type of addressing mode in the following instruction: i. MOVE.W $1500, D2 = ii.…

A: Given: We have to identify the type of addressing mode in the Following instructions.

Q: Question 2: Answer each of the following 1) The memory locations 1000, 1001, and 1004 have data…

A: Here in this question we have given some instructions in low level language.and based on this we…

Q: 3- Suppose that DS = 100H, SS = 300H, BP = 200H, and SI = 0100H, BX= 1500H . Determine the memory…

A: DATA Given:- DS=100H SS=300H SI=0100H BX=1500H Instruction : MOV DL,[BP+200] Operation : Real…

Q: (i) Identify the addressing mode used in each instruction in the following code segment, and give…

A: The way of specifying data to be operated by an instruction is known as addressing modes. This…

Q: Pinned below

A: Explanation:Instruction lw loads the value of var_x in the register $s0.Instruction lw loads the…

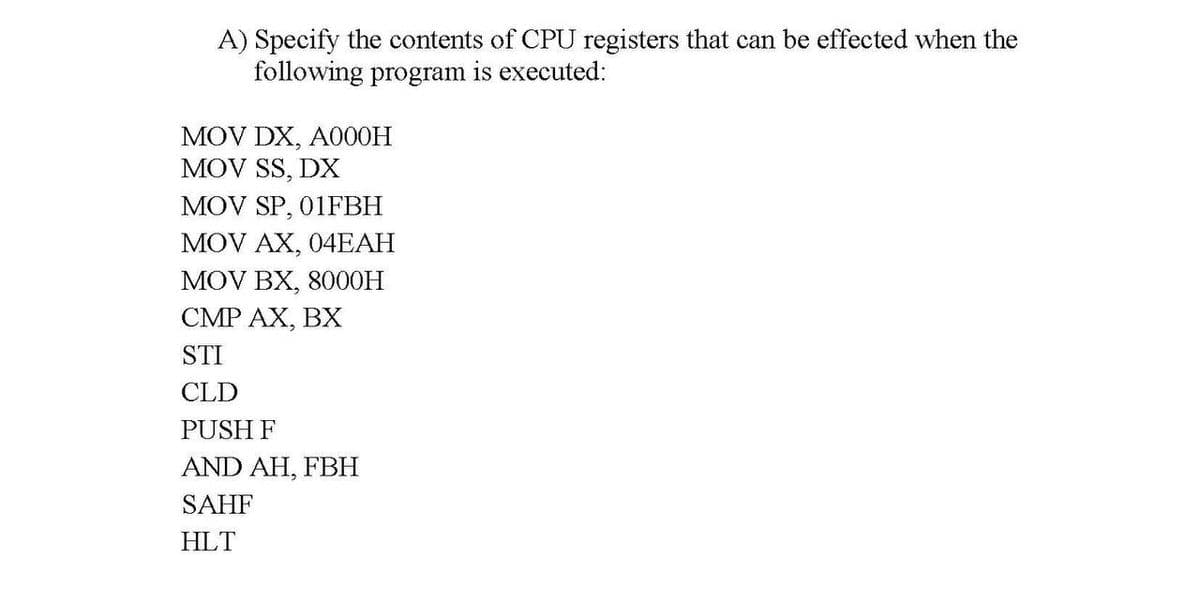

Q: A) Specify the contents of CPU registers that can be effected when the following program is…

A: Given program MOV DX,A000H MOV SS,DX MOV SP,01FBH MOV AX,04EAH MOV BX,8000H CMP AX,BX STI CLD PUSH F…

Q: 2-Suppose that DS = 100H, SS = 2000H, BP = 200H, and SI = 0100H, BX= 1500H. Determine the memory…

A: Solution Given , DS=100H SS=2000H BP=200H SI=0100H BX=1500H Instruction is : MOV AL , [ BX + 500 ]

Q: 11. a. Draw flowchart of IAS operation for the following pair of instructions located in address…

A: Answer: a) The flowchart of the instruction goes this way:

Q: a) Find the status of CY, AC and P flags after each of the following instructions. (C4) i. ii. MOV…

A:

Q: Assume we have the following instructions that need to be executed on the DLX computer: ADD R5, R8,…

A: According to the question we have non-pipeline DLX Architecture ADD R5, R8, R4 means it takes 4…

Q: 22. Suppose that DS = 0200H, BX = 0300H, and DI = accessed by each of the following instructions,…

A: The Answer is

Q: Assume the following register contents: $t0 = 0x01234567, $t1 = 0x56781234. Set back to these values…

A: The value of $t1, $t2, $t3, $t4 after the above instructions are given below

Q: Q2. A. Define the content of registers and/or Memory location after executing each instruction in a…

A: 1)Mov Ax, 33 H P. A= DS × 10H + [33H] = 200H × 10H +33H = 2000H +33H P. A…

Q: 6) Study the data transfer program of the figure below and answer the following questions: a. When…

A: Refer the problem figure from the text book. The MOV instruction copies the contents of the source…

Q: (ii) What is the content of register AX after executing the following instruction? mov AX, [0x208]…

A:

Q: Q:find the actual address for the following instruction assume X=38 and R index=DCE8 hex LOAD X(Ri),…

A: Solution:-

Q: 3. Assume that the following registers contain these Hex. values: AX= F000H, BX 3456H and DX E390H…

A: -AX register is of bits -0-15, where 0-7 are AL ,means lower bit address of address register A and…

Q: 1-a: The content of AR at timing T1 is . when an ISZ instruction fetched from .memory and executed…

A: Actually, AR is a Address Register.

Q: * H/W At a certain time, the simple computer registers contents the following data: PC = 1FFH, AR =…

A:

Q: Write ASL programs in EMU8086 to accomplish the following tasks. a) Evaluate (5 + 4) * 36. Your…

A: Assembly language: Assembly language is a low level programming language. It is used to tell…

Q: Q:find the actual address for the following instruction assume X=A6 and PC=8B79, LOAD X(PC), D…

A: Given: X = A6 PC = 8B79 LOAD X(PC), D Find the actual address.

Q: Explain utiat haprns PUSH Bx instruction executes. Make sure to show where BH and BL are stored…

A: Hey there, I am authorised to answer any one question at a time when there are multiple questions…

Q: 3. The following table shows the number of instructions for a program. ARITH STORE LOAD BRANCH TOTAL…

A: The Answer is in below Steps

Q: 2. What operation is performed by the instruction sequence that follows? MOV AH, [BX+SI] SAHF

A: MOV AH, [BX+SI] SAHF

Q: 1- Explain what operation is performed by each of the instruction that follow a. MOV AX,0110H b. MOV…

A: 1) MOV AX, 0110H It will move value stored in immediate operand in 0110H to AX 2)MOV D1,AX Data…

Q: 2- For the MIPS assembly instructions below, what is the corresponding C statement? Assume that the…

A: The answer is given below:-

Q: 2. Use the following data definitions for the following questions: myBytes BYTE 10h, 20h, 30h, 40h…

A: Step 1:- Given:- myBytes BYTE 10h,20h,30h,40h myWords WORD 8Ah,3Bh,72h,44h,66h

Q: 4 Assuming the following integers in memory: 3000 2000 1000 1000 100 10 And the following integers…

A: About leal instruction:

Q: 8. Analyze and state the contents of R2 and memory location 0x20000000 after the following program:…

A: LDR R2 ,=0x12F61234 ; R2 will point to memory location 0x12F61234 R2= 0x12F61234 MOV…

Q: 1) Write an instruction sequence to decrement the contents of data memory locations 0x10, 0x1 1, and…

A: As per our policy, "Since you have asked multiple questions, we will solve the first question for…

Q: 1. SP=F002H; after PUSH BX, what is the value of SP? _____________ (1 Mark) 2. BL=00, after…

A:

Q: iv) Using the following instruction format, a total of registers can be addressed 8 7 10 OP code…

A: 4) 4.10

Q: 2. (a) How many instruction bits are required to specify the following: (i) Two operand registers…

A: Here is the answer for finding the total bits in the instruction

Step by step

Solved in 2 steps

- Constants such as 250, 400, 5.5, and so on can be put into the source location of the Allen-Bradley MOV instruction instead of a memory address containing the value to be transferred. True \sFalseQuestion1: Multiple Choice: (please leave it to other tutors who can answer all my sub-question since this is my last question for this month) 2-The elements of the ISA for a particular type of CPU include a. addressing modes b. data types c. instructions d. a and b e. a, b and c Question 2: Perform the following logical operations and express your answers in hexadecimal notation. x3487 AND x7254 xABCD or x3234 xF098 XOR x3344I- Explain utiat haprns PUSH Bx instruction executes. Make sure to show where BH and BL are stored (assume that SP=OI OOh and SS=0200h) 2- Show the ending auress of each memory segments for the follow.ng segment register values: SS=ABCDw CS=EOOOh, DS=FOFOW cs=1234h 3- Sumx»se ECx-12345678h , EBx—876S4321h DS-1100tL Determine the contents of each address accessed by the following instructions: (a) MOV [EBx].ECx (b) MOV WORD PTRIEBx J, 1234b

- The following statements describe the basic CPU organization. Select all TRUE statements. Question 4 options: a The program counter (PC) holds the address of the next instruction to be fetched from Memory. b Buses serve as communication highways for passing information. c The instruction register holds each instruction fetched from memory. d The arithmetic logic unit (ALU) carries out arithmetic and logical operations, such as addition, comparison, Boolean AND/OR/NOT, etc.4 Memory and Addressing Modes The state of the CPU and memory is represented by this diagram. ey Wemory Address | Value Value |0 [0 |1(0]|0|0(1]1 a) Value of A after execution of LDA #50D? b) Value of A after execution of LDA #50F? ©) Value of ¥ after execution of LOY $0D? d) Value of Y after LDY $(000F), X? ) Value of Y after LDY ($0F), X2 please show workings!Analyze the flow chart below. QUESTIONS: 6. Determine - calculate the delay generated by [DE] and the value of "F" after the instruction [A]<-[A]v[E] is executed the first and the 10th time. 7. Determine - discuss the contents of the displays. 8. Estimate - Calculate the shortest execution time of the program in terms of instructions, cycles, and seconds. 9. Repeat Part 8 for the longest execution time. 10. Are the two PUSHH instructions required? Discuss.[}][|

- The purpose of adding cache between main memory and CPU is ( ).A. Solve the speed matching problem between CPU and main memory. Increase the capacity of the main memory.C. Enlarging the number of general-purpose registers in the CPU D. Both increasing the main memory capacity and increasing the number of general-purpose CPU registersConsider the following program in MARIE assembly language. a) Complete the table detailingthe RTN for next 2 instructions only that will be executed including the content of registers PC,IR, MAR, MBR and AC in hexadecimal. Note the first instruction LOAD X is already filled. Notealso that SKIPCOND instruction has no operands, therefore you can complete Fetch, decode andexecute cycles only. b) Explain in one statement the task performed by this program?20. CPU as two modes privileged and non-privileged. In order to change the mode from privileged to non-privileged a. A hardware interrupt is needed b. A software interrupt is needed c. Either a or b d. A non-privileged instruction (which does not generate an interrupt)is needed

- Design a CPU System that combines and connect memory system, ALU, registers and controlunit. The CPU MUST use a 16-bit instruction format where 4-bit for Opcode, 6-bit forOperand 1 and 6-bit for Operand 2 as shown below: The CPU should be able to perform the complete instruction cycle (fetch instruction (FI),decode instruction (DI), calculate operands (CO), fetch operands (FO), execute the instruction(EI), and write operand (WO). To verify the functionality of the CPU system, the studentshave to create test benches to demonstrate that the CPU is able to perform at least thecomputations as shown below: You are asked to draw the Flow Chart based on the information given above. The Flow Chart drawn must be accompanied by a brief description of it.Design a CPU System that combines and connect memory system, ALU, registers and controlunit. The CPU MUST use a 16-bit instruction format where 4-bit for Opcode, 6-bit forOperand 1 and 6-bit for Operand 2 as shown below: The CPU should be able to perform the complete instruction cycle (fetch instruction (FI),decode instruction (DI), calculate operands (CO), fetch operands (FO), execute the instruction(EI), and write operand (WO). To verify the functionality of the CPU system, the studentshave to create test benches to demonstrate that the CPU is able to perform at least thecomputations as shown below:11.a) Discuss the sequencing of control signals for the following instructions. i) Load R1,10(R2) ii) Add R1, R2 b) Compare and contrast memory mapped IO over programmed IO. need complete solution of a and b,,,thank u