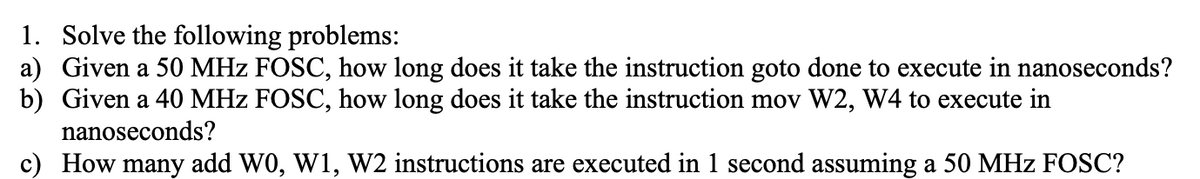

1. Solve the following problems: a) Given a 50 MHz FOSC, how long does it take the instruction goto done to execute in nanoseconds? b) Given a 40 MHz FOSC, how long does it take the instruction mov W2, W4 to execute in nanoseconds? c) How many add W0, W1, W2 instructions are executed in 1 second assuming a 50 MHz FOSC?

Q: Suppose that a task on the ARM computer runs 256M instructions during its execution. The total time…

A: Shortest Possible Stage time = 10ns Total execution time = 16M instructions * 1 cycle/inst * 10ns =…

Q: Problem 3: If we assume a CPU can process 100000 Instruction/sec. Compute the CPU utilization in the…

A: CPU Utilization is the percentage of instructions currently executing divided by total number of…

Q: a- Find the total execution time for the program on 1,2,4, and 8 processors, and show the relative…

A:

Q: Question 3: please solution with explain What answer appears in memory locations 1200 hex to 1203…

A: According to our guidelines we can solve first one: ================================== Answer 3:…

Q: 2- Draw memory and microprocessor contents before and after execution the following instruction: MOV…

A: Given: We are given a microprocessor instruction below: Goal: We have to find the contents of…

Q: Assume a pipelined processor with five pipeline stages where each stage takes one clock cycle.…

A: Answer: I have given answer in the brief explanation.

Q: b) Given the following register and memory values, what values do the following ARM instructions…

A: Value of R0 register is given below after each given ARM instructions

Q: What is the result of executing the following instruction sequences? MOV DX,00H MOVAX,245 MOV CX,100…

A: According to the information given:- we have to execute the instruction sequence

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 x 106 INT instructions,…

A: The answer is...

Q: Suppose on a non-pipelined single-processor machine, you have the following breakdown: alu…

A: (a)Non-pipelined single-processor machineAverage CPI = (0.25*2 + 0.3*10 + 0.15*4 + 0.3*1.5) = 4.55

Q: In this exercise, we examine how pipelining affects the clock cycle time of the processor. Problems…

A: Below is the answer to above question. I hope this will be helpful for you.

Q: Question 2 (8) i) Processor having Clock cycle of 0.25ns will have clock rate of a) 2GHZ b) 3GHZ c)…

A: “Since you have posted a question with multiple sub-parts, we will solve the first three subparts…

Q: Consider the following duration for each stage: IF - 286 ID = 196 EX (addition) 383 EX (subtraction)…

A: According to the given information:- We have to find the stage pipeline datapath and its execution…

Q: 3-Assume a program requires the execution of 60*10^6 FP instructions, 120 × 10^6 INT instructions,…

A: Solution is given below:-

Q: Answer the following questions. A. A computer system has a main memory access time as 60ns. you as a…

A: ANSWER:-

Q: 5. Consider three different processors P1, P2, and P3 executing the same instruction set. P1 has a 3…

A: Given:

Q: 3- Suppose that DS = 100H, SS = 300H, BP = 200H, and SI = 0100H, BX= 1500H . Determine the memory…

A: DATA Given:- DS=100H SS=300H SI=0100H BX=1500H Instruction : MOV DL,[BP+200] Operation : Real…

Q: Consider the following instruction, discussed in Example 8.6: MAC *AR2+, *AR3+, A Suppose the…

A: Solution:-- 1)The given question has required for the solution which is related with the…

Q: Assume a hypothetical GPU with the following characteristics: • Clock rate 1 GHz • 32 simultaneous…

A: As Given by question Clock rate=1 GHz SIMD=8 cores, each containing 32 single-precision…

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 × 106 INT instructions,…

A: the answer is....

Q: 2-Suppose that DS = 100H, SS = 2000H, BP = 200H, and SI = 0100H, BX= 1500H. Determine the memory…

A: Solution Given , DS=100H SS=2000H BP=200H SI=0100H BX=1500H Instruction is : MOV AL , [ BX + 500 ]

Q: Consider the data path below for a single cycle 32-bits MIPS processor Assume that we are executing…

A: the option c is correct

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 × 106 INT instructions,…

A: The answer is...

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 × 106 INT instructions,…

A: the answer is...

Q: Question 4 (a) Consider the memory locations shown in Table Q4 (a), explain the architecture of a…

A:

Q: Address Word Ox00000015 ? Ox00000014 ? Ox00000013 ? Ox00000012 ? Ox00000011 )x00000010

A: Here is the solution to the above problem: -

Q: Q3 Assume the following latencies for a single-issue processor. Instruction Producing Result FP…

A: Answer: I have given answered in the handwritten format in brief explanation

Q: A certain microprocessor requires either 2, 4, 8, 12, or 16 machine cycles to perform various…

A: Distribution of the frequency: CPU speed is considered as the key deciding factor for finding the…

Q: Assume a program requires the execution of 50 × 106 FP instructions, 110 × 106 INT instructions, 80…

A:

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 × 106 INT instructions,…

A: The answer is...

Q: Memory location2017H through 2020H contain, respectively, OAH, 9BH, C2H, and A8H. What does AX or AL…

A: Assembly language: Assembly language is used to tell directly the computer what to do. The computer…

Q: Assume forwarding and stall mechanisms have been designed, show the timing of this instruction…

A: 5 Stages Pipelined CPU: Fetch, Decode, Execute, Memory, Write There are 11cycles followed to fetch,…

Q: Assume that the Intel 8086 registers AL, BL, CL, and DL have the following values Gn Hexadecimal)…

A: Question 1) XCHG BL, DL will exchange the values of BL with DL , thus BL= AB DL = CD. Question 2)…

Q: Assume a program requires the execution of 75 ×106 FP instructions, 112 ×106 INT instructions, 88…

A: The answer is ...

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 x 106 INT instructions,…

A: The answer is

Q: d) Consider I have the following instructions Id addi x11, x12, 5 x12, 16(x11) add x13, x11, x12…

A: In above code we can see that each instruction consist of 3-stage . however, some instruction depend…

Q: Q2/ Assuming that the registers have the following values (all in hex) and that CS=1000, DS=2000,…

A: 1.Instruction Address: In the execution of a sequence of instructions in a computer program, a…

Q: Assume a program requires the execution of 75 x106 FP instructions, 112 ×106 INT instructions, 88…

A: The Time taken for n number of instructions which are of normal type= n*CPI/(clock rate)

Q: Question 8: Consider a 5-stage instruction execution in which, Instruction fetch = ALU operation =…

A: *As per the company norms and guidelines we are providing one question answer only please repost…

Q: 3-Assume a program requires the execution of 50 × 106 FP instructions, 110 × 106 INT instructions,…

A: The answer is...

Q: 1.14 Assume a program requires the execution of 50 x 106 FP instructions, 110 x 106 INT…

A: The answer is...

Q: Consider three different processors P1, P2, and P3 executing the same instruction set. P1 has a 5.1…

A: According to the information given:- We have 3 different processors and follow the instruction.

Q: Assume a program requires the execution of 50 x 106 FP instructions, 110 x 106 INT instructions, 80…

A: The answer is....

Q: Memory locations 00390H through 00393H contain, respectively, 9A, 76, 65, and 1F. What does AX…

A: Memory location 00393H contain ,respectively,9A ,76,65 and 1F.what does Ax contain after each…

Q: Given the following latencies-- I-Mem: 200ps, Add: 70ps, Mux: 20ps, ALU: 90ps, Regs: 90ps, D-Mem:…

A: GIVEN: I-Mem Add Mux ALU Regs D-Mem Sign-Extend Shift-Left-2 200ps 70ps 20ps 90ps 90ps 250ps…

Q: A certain microprocessor requires either 2, 4, 8, 12, or 16 machine cycles to perform various…

A: A machine cycle refers to the process that a computer's processor executes whenever it receives a…

Q: Consider three different processors P1, P2, and P3 executing the same instruction set. P1 has a 3GHz…

A: Given terms are clock rate and CPI of processors P1, P2 and P3 Processor P1 , clock rate = 3GHz ,…

Q: 2. We examine how pipelining affects the clock cycle time of the processor. Problems in this…

A: solution for the above question is solved in step 2:-

Q: Answer the following questions. Consider the following program and assume that the Initial content…

A: consider the given Instructions and Answer the following questions i. Write the timing of…

Q: Assume a program requires the execution of 50 × 106 FP instructions, 110 × 106 INT instructions, 80…

A:

Step by step

Solved in 2 steps

- Question: Suppose a program of 600 instructions runs on a 2 GHz processor. The frequency of instructions and the clock cycle counts per instruction are given as follows. What is the average CPI of this instruction mix? Operation Frequency Clock Cycles ALU operations 55% 1 Loads/Stores 30% 2 Branches 15% 3 Question: Continue from the previous question. What is the CPU time of the program in nanoseconds? Question: Suppose a processor P has a 2.5 GHz clock rate and a CPI of 1.5. If the processor executes a program in 3 microseconds, find the number of instructions in the program.Assume a program requires the execution of 75 ×106 FP instructions, 112 ×106INT instructions, 88 ×106 L/S instructions, and 12 × 106 branch instructions.The CPI for each type of instruction is 1, 3, 4, and 2, respectively. Assume thatthe processor has a 2 GHz clock rate.a) By how much must we improve the CPI of FP instructions if we wantthe program to run two times faster?b) By how much must we improve the CPI of L/S instructions if we wantthe program to run two times faster?c) By how much is the execution time of the program improved if theCPI of INT and FP instructions is reduced by 40% and the CPI of L/Sand Branch is reduced by 30%?Consider the following store instruction: SW R1, 0x000F(R0). Assume that the registers R0 and R1 are initialized with 0x00000001 and 0x53A78BC Frespectively. A section of the MIPS byte addressable data memory is shown. Give the memory word of the following memory locations after the SW operation: (a). 0x00000015. (b). 0x00000014. (c). 0x00000013. (d) 0x00000012.(e). 0x00000011. (f). 0x00000010.

- Assume that a program requires the execution of 125x106 FP (floating point) instructions, 130x106 INT (integer) instructions, 150x106 L/S (load/store) instructions, and 110x106 branching instructions. These instructions have CPIs of 1, 1, 8 and 4, respectively. Assume that the processor has a 5 GHz clock rate. a. Is it possible to run the program twice as fast if we improve the CPI of just the L/S instructions? If so, by how much? Show your calculations. b. What is the Speedup in the execution time of the entire program if the CPI of INT and FP instructions is reduced by 40% and that of L/S and branching instructions is reduced by 50%?Assume that every 18 months, the number of CPU cores available is doubled. How much extra off-chip memory bandwidth will be required for a CPU introduced in three years to retain the same level of per-core performance?ANSWER THE QUSTIONS THAT IS WRITEN OR ON THE PICTURE PLEASE Question 6: Suppose in a program there are 120 instructions, and 6 stages are required for each instruction to be processed. Time required in each stage is equivalent to 1 ps. Calculate the speedup of pipeline parallel processing. Question 7: Suppose in a program there are 300 instructions, and 6 stages are required for each instruction to be processed. Time required in each stage is equivalent to 1 ps. Calculate the efficiency of pipeline parallel processing. Question 8: Consider a 5-stage instruction execution in which, Instruction fetch = ALU operation = Data memory access = 250 ps; and Register read = Register write = 200 ps. Find out the speedup factor for pipelined execution.

- Consider three different processors P1, P2, and P3 executing the same instructionset. P1 has a 3GHz clock rate and a CPI of 1.5. P2 has a 2.5GHz clock rate and a CPI of 1.0, P3has a 4GHz and a CPI of 2.5.a) Which processor has the highest performance expressed in instructions per second?b) If the processors each execute a program in 5 seconds, find the number of cycles and thenumber of instructions.c) We are trying to reduce the execution time by 20% but this leads to an increase of 15% inthe CPI. What clock rate should we have to get this time reduction?Q: Consider three different processors P1, P2, and P3 that support the same instruction set. P1 has a 3 GHz clock rate and a CPI of 1.5. P2 has a 2.5 GHz clock rate and a CPI of 1.0. P3 has a 4.0 GHz clock rate and has a CPI of 2.2. (a) Which processor has the highest performance expressed in instructions per second? Show your calculations. (b) If the processors each execute a program in 10 seconds, find the number of cycles and the number of instructions for each processor. (c) We are trying to reduce the execution time by 30% (i.e., execution time is reduced from 10 seconds to 7 seconds). However, this leads to an increase of 20% in the CPI. For each processor, what clock rate should we have to get this time reduction? (Show the calculations you did to answer this question.)Assume that every 18 months, the number of cores available on a new generation of CPUs is doubled. How much extra off-chip memory bandwidth will be required in three years to maintain the current level of per-core performance?

- On a uniprocessor, portion A of program P consumes 24 seconds, while portion B consumes 822 seconds. On a parallel computer, moderately serial portion A speeds up 4 times, while perfectly parallel portion B speeds up by the number of processors. 1- What is the speedup of program P on 1,024 processors? _______ times 2- How many processors are required to achieve at least half the theoretical maximum possible speedup on P?Assume for arithmetic, load/store, and branch instructions, a processor has CPIs for 1, 12, and 5respectively. Also assume that on a single processor a program requires the execution of 2.56*10^9arithmetic instructions, 1.28*10^9 load/store instructions, and 256 million branch instructions. Assumethat each processor has a 2GHz clock frequency. Assume that, as the program is parallelized to run overmultiple cores, the number of arithmetic and load/store instruction per processor is divided by 0.7xp(where p is the number of processors) but the number of branch instructions per processor remains thesame. a- Find the total execution time for the program on 1,2,4, and 8 processors, and show the relativespeedup of the 2,4, and 8 processor result relative to single processor result. b- If the CPI of the arithmetic instruction was doubled, what would be the impact be on theexecution time of the program on 1,2,4, and 8 processors? c- To what should the CPI of load/store instructions be…In this problem, you will explore processor frequency in the context of the speed of light.Suppose you have overclocked a processor to 8,722.78MHz. This processor can execute one instruction per cycle. Further let us suppose that the system is accessing a magnetic disk (HD) with an access time of 11ms. 1. Suppose that you are designing the machine architecture and want to guarantee the CPU can obtain data from memory within 4 CPU cycles. Given that the address has to travel from the CPU to the memory unit (MMU) and that the data has to travel from memory to the CPU, what is the maximum distance between CPU and the MMU if the signal on the memory bus propagates at 75% of the speed of light?