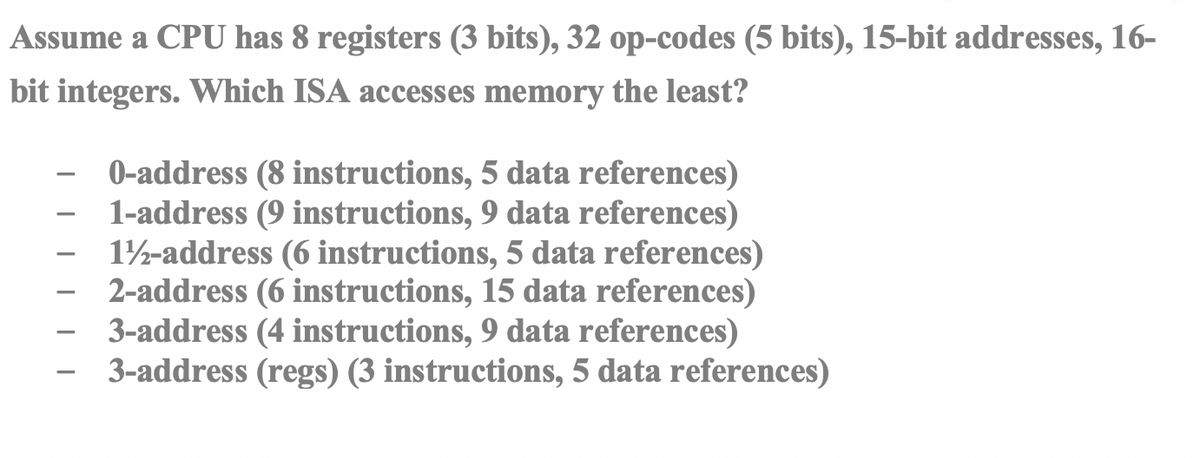

Assume a CPU has 8 registers (3 bits), 32 op-codes (5 bits), 15-bit addresses, 16- bit integers. Which ISA accesses memory the least? 0-address (8 instructions, 5 data references) 1-address (9 instructions, 9 data references) 12-address (6 instructions, 5 data references) 2-address (6 instructions, 15 data references) 3-address (4 instructions, 9 data references) 3-address (regs) (3 instructions, 5 data references) - - -

Q: MIPS ISA has registers of 32-bits which are employed to create a 64-bit base address which is…

A: The Lord word and Store Word instruction format does not contain a random pair of source registers.…

Q: a processor using 32-bit memory addresses and a fully associative cache memory that stores 32 bits…

A: The associative cache definition is a. balance between fully coherent and direct mapped caching. In…

Q: Given a memory of 2048 bytes consisting of several 64 x 8 RAM chips, and assuming byte-addressable…

A: A correct option is an option (e).

Q: Consider a hypothetical microprocessor generating a 16-bit address (for example, as- sume that the…

A: a) Hypothetical microprocessor generating 16-bit address. The program counter and address register…

Q: The register content for an Intel 8086 microprocessor is as follows: CS = 1000H, DS = 2000H, SS =…

A: Given:

Q: e system shown below, answer following questions CLK 3.3GHZ DATA BUS (16 bits) CPU ADDRESS BUS (23…

A: 1). 2address bus width Equals total addressable memory * The size of the data bus. For example, a…

Q: Suppose a computer has 32-bit instructions. The instruction set consists of 120 different…

A: There are 120 instructions. So we need a minimum of 7 bits to encode them. There are 32 registers.…

Q: a) How many bits does a processor need internally to address a 32M x 32 memory if the memory is word…

A:

Q: 1. A central processing unit (CPU) has the following hardware components: Program Counter (PC) •…

A: All registered CPU - connected to two internal buses Memory Bus

Q: Desired to have a memory of = 64K bytes. No of bits in address bus to address memory location = 13…

A: Desired to have a memory of = 64K bytes.No of bits in address bus to address memory location = 13…

Q: a) How many bits does a processor need internally to address a 32M x 32 memory if the memory is word…

A: As per Bartleby guideline we can only provide only 3 subparts.

Q: Use the register and memory values in the tables below for the next questions. Assume a 32-bit…

A: a) add $t3, $t2, $t1 implies adding the contents of register t1 to the contents of register t2 and…

Q: 4. Memory and Addressing Modes The state of the CPU and memory is represented by this diagram.…

A: EXPLANATION Below is the answer for the given question. Hope you understand it well. If you have any…

Q: [A] Suppose that a 16M x 32 main memory is built using 512K x 16 RAM chips and that the memory is…

A: a. To find out how many RAM chips are necessary, divide the size of memory with the chip size as…

Q: 1- Memory locations can be addressed by a microprocessor with 14 address lines? 2- Chips are…

A: 8086 System 8086 Microprocessor is an advanced version of the before version of 8086 which is teh…

Q: Consider a hypothetical 32-bit microprocessor having 32-bit instructions composed of two fields. The…

A:

Q: If the CPU accesses the recently accesse memory location again, it is called Answer in two words…

A: Given: In the given question we have to answer the following:

Q: Consider a computer with cache, DRAM, HDD memory hierarchy. The hit rate of cache is 90% and DRAM is…

A: Given, Hit rate of cache = 90 % This implies hit ratio of cache = h1 = 0.9 Hit rate of DRAM = 95 %…

Q: Sec 2 - Computer Org: MIPS, ARM, x86 A CPU core contains which blocks: O Execution Unit + L1 caches…

A: This question comes from Computer Organization/Architecture which is a paper of Computer Science.…

Q: Q1/ Explain with details the segments memory of microprocessor 8086 at below action: 1- Fetch and…

A: Bus: A bus is a common group of wires that interconnect components in a computer system. The buses…

Q: a. How many bits would a memory address have to have to make every address referenceable? z12928 1G…

A: a. How many bits would a memory address have to have to make every address referenceable? b. How…

Q: Suppose that A 8051 family CPU with 8K bytes on-chip ROM, please give the ROM memory address (6’).…

A: Answer The location of on-chip ROM is from 0000H to 1FFFH.The underlying location area is 0000H and…

Q: A microprocessor has a 32-bit address line. The size of the memory contents of each address is 8…

A: Check further steps for the answer :

Q: Instructions Space MAR ALU MBR AC BUS PC Control Data Space Cache A simple processor shown in the…

A: subtraction, addition and multiplication operations are given below:- by bartleby guidelines i am…

Q: A computer employs RAM chips of 128 x 8 and ROM chips of 512 x 8. The computer system needs 1K bytes…

A: Number of RAM and ROM chips required by computer system is calculated as mentioned below .

Q: Q 1. Answer the following short questions. Support your answers with diagram, where needed: How…

A: Programs are the set of lines of code that is used to provide instructions to the computer. The…

Q: microprocessors are to be interfaced to a system bus. The following details are given: All…

A: The answer given as below:

Q: Question 35 A processor running a program makes 100 accesses to memory addresses. 80% are to L1…

A: A processor running a program makes 100 accesses to memory addresses.80% are to L1 only,10% are to…

Q: CPU Main Memory Instructions Space MAR ALU MBR АС BUS PC Control Data Space Cache Explain in your…

A: Here it is the architecture of the simple processor, it having the two main blocks those are CPU and…

Q: A computer has a 256K word addressable memory Module with 16 bits per wor instruction set consists…

A: Dear Student, Given that size of main memory = 256K bits = 256*1024 bits, Now bits in the main…

Q: Q.In a computer instruction format, the instruction length is 11 bits and the size of an address…

A: Given information: Instruction length = 11 bits = 211 = 2048 bits Address register size = 4 bits

Q: Assume a CPU has 8 registers (3 bits), 32 op-codes (5 bits), 15-bit addresses, 16- bit integers.…

A: CPU has 8 registers (3 bits), 32 op-codes (5 bits), 15-bit addresses, 16-bit integers. Which ISA…

Q: iv) Consider the following two diagrams. Left one for memory management unit and right one for the…

A: providing the answer below

Q: Memory - reference intruction AND ADD LDA STA DT. D,T. D;T. DT. DRMAR) DR-MIMAR) DR-M(AR) MIAR)-AC…

A: Since you are asking multiple questions, we are doing first question for you. If you want solution…

Q: Assume a CPU has 8 registers (3 bits), 32 op-codes (5 bits), 15-bit addresses, 16-bit integers.…

A: ISA: ISA is the part of the processor that is noticeable to the programmer or compiler author. The…

Q: CPU Main Memory Instructions Space MAR ALU MBR AC BUS PC Control Data Space Cache A simple processor…

A: As per Bartleby, Since you have posted a question with multiple sub-parts, we will solve the first…

Q: Consider a hypothetical microprocessor generating a 16-bit address (for example, as sume that the…

A: It is defined as the central unit of a computer system that performs arithmetic and logic…

Q: CPU Main Memory Instructions Space MAR ALU MBR AC BUS PC Control Data Space Cache A simple processor…

A: Given is in a reaction between Fe+3 and NCS-, Kc = 620.4 Volume of Fe+3 = 10 mL molarity of Fe+3 =…

Q: For this question, use the register and memory values in the tables below. Assume a 32-bit machine.…

A:

Q: CPU Main Memory Instructions Space MAR ALU MBR AC BUS PC Control Data Space Cache plain in your own…

A: It is defined as an electronic device that manipulates information, or data. It has the ability to…

Q: What is the number of required bits for the machine instruction set, knowing that the processor can…

A: 64-bit virtual memory, for example, support only 48 bits of virtual address, with the remaining 16…

Q: CPU Main Memory Instructions Space MAR ALU MBR AC BUS PC Control Data Space Cache A simple processor…

A: by bartleby guidelines, i am able to do only 3 sub parts. 3 operations are solved below:-

Q: The code segment has a value of 0ACFH with 0123H in the instruction pointer what physical address…

A: b)04E13H

Q: CPU Main Memory Instructions Space MAR ALU MBR AC BUS PC Control Data Space Cache A simple processor…

A: by bartleby guidelines i am able to do only 3 sub parts of a question. all the 3 operations are…

Q: In a computer instruction format, the instruction length is 11 bits and the size of an address field…

A: Given:Instruction length = 11 bits = 211 = 2048 bitsAddress register size = 4 bits

Q: A Digital computer has a memory unit with 32 bits per word (memory element). The instruction set…

A: Word size(memory element) = 32 bits Number of operations = 260 So, to represent 260 operation the…

Q: 1) How many address lines in the 8086 microprocessor? 2) How many data lines in the 8086…

A:

Q: .in a code space of 8Kbytes mapping from address 0X1000. What is the last address available to store…

A: Over here given a code section of 8k bytes. Means total size is 8192.

Q: We want to build a word organized main memory of 8 GB for a 32-bit CPU architecture composed of word…

A: Solution:: Let's see the direct answer for the above question first then will see the basic part…

Trending now

This is a popular solution!

Step by step

Solved in 3 steps

- How does pipelining improve CPU efficiency? What’s the potential effect on pipelining’s efficiency when executing a conditional BRANCH instruction? What techniques can be used to make pipelining more efficient when executing conditional BRANCH instructions?Most Intel CPUs use the __________, in which each memory address is represented by two integers.Processor R is a 64-bit RISC processor with a 2 GHz clock rate. The average instruction requires one cycle to complete, assuming zero wait state memory accesses. Processor C is a CISC processor with a 1.8 GHz clock rate. The average simple instruction requires one cycle to complete, assuming zero wait state memory accesses. The average complex instruction requires two cycles to complete, assuming zero wait state memory accesses. Processor R can’t directly implement the complex processing instructions of Processor C. Executing an equivalent set of simple instructions requires an average of three cycles to complete, assuming zero wait state memory accesses. Program S contains nothing but simple instructions. Program C executes 70% simple instructions and 30% complex instructions. Which processor will execute program S more quickly? Which processor will execute program C more quickly? At what percentage of complex instructions will the performance of the two processors be equal?

- Consider a word-addressable computer with 32 bits per word. The instruction set consists of 30 different All instructions have an operation code field, a mode field to specify one of 7 possible addressing modes, a register address field to specify one of 60 available registers, and a memory address field. Each instruction is stored in one word of memory. What is the maximum allowable size for memory? Use KB, MB, or GB as a unit.Suppose that A 8051 family CPU with 8K bytes on-chip ROM, please give the ROM memory address (6’). Also please give the initial address location and the maximum address location of 8051 family CPU (6’).1. Assume the memory uses big endian addressing, find the byte stored in 0x20000001 if the address of the memory 0x20000000 contains the value 0x89346710. 2. Assume the memory uses little endian addressing, find the value of r0 after the instruction LDRSB r0, [#0x20000000] if the address of the memory 0x20000000 contains the value 0x893467B0.

- A read/write type memory will be designed for a microprocessor with 16 bit address bus.. Memory chips will be 1K type. Write down bitwise memory addresses for each chip and determine address bits for S0=, S1= and I0=, I1=, I2= and I3= for which memory chip. Draw the full system architecture (CPU-Memory-Decoder-Buses). Write your name on, Student Id and put signature on the paper and take full picture If your last digit of your Student ID is 0, 2,5 then memory range $1C00H-27FFH If your last digit of your Student ID is 1, 3, 6, 9 then memory range $2400H-33FFH If your last digit of your Student ID is 4, 7 , 8 then memory range $3800H-43FFH LAST DİGİT = 9Main memory of the basic computer has been shown in the figure below, each instruction and memory variables are represented with the respective physical address (in red and bold font) of each location. PC has value of 1028h and addressing mode is direct. Main Memory Address Content 1028h LDA 2011h; 1029h BUN 102Bh; 102Ah ADD 2012h; 102Bh AND 2012h; : : 2011h 0; 2012h 1; You are required answer following questions. How these instructions will be executed according to instruction execution cycle with respect to the timing signals (T0, T1, T2..)? (10) What will be the value of these registers (PC, AR, DR, IR and AC) with respect to timing signals during the execution of each instruction? (10) What will the final outcome of the after the execution of instruction at physical address 102Bh? (5)Consider a hypothetical microprocessor having 32-bit instructions composed of two fields: the first Byte contains the opcode and the remainder the immediate operand or operand address. What is the maximum directly accessible memory capacity (in Bytes)? Discuss the impact on the system speed if the microprocessor bus has: a 32-bit local address bus and a 16-bit local data bus a 16-bit local address bus and a 16-bit local data bus

- Suppose a machine has word length of 32 bits, and the CPU has 32 registers of 32 bits. Design an instruction system with 64 operations. (1) If it uses register addressing mode and the direct addressing mode in the instruction, what is the maximum main memory space that can be addressed? (2) What are the differences between the based index addressing and index addressing? (3) Introduce at least three of other addressing methods that can be used.Suppose that a 64 Mega x 16 bits main memory is built using 16M x 8 bits chips of RAM and memory is word addressable. a. How many RAM chips are necessary? ______ b. How many RAM chips are needed for each memory word? _______ c. How many address bits are needed for each RAM chip? _______ d. How many address bits are needed for all memory? _______Q 1. Answer the following short questions. Support your answers with diagram, where needed: How the LIFO memory differs to FIFO Memory. Which type of addressing mode is used by the Instruction: ADD [BX+2], AX? What is the equivalent of a Binary number: 00110100011012 in octal and hexa-decimal. How much memory space is addressable (in bytes) by a microprocessor, if it uses 36 address lines? If Base address = A000H, Physical address = A0345H, then the offset add = ___________? Why address bus is unidirectional and data bus is bidirectional in 8086?