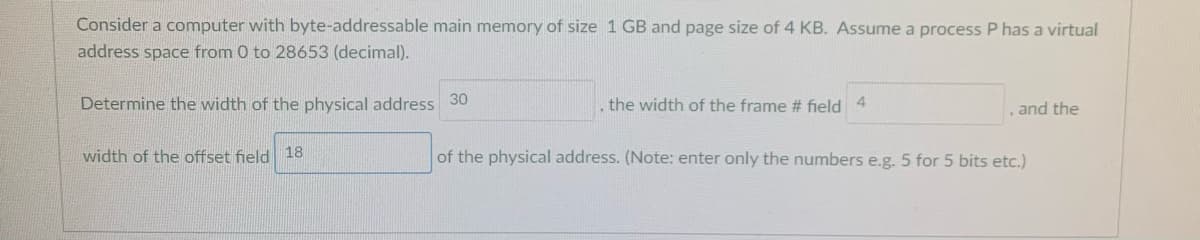

Consider a computer with byte-addressable main memory of size 1 GB and page size of 4 KB. Assume a process P has a virtual address space from 0 to 28653 (decimal). Determine the width of the physical address 30 , the width of the frame # field 4 , and the width of the offset field 18 of the physical address. (Note: enter only the numbers e.g. 5 for 5 bits etc.)

Q: Suppose a computer using direct-mapped cache has 232 bytes of byte-addressable main memory and a…

A: Given Information is as follow: Size of the main memory = 2^32 bytes. Size of cache = 1024 bytes…

Q: Suppose the page table for the process currently executing on the processor looks like the…

A: The virtual address is a virtual, logical address, there is no physical existence of this address in…

Q: Given a 32-bit virtual address space featuring a 10-10-12 split and a 4-byte PTE size, suppose a…

A: The Answer is

Q: A computer with a 32-bit address uses a two-level page table. Virtual addresses are split into a…

A: The ask is to calculate the page size and numbr of pages in the address space for a computer with a…

Q: Consider an operating system that uses 48-bit virtual addresses and 16KB pages. The system uses a…

A: Consider an operating system that uses 48-bit virtual addresses and 16KB pages. The system uses a…

Q: Suppose a processor has access to three levels of memory. Level 1 has an access time of 9…

A: Given Level 1 contains a subset of the bytes contained inlevel 2, and level 2 contains a subset of…

Q: Consider an operating system that uses Segmentation. Given an address [S,D], where S is the segment…

A: given an operating system that uses Segmentation. Given an address [S,D], where S is the segment and…

Q: Consider a system with 256Mbytes of main memory with page size of 4Kbytes. It has a logical address…

A: Answer: Given Main Memory 256Mbytes Page Size =4Kbytes and logical address=26 bits

Q: Consider a byte-addressable computer with 32-bit addresses, a cache capable of storing a total of…

A: Answer to the above question is in step2.

Q: Consider a logical address space of eight pages of 1024 words ach, mapped on to a physical memory of…

A: ANSWER:-

Q: Let us consider a memory that includes two instructions. First instruction is located at memory…

A: Given

Q: Suppose a computer using direct mapped cache has 4MB of byte-addressable main memory, and a cache of…

A: A) Total number of blocks in main memory = 2^22/2^4 = 2^18 B) Size of offset field =log(block size)…

Q: Suppose the page table for the process currently executing on the processor looks like the…

A:

Q: Consider a virtual memory system providing 32 pages for each user program; the size of each page is…

A:

Q: Consider a memory system with a 6-bit address space with a direct-mapped cache with two set bits and…

A: The memory address space is 6 bit and the cache is direct-mapped. We have to determine the offset…

Q: Consider a system with N bytes of physical RAM, and M bytes of virtual address and frames are K…

A: Here the virtual memory size = M bytes And page size is K bytes. The virtual address is divided…

Q: 9. Consider a system that uses 32-bit addresses and page table structures as discussed in class. If…

A: 32 bits= 2^5 256 pages= 2^8

Q: Consider a system with 256Mbytes of main memory with page ize of 4Kbytes. It has a logical address…

A: Here in this question we have given main memory size= 256MB. Page size = 4KB Logical address space=…

Q: Suppose the page table for the process currently executing on the processor looks like the…

A: (a) Split the binary address into a VPN and also an offset. Use VPN binary address as an index into…

Q: Consider a system with a 7-bit virtual address space,32-byte pages and 512-byte physical memory. The…

A: In this question, we are given virtual address and physical address with page size. Virtual address…

Q: Suppose a byte-addressable computer using set associative cache has 216 bytes of main memory and a…

A: Answer 1. 16 bits in an address cache contain 2^5 block. but each set must have 2 blocks so we have…

Q: Suppose a byte-addressable memory with 4 frames of size 16 bytes each and a paged virtual memory…

A: In this, we are asked about the TLB hit and physical address corresponding to the given virtual…

Q: Consider a computer with byte-addressable main memory of size 8 GB and page size of 1 KB. Assume a…

A: Byte addressable memory upholds getting to information in units that are smaller than the transport.…

Q: A computer has 32-bit virtual addresses and the page size is 2^9 KB. Suppose the text, data, and…

A: Here the virtual address size is 32 bits. Page size is 29 Bytes. Two level page table.

Q: Let us consider a memory that includes two instructions. First instruction is located at memory…

A: Given

Q: Consider the main memory size of 128 kB, Cache sıze of 16 kB, Block sıze of 256 B with Byte…

A: ----------------------------------------------- | Tag | Set Number | Block…

Q: Given a 32-bit virtual address space featuring a 10-10-12 split and a 4-byte PTE size, suppose a…

A: The memory is split as 10 - 10 - 12 This means page size is 4KB. Now process size is 9MB Therefore…

Q: Consider a logical address space of 512 pages with a 4-KB page size, mapped onto a physical memory…

A:

Q: Suppose a processor has access to three levels of memory. Level 1 has an access time of 9…

A: Given: Suppose a processor has access to three levels of memory. Level 1 has an access timeof 9…

Q: Consider a machine where total addressable physical memory size is 32 Kbytes. If we would like to…

A: total addressable physical memory size=32 Kbytes. we like to run 2 processes P and R as 8KB using…

Q: Let us consider a memory that includes two instructions. First instruction is located at memory…

A: CLICK HERE TO GET MORE FREE SOLUTIONS :: Solution :: // C program for the above approach…

Q: Consider a machine where total addressable physical memory size is 32 Kbytes. If we would like to…

A: given, physical mem size=32 p=8KB R=2KB

Q: Let us consider a memory that includes two instructions. First instruction is located at memors…

A: It can be approached as: The instruction consists of opcode and operands. Given the instruction…

Q: Consider a hypothetical memory access time: 1 memory bus clock cycle to send an address

A: Answer: The bandwidth attainable from parallelizing the DRAM initialization time would be 8 words…

Q: Consider a logical address space of 256 pages of 1024 words each. This is mapped onto a physical…

A: Given: logical address space= of 256 pages of 1024 words each. the physical memory=32 frames. We…

Q: Suppose we have a byte-addressable computer using fully associative mapping with 16-bit main memory…

A: The number of bits in the main memory address is given =16 bits In fully associative mapping a…

Q: Consider a logical address space of 32 pages with 1,024 words per page, mapped onto a physical…

A: As mentioned in the question above, addressing is done with 1024 words per page, 1024 = 210 , 1024…

Q: Consider a system with 256Mbytes of main memory with page size of 4Kbytes. It has a logical address…

A: Below is the answer to above questions.

Q: Consider a computer system with a 32-bit logical address and 4-KB page size. The system supports up…

A: A) Number of entries in conventional single level page table = number of pages in virtual address =…

Q: Consider a computer system with a 64-bit logical address and 32-KB page size. The system supports up…

A: 2) Consider a computer system with a 64-bit logical address space and 2-KiB page size. The system…

Q: Suppose a processor has access to three levels of memory. Level 1 has an access time of 9…

A: Level 1 access time = 9 micro seconds Level 2 access time = 23 micro seconds Level 3 access time =…

Q: Consider a processor that uses a 48-bit virtual memory address. The main memory installed on the…

A: virtual memory address=48bits Main memory=4 GB Page Size=32KB Determine the following:I. Address…

Q: Consider a computer with N processors in a multiprocessor configuration. a. How many processes can…

A:

Q: Consider a computer system with a 30-bit logical address and 4-KB page size. The system supports up…

A: 1.

Q: Suppose a byte-addressable memory with 4 frames of size 8 bytes each and a paged virtual memory…

A:

Q: Consider a logical address space of 1024 pages of 2048 words each, mapped onto a physical memory of…

A: Question :-

Step by step

Solved in 2 steps with 2 images

- Suppose a byte-addressable computer using set associative cache has 216 bytes of main memory and a cache of 32 blocks, and each cache block contains 8 bytes. a) If this cache is 2-way set associative, what is the format of a memory address as seen by the cache, that is, what are the sizes of the tag, set, and offset fields? b) If this cache is 4-way set associative, what is the format of a memory address as seen by the cache?Suppose that a machine has 42-bit virtual addresses and 32-bit physical addresses.{a} How much RAM can the machine support (each byte of RAM must be addressable)?{b} What is the largest virtual address space that can be supported for a process?{c} If pages are 2 KB, how many entries must be in a single-level page table?{d} If pages are 2 KB and we have a two-level page table where the first level is indexed by 15-bits, then how many entries does the first-level page table have?{e} With the same setup as part {d}, how many entries are in each second-level page table?{f} What is the advantage of using a two-level page table over single-level page table?Suppose a byte-addressable computer using set associative cache has 4Mbyes of main memory and a cache of 64 blocks, where each cache block contains 8 bytes. a) If this cache is 2-way set associative, what is the format of a memory address as seen by the cache, that is, what are the sizes of the tag, set, and offset fields? b) If this cache is 4-way set associative, what is the format of a memory address as seen by the cache? Show all work and explain how you got the answers please. Thanks

- 1. Consider a computer system with a 30-bit logical address and 4-KB page size. The systemsupports up to 512 MB of physical memory. How many entries are there in each of the following?Assume that each page table entry is 4 Bytes.c. A conventional single-level page table?d. An inverted page table?e. A two-level hierarchical page table? 2. Consider a virtual memory system with a 50-bit logical address and a 38-bit physical address.Suppose that the page/frame size is 16K bytes. Assume that each page table entry is 4 Bytes.a. How many frames are in the systems? How many pages in the virtual address space for aprocess?b. If a single-level page table is deployed, calculate the size of the page table for each process.c. Design a multilevel page table structure for this system to ensure that each page table can fitinto one frame. How many levels do you need? Draw a figure to show your page systemsSuppose a byte-addressable computer using set associative cache has 2^24 bytes of main memory and a cache size of 64K bytes, and each cache block contains 32 bytes. a) If this cache is 2-way set associative, what is the format of a memory address as seen by the cache, that is, what are the sizes of the tag, set, and offset fields? b) If this cache is 4-way set associative, what is the format of a memory address as seen by the cache?Assume a process containing 5 pages with 1024 bytes per page and physical memory with 10 page frames. Frames and pages are of the same size. Given the following page map table (PMT): a) determine the physical address associated with the logical address of page 1, offset 100? b) what is the logical address associated with the physical address 2300? Please dont over complicate this question!!

- Suppose a byte-addressable computer using set-associative cache has 216 bytes of main memory and a cache of 32 blocks, and each cache block contains 8 bytes.Q.) If this cache is 2-way set associative, what is the format of a memory address as seen by the cache; that is, what are the sizes of the tag, set, and offset fields?Consider a memory-management system based on paging. The total size of the physical address space 64 MB, Pages of size 4 KB, the Logical address space of 4GB. total number of pages are 16384, total number of frames are 16384 and the number of entries in a page table are 1048576.Now Calculate: a)Size of Page Table b) No of bits in Physical Address c) No of Bits in Logical AddressSuppose a computer system uses 16-bit addresses for both its virtual and physical addresses. In addition, assume each page (and frame) has size 256 bytes. Could you hand draw the page table, if possible a) Suppose that the OS uses a two-level page table. Draw the page table. (Assume that frames 7 through 221 are free, so you can allocate space for the page table there.) In addition, suppose that the page-table directory storage comprises a whole number of consecutive full frames. (For examples: if the directory entry is 2 bytes, the entry’s storage comprises 1 frame; if the directory entry is 260 bytes, the entry’s storage comprises 2 consecutive frames.) b) What is the size of the two-level page table

- Suppose a byte-addressable computer using set associative cache has 8M byes of main memory and a cache of 128 blocks, where each cache block contains 64 bytes. a) If this cache is 4-way set associative, what is the format of a memory address as seen by the cache, that is, what are the sizes of the tag, set, and offset fields? b) If this cache is 16-way set associative, what is the format of a memory address as seen by the cacheConsider a program that performs the following steps repeatedly: Use the CPU for 4 milliseconds. By issuing an I/O, use the disk for 14 milliseconds. Use the CPU for 10 milliseconds. By issuing an I/O, use network for 18 milliseconds. Assume that each step depends on data obtained from the previous step (e.g., step 3 cannot start before step 2 is completed. Also assume that each resource (CPU or disk or network) can be used by one process at a time. Answer the following questions: (a) Draw 3 time-line diagrams (horizontal axis is the time line; one line for each resource. That is, 3 parallel rows in the resulted figure.) that illustrate the utilizations of the CPU, disk, and network over the execution of two iterations of the program above by a single process. (b) What are the average utilizations of the CPU, disk and network over these two iterations? (Please note that the “total time” should be the same across all resources, from the entire system starts until all work on any…Consider a computer system with a 64-bit logical address and 32-KB page size. Thesystem supports up to 4096 MB of physical memory. How many entries are there ineach of the following?a. A conventional single-level page table?b. An inverted page table?