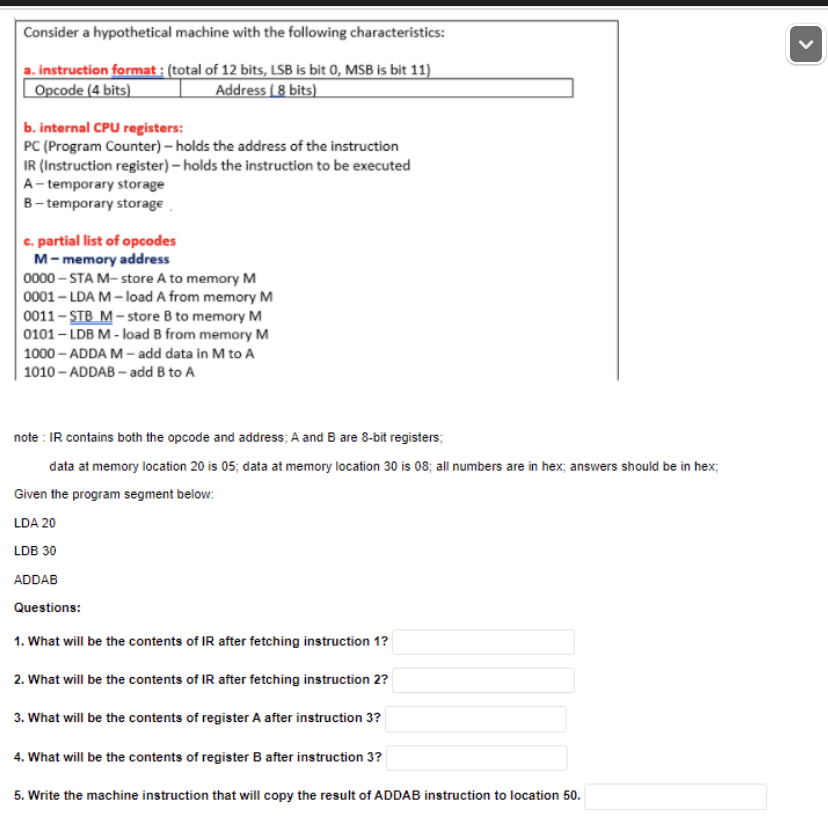

Consider a hypothetical machine with the following characteristics: a. instruction format ; (total of 12 bits, LSB is bit 0, MSB is bit 11) Opcode (4 bits) Address ( 8 bits) b. internal CPU registers: PC (Program Counter) – holds the address of the instruction IR (Instruction register) – holds the instruction to be executed A- temporary storage B- temporary storage. c. partial list of opcodes M- memory address 0000 – STA M- store A to memory M 0001– LDA M- load A from memory M 0011- STB M- store B to memory M 0101 – LDB M - load B from memory M 1000 - ADDA M – add data in M to A 1010 – ADDAB – add B to A note : IR contains both the opcode and address; A and B are 8-bit registers; data at memory location 20 is 05; data at memory location 30 is 08; all numbers are in hex; answers should be in hex; Given the program segment below: LDA 20 LDB 30 ADDAB Questions: 1. What will be the contents of IR after fetching instruction 1? 2. What will be the contents of IR after fetching instruction 2? 3. What will be the contents of register A after instruction 3? 4. What will be the contents of register B after instruction 3? 5. Write the machine instruction that will copy the result of ADDAB instruction to location 50.

Consider a hypothetical machine with the following characteristics: a. instruction format ; (total of 12 bits, LSB is bit 0, MSB is bit 11) Opcode (4 bits) Address ( 8 bits) b. internal CPU registers: PC (Program Counter) – holds the address of the instruction IR (Instruction register) – holds the instruction to be executed A- temporary storage B- temporary storage. c. partial list of opcodes M- memory address 0000 – STA M- store A to memory M 0001– LDA M- load A from memory M 0011- STB M- store B to memory M 0101 – LDB M - load B from memory M 1000 - ADDA M – add data in M to A 1010 – ADDAB – add B to A note : IR contains both the opcode and address; A and B are 8-bit registers; data at memory location 20 is 05; data at memory location 30 is 08; all numbers are in hex; answers should be in hex; Given the program segment below: LDA 20 LDB 30 ADDAB Questions: 1. What will be the contents of IR after fetching instruction 1? 2. What will be the contents of IR after fetching instruction 2? 3. What will be the contents of register A after instruction 3? 4. What will be the contents of register B after instruction 3? 5. Write the machine instruction that will copy the result of ADDAB instruction to location 50.

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 2PE: If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the...

Related questions

Question

Transcribed Image Text:Consider a hypothetical machine with the following characteristics:

a. instruction format : (total of 12 bits, LSB is bit 0, MSB is bit 11)

Opcode (4 bits)

Address ( 8 bits)

b. internal CPU registers:

PC (Program Counter) – holds the address of the instruction

IR (Instruction register) – holds the instruction to be executed

A- temporary storage

B- temporary storage

c. partial list of opcodes

M- memory address

0000 - STA M- store A to memory M

0001– LDA M- load A from memory M

0011- STB M – store B to memory M

0101 – LDB M - load B from memory M

| 1000 – ADDA M- add data in M to A

1010 - ADDAB – add B to A

note : IR contains both the opcode and address; A and B are 8-bit registers;

data at memory location 20 is 05; data at memory location 30 is 08; all numbers are in hex; answers should be in hex;

Given the program segment below:

LDA 20

LDB 30

ADDAB

Questions:

1. What will be the contents of IR after fetching instruction 1?

2. What will be the contents of IR after fetching instruction 2?

3. What will be the contents of register A after instruction 3?

4. What will be the contents of register B after instruction 3?

5. Write the machine instruction that will copy the result of ADDAB instruction to location 50.

>

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning