Identify the memory IC shown to the right: Vce 24 Vss DO 23 D3 Find the contents of each addressable locations D1 22 D2 State the functions of RAS, CAS, WE and OE pins 210 CAS 20 OE 19 A9 WE Show the tentative internal architecture (Schematic diagram) of this IC and identify RAS different functional units NC 18 AS 17 A7 16 A6 15 AS A10 A0 Al 9 A2 A3 11 14 A4 13 Vce 12 Vss Top View

Identify the memory IC shown to the right: Vce 24 Vss DO 23 D3 Find the contents of each addressable locations D1 22 D2 State the functions of RAS, CAS, WE and OE pins 210 CAS 20 OE 19 A9 WE Show the tentative internal architecture (Schematic diagram) of this IC and identify RAS different functional units NC 18 AS 17 A7 16 A6 15 AS A10 A0 Al 9 A2 A3 11 14 A4 13 Vce 12 Vss Top View

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 2PE: If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the...

Related questions

Topic Video

Question

Transcribed Image Text:6.

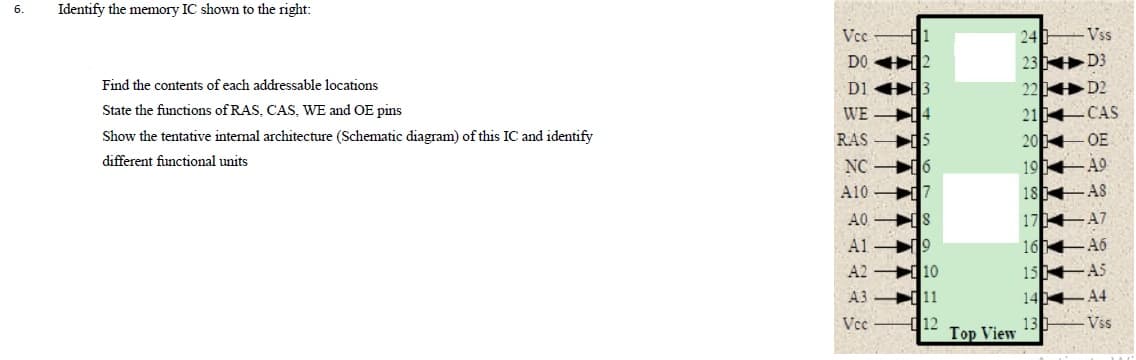

Identify the memory IC shown to the right:

Vcc

24

Vss

23 D3

22 D2

DO 12

D1 3

WE 14

Find the contents of each addressable locations

State the functions of RAS, CAS, WE and OE pins

21 CAS

Show the tentative internal architecture (Schematic diagram) of this IC and identify

20 OE

19 49

18 AS

RAS

i15

different functional units

NC 6

A10 7

17 A7

16 46

15 AS

A0 IS

A1 게9

A2 10

A3 11

14 4

13 Vss

Vce

d12

Top View

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by step

Solved in 2 steps with 2 images

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning