instruction at location 0151 (LXI), it is interrupted. Read the program, then answer the questions that follow: Memory Address Mnemonics START: 0100 LXI SP,0400H 0103 EI 0120 ÇALL 0150H SUB: 0150 PUSH B 0151 LXI B,10FFH 0154 MOV C,A 015E POP B RET 015F a. Specify the contents of stack location 03FFH after the CALL instruction.

instruction at location 0151 (LXI), it is interrupted. Read the program, then answer the questions that follow: Memory Address Mnemonics START: 0100 LXI SP,0400H 0103 EI 0120 ÇALL 0150H SUB: 0150 PUSH B 0151 LXI B,10FFH 0154 MOV C,A 015E POP B RET 015F a. Specify the contents of stack location 03FFH after the CALL instruction.

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 2PE: If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the...

Related questions

Question

100%

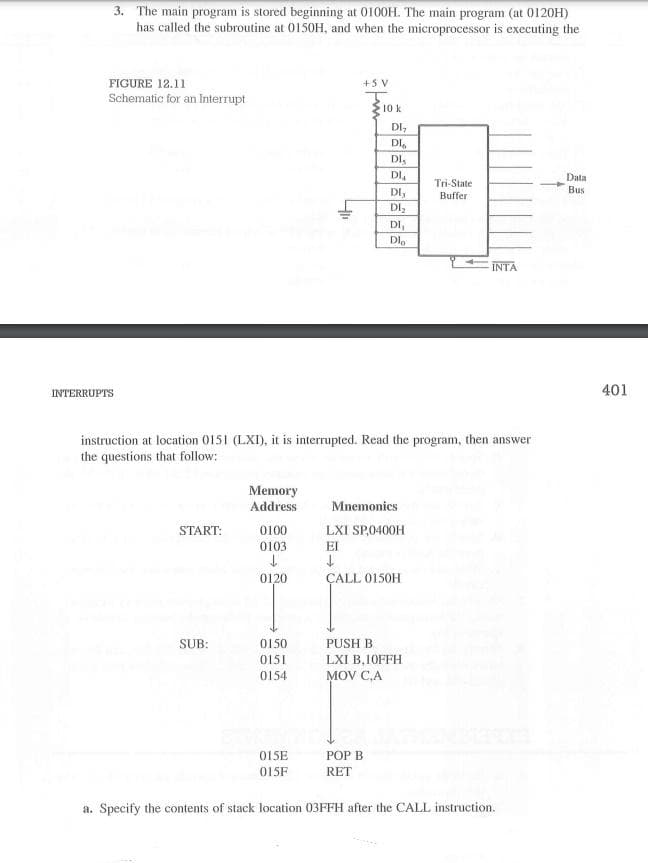

Transcribed Image Text:3. The main program is stored beginning at 0100H. The main program (at 0120H)

has called the subroutine at 0150H, and when the microprocessor is executing the

FIGURE 12.11

+5 V

Schematic for an Interrupt

10 k

DI,

DI,

DI.

DI.

Data

Bus

Tri-State

DI,

Buffer

DIz

DI,

DI,

INTA

INTERRUPTS

401

instruction at location 0151 (LXI), it is interrupted. Read the program, then answer

the questions that follow:

Memory

Address

Mnemonics

START:

0100

LXI SP,0400H

0103

EI

0120

ÇALL 0150H

SUB:

0150

PUSH

0151

LXI B,10FFH

0154

MOV C,A

015E

POP B

015F

RET

a. Specify the contents of stack location 03FFH after the CALL instruction.

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 2 steps

Knowledge Booster

Learn more about

Need a deep-dive on the concept behind this application? Look no further. Learn more about this topic, computer-science and related others by exploring similar questions and additional content below.Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning