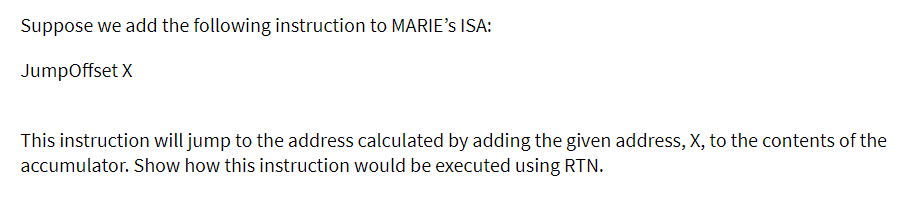

Suppose we add the following instruction to MARIE's ISA: Jumpoffset X This instruction will jump to the address calculated by adding the given address, X, to the contents of the accumulator. Show how this instruction would be executed using RTN.

Q: 243. Fetching an instruction is: a) Bringing the instruction from stack to the microprocessor. )…

A: Q 43. Fetching an instruction is: a) Bringing the instruction from stack to the microprocessor. b)…

Q: Question// calculate physical addressing mode for the following instruction MOVv AX,[BX].ALPHA if…

A: In the above instruction S=0200H, ALPHA=AB54H, and [BX]=900H are given. The data segment register…

Q: Example1: Describe the contents of the address, data and control bus lines when the instruction? MOV…

A: Solution:- Assembly code is as follows; CS = FEDBH ; ZETA = 1234H ; MOV BX, ZETA ; 0AH

Q: Consider the following MARIE Assembly program: label opcode operand hex X LOAD 1107 100 101 SUBT Y…

A: Answer is given below-

Q: The CLC ISA ( a pretend ISA) is under development and in a state of flux. The CLC ISA uses a 40 bit…

A: Maximum number of instructions possible with n bits is given by 2n Hence maximum number of…

Q: What happens if an instruction is not accepted and it writes to VA page 30? In the following…

A: Introduction: When a command is sent to VA page 30: If the instructions want to write to Virtual…

Q: Write an 8086 assembly code (using an 8086emu) that calculates the summation of 11 data bytes (21H,…

A: Algorithm for above program 0.Start 1.Initialise data bytes numbers to contain the given numbers 2.…

Q: Suppose that DS = 1200H, SS = 0100H, and SI = 0250H, Determine the address accessed by the…

A: DS=1200H, SS=0100H and SI=0250H so what will be address accessesd by instruction MOV[SI+100H], EAX…

Q: Suppose we add the following instruction to MARIE’s ISA:This instruction increments the value with…

A: INCZ Instruction: From the description, we can see that the INCZ instruction increments the value at…

Q: Assume that the MIPS instruction j Label is located at address 0x (0800 5678), and that Label is…

A: Given: Assume that the MIPS instruction j Label is located at address 0x (0800 5678), and that…

Q: Suppose that DS = 1200H, SS = 0100H, and SI = 0250H. Determine the address accessed by the…

A: The instruction MOV [SI+100 H], EAX is an indexed addressing mode of instruction. DS is the default…

Q: Given the following branch instruction and location, answer the following questions about it.…

A: Given that: 0X10000 , 0Xb5000184At present, the PC is at 0X10000 * Type of branch Instruction:…

Q: If the current values of registers are as shown below, what are the new values of the registers…

A: Dear Student, PC is the program counter which gets incremented by 1 for each instruction. MAR is the…

Q: If the current values in the code segment register and the instruction pointer are 12AC16 and…

A: ANSWER:-

Q: What is the energy consumption of the worst-case MIPS instruction, and how much energy is required…

A: Intro Below the energy consumed by the worst-case MIPS instruction

Q: Question// calculate physical addressing mode for the following instruction MOV AX,[BX].ALPHA if…

A: GivenMOV AX,[BX].ALPHA we have given S= 0200H, ALPHA=AB54H and [BX]=9000H

Q: 3. If the BIU is already in the process of fetching an instruction when the EU request it to read or…

A: According to the question, we have to choose the correct option according to given criteria. The…

Q: rgy consumed by the worst-case MIPS instruction, and how m

A: Below the energy consumed by the worst-case MIPS instruction

Q: Suppose we have a byte-addressable memory of 20 bytes, built using 4 modules. Draw diagrams showing…

A: Here we had shown the diagram showing the distribution off address within each module, using (a)…

Q: 2. Write an instruction sequence that will initialize the ES register with the immediate value…

A: Q)Write instruction sequences that will initialize the ES register with the immediate value 1020H.…

Q: Suppose we have the instruction Load 1200. Given memory as follows: Memory 1000 1100 1200 800…

A: Please upvote, I am providing you the correct answer below. Please please. 1. Indirect…

Q: Suppose we add the following instruction to MARIE’s ISA: JumpIOffset X This instruction will jump to…

A: Register Transfer Notation (RTN is a notation which uses symbols to describe the behavior of micro…

Q: is the effective address that is targeted by the store instruction whose code word in binary is:…

A: It is defined as programs can be asked from control statements, array, string, oops etc. Java basic…

Q: When does it become possible for a bit to get accessed from bank "0" in the dire addressing mode of…

A: An Addressing Mode is a method to locate a target data where it is also called an Operand. In…

Q: Which functional unit of the ARM architecture is responsible for updating the address register…

A: ARM ( Advanced RISC Machines and initially Acorn RISC Machine) is a group of reduced instruction set…

Q: The branch instruction allows the execution to go backward or forward starting from a new a Opcode…

A: answer is option f f.1000. the branch instruction should be 1000

Q: Suppose that the address of the branch instruction (beq) is 0x2000,0000. Is it possible to use this…

A: yes it is possible. use jr to jump to the address 0x2001,0000. jump instruction uses the current PC…

Q: 8. In fully buffered 8086 microprocessor, its address pins are already buffered by.... b- three…

A: In 8086 microprocessors , its address pins are buffered by 3 latches of 74LS373 , so the only…

Q: Given the following memory addresses and opcodes to be executed, if the current value of the…

A: Please upvote/like .I am providing you the correct answer below. Please. What is…

Q: In the read bus cycle of 8086, the Bus AD0-AD15 is asserts by the MP to end of bus cycle, the…

A: In the read bus cycle of 8086, the Bus AD0-AD15 is asserts by the MP to end of bus cycle, the…

Q: H/W Convert this simple timeline to include all the necessary pins: One Bus Cycle - T T CLK-…

A: In 8086 microprocessor , pins from 16 to 2 i.e,AD0 to AD14 and pin-39 :AD15 ,pin-38:A16/S3,pin-37:…

Q: 6) After the execution the far jump instruction JMP B3000123H, the new value of Physical Address…

A: In the given question we use simple concept of physical address:…

Q: Explain the difference between Preindexed and Postindexed addressing mode with an example. Write an…

A: Pre-indexed The offset is combined with the value in the base register, and the base register is…

Q: The table below shows the 32-bit memory address that is loaded into the program counter (PC)…

A: Answer: Four digit hexa decimal value of the immediate 16 bit field , IMM 16 => Since PC will…

Q: Example1: Describe the contents of the address, data and control bus lines when the instruction? MOV…

A: Given:

Q: The jump instruction () allows the exécution to start from a new address. Opcode (6 bits) Address…

A: Question from jump instruction. jump(X) means we will jump to Address' X' and start execution from…

Q: Compute the physical address for the source operand in the following instruction if the contents of…

A: There are different methods for addressing an operand which is referred as Addressing modes. In the…

Q: Consider the ARM Assembly code: ov a1, v1, ror #8 1. Write a suitable comment for this instruction…

A: register a1 is destination register,register v1 is source register.In this instruction source…

Q: is stored in the memory starting 2- The ISR address of interrupt number at address (0039CH). 3- In…

A: 2) Each interrupt type is given a number between 0 to 255 and the address of each interrupt js found…

Q: is the effective address that is targeted by the store instruction whose code word in binary is:…

A: It is defined as the effective address of an operand is represented in the instruction. Some…

Q: In the JMP instruction, how many bits are there for determining the target address? Select one: O a.…

A: SummaryAnswer: C (22bits) There are numerous different forms of jumps relative, tentative,…

Q: 1) Write a single instruction that will load AX from address 0460H and ES from address 0462H. 2)…

A: Please find your answer below:

Q: If the current value of the PC is OX57F0_3280, can you use a single jump instruction to get to the…

A: Each machine cycle executes one machine instruction. At the top of the machine cycle, the PC…

Q: Write a sequence of instructions to store data from ARM microprocessor’s internal register, R1 into…

A: Mov R0,#0x20000100Msr APSR,R0LDR R0, [APSR]LDR R1,[APSR,#1] LDR R3,[APSR,#1] LDR R4,[APSR,#1] LDR…

Q: Suppose we add the following instruction to MARIE’s ISA: JumpOffset X This instruction will jump to…

A: Register Transfer Notation (RTN) is a notation that uses symbols to define actions. Micro-operation…

Q: 20 LDA 50 21 SUB 51 50 100 51 200 Choose the contents of the registers: PC, MAR, MDR, IR, A at the…

A: Given : Assembly code. The task is to find the value of PC MAR MDR IR A

Q: The program then computes the sum of the three values,

A: Here is the assembly program to compute the sum of theree values:

Q: Q2/ Give an overview of how a byte of data is read from memory address B0003H in a minimum-mode of…

A: It is a 16-bit Microprocessor having 20 address lines and16 data lines that provides up to 1MB…

Q: Suppose the program counter (PC) is set to 0x2000 0000. Is it possible to use the jump (j) MIPS…

A: No, it is not possible to use jump assembly instruction. jump instruction uses j-type format, and…

Trending now

This is a popular solution!

Step by step

Solved in 2 steps with 2 images

- A(n) ________________ instruction always alters the instruction execution sequence. A(n) ______________ instruction alters the instruction execution sequence only if a specified Condition is true.The time it takes to perform the fetch instruction and decode instruction steps is called the execution time. True or false?Suppose we add the following instruction to MARIE’s ISA: JumpOffset X This instruction will jump to the address calculated by adding the given address, X, to the contents of the accumulator. Show how this instruction would be executed using RTN.

- Suppose we add the following instruction to MARIE’s ISA: JumpIOffset X This instruction will jump to the address calculated by going to address X, then adding the value found there to the value in the AC.Show how this instruction would be executed using RTN.Suppose we add the following instruction to MARIE’s ISA:This instruction increments the value with effective address “Operand,” and if this newly incremented value is equal to 0, the program counter is incremented by 1. Basically, we are incrementing the operand, and if this new value is equal to 0, we skip the next instruction. Show how this instruction would be executed using RTN.MIPS ISA has registers of 32-bits which are employed to create a 64-bit base address which is especially used for instructions like Load Word and Store Word. May these Load Word and Store Word instruction formats contain a random pair of source registers to create the base address? If yes, explain if there will be any corresponding effects and what they will be? If no, why not?

- Q1:Suppose the initial physical address of a segment register is given by 0E41:A02EH. Determine the physical address, base and final address of that segment register of 8086 microprocessorin 80886 microprocessor Suppose that. DS = 0200H, BX = 0300H, and DI-400H Determine the memory address accessed by each of the following instructions, assuming real mode operation: (1) MOV AL,[1234H] (2) MOV AX,[BX] (3) MOV [DI]ALAssume that the MIPS instruction j Label is located at address 0x (0800 5678), and that Label is located at address 0x (0800 1234). What will the binary value of the target address field , represented in 26 bits,be?

- If the current values in the code segment register and the instruction pointer are 12AC16 and 88B616, respectively, what physical address is used in the next instruction fetch?In the MIPS micro-architecture, the PC is incremented for each instruction, during the "Instruction Fetch" stage. The value of the PC may also be updated later within the "Memory Access" phase. * If the value of the PC is: 0x0000 2F1C, what is the value of the PC after you complete the execution of the instruction: ``addi $t0, $s0, $ra``?* <!-- response -->The PC ← PC + 1 microoperation is executed at the end of every fetch cycle (to prepare for the next instruction to be fetched). However, if we execute a Jump or a JumpI instruction, the PC overwrites the value in the PC with a new one, thus voiding out the microoperation that incremented the PC. Explain how the microprogram for MARIE might be modified to be more efficient in this regard.