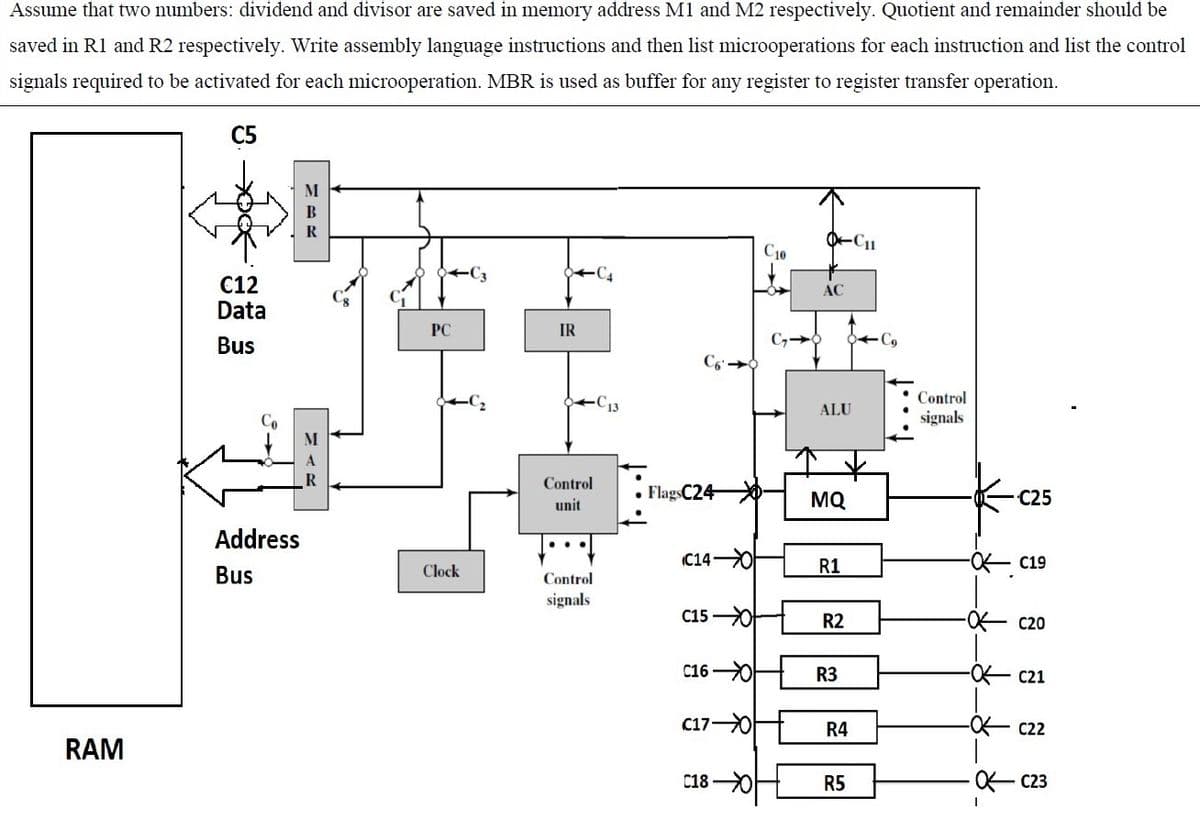

Assume that two numbers: dividend and divisor are saved in memory address M1 and M2 respectively. Quotient and remainder should be saved in R1 and R2 respectively. Write assembly language instructions and then list microoperations for each instruction and list the control signals required to be activated for each microoperation. MBR is used as buffer for any register to register transfer operation.

Assume that two numbers: dividend and divisor are saved in memory address M1 and M2 respectively. Quotient and remainder should be saved in R1 and R2 respectively. Write assembly language instructions and then list microoperations for each instruction and list the control signals required to be activated for each microoperation. MBR is used as buffer for any register to register transfer operation.

Chapter4: Processor Technology And Architecture

Section: Chapter Questions

Problem 2PE: If a microprocessor has a cycle time of 0.5 nanoseconds, what’s the processor clock rate? If the...

Related questions

Question

Transcribed Image Text:Assume that two numbers: dividend and divisor are saved in memory address M1 and M2 respectively. Quotient and remainder should be

saved in R1 and R2 respectively. Write assembly language instructions and then list microoperations for each instruction and list the control

signals required to be activated for each microoperation. MBR is used as buffer for any register to register transfer operation.

C5

C10

C12

Data

АС

PC

IR

Bus

-C9

Control

ALU

signals

A

Control

• FlagsC24 o

MQ

C25

unit

Address

C140

R1

R c19

Bus

Clock

Control

signals

С15 —

OK c20

R2

C16 0

R3

-OK C21

C170

R4

-OK C22

RAM

C18 0

R5

个C23

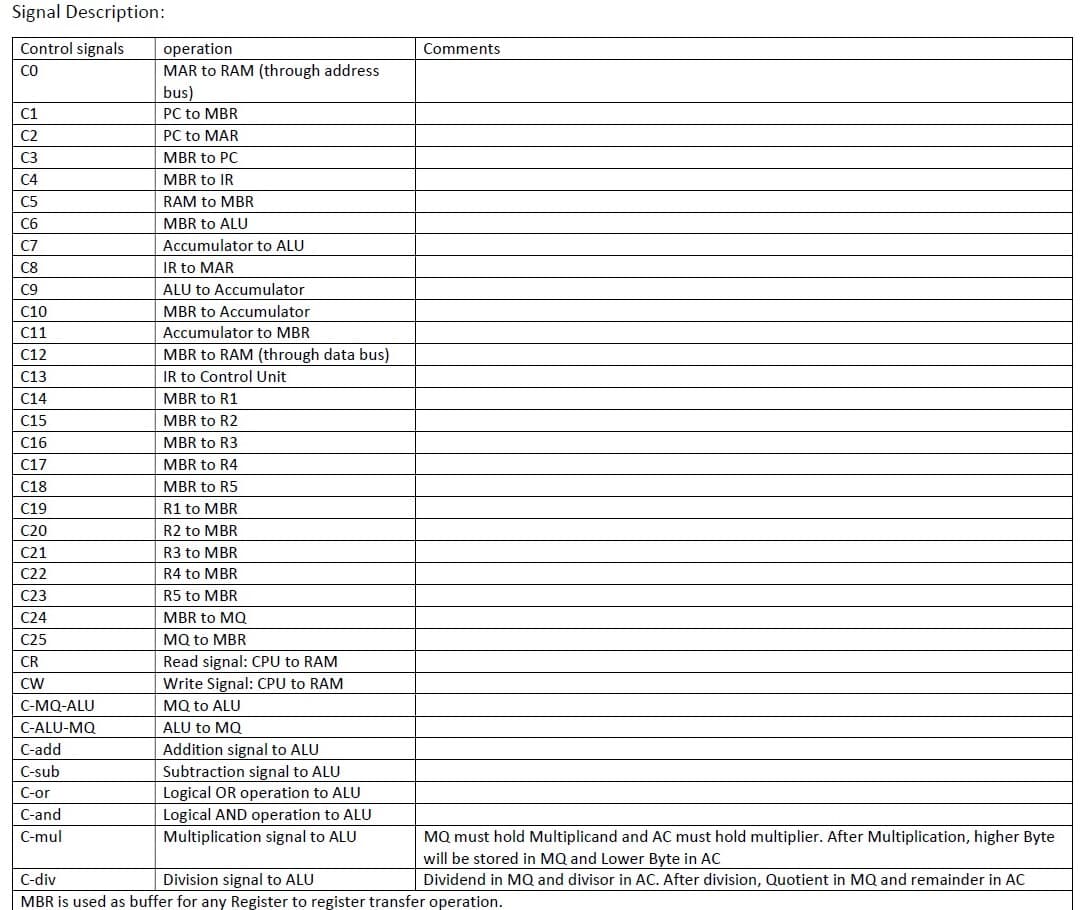

Transcribed Image Text:Signal Description:

Control signals

operation

MAR to RAM (through address

bus)

Comments

CO

C1

PC to MBR

C2

PC to MAR

C3

MBR to PC

C4

MBR to IR

C5

RAM to MBR

C6

MBR to ALU

C7

Accumulator to ALU

C8

IR to MAR

C9

ALU to Accumulator

C10

MBR to Accumulator

C11

Accumulator to MBR

MBR to RAM (through data bus)

IR to Control Unit

C12

C13

C14

MBR to R1

C15

MBR to R2

С16

MBR to R3

С17

MBR to R4

С18

MBR to R5

C19

R1 to MBR

С20

R2 to MBR

C21

R3 to MBR

C22

R4 to MBR

C23

R5 to MBR

C24

MBR to MQ

C25

MQ to MBR

CR

Read signal: CPU to RAM

CW

Write Signal: CPU to RAM

C-MQ-ALU

MQ to ALU

C-ALU-MQ

ALU to MQ

C-add

Addition signal to ALU

C-sub

Subtraction signal to ALU

Logical OR operation to ALU

Logical AND operation to ALU

Multiplication signal to ALU

C-or

C-and

C-mul

MQ must hold Multiplicand and AC must hold multiplier. After Multiplication, higher Byte

will be stored in MQ and Lower Byte in AC

Dividend in MQ and divisor in AC. After division, Quotient in MQ and remainder in AC

C-div

Division signal to ALU

MBR is used as buffer for any Register to register transfer operation.

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

This is a popular solution!

Trending now

This is a popular solution!

Step by step

Solved in 4 steps with 4 images

Recommended textbooks for you

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning

Systems Architecture

Computer Science

ISBN:

9781305080195

Author:

Stephen D. Burd

Publisher:

Cengage Learning