Question

Transcribed Image Text:5.

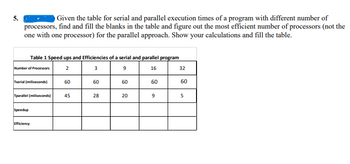

Given the table for serial and parallel execution times of a program with different number of

processors, find and fill the blanks in the table and figure out the most efficient number of processors (not the

one with one processor) for the parallel approach. Show your calculations and fill the table.

Number of Processors

Table 1 Speed ups and Efficiencies of a serial and parallel program

2

3

9

16

Tserial (miliseconds)

Tparallel (miliseconds)

Speedup

Efficiency

60

45

60

28

60

20

60

9

32

60

5

Expert Solution

This question has been solved!

Explore an expertly crafted, step-by-step solution for a thorough understanding of key concepts.

Step by stepSolved in 3 steps

Knowledge Booster

Similar questions

- A generalized register, a single accumulator, or a stack are the three alternative designs for a computer's central processing unit (CPU). Each has its own set of advantages and disadvantages. It is up to you to answer, and your response might be correct or incorrect.arrow_forwardSuppose we have two implementations of the same instruction set architecture. Computer A has a clock cycle time of 210 ps and a CPI of 2.2 for some programs, and computer B has a clock cycle time of 460 ps and a CPI of 1.3 for the same program. Which computer is faster for this program and by how much? Please and thank youarrow_forwardDiscuss the advantages and challenges associated with pipelining in the context of CPU design.arrow_forward

- The result for the SPEC CPU 2017 Integer Speed Result on an Intel Xeon Platinum 8490Hprocessor. This system has an enabled 120 cores, 2 chips and 2 threads/core where each benchmarkprogram is executed simultaneously on all 120 cores with the execution time and ratio for each test asshown on the table. Compute for the speed metric on base and peak.arrow_forwardExplain the concept of instruction-level parallelism and how it relates to pipelining.arrow_forwardPlease compute for the CPU utilization:arrow_forward

- Suppose that we are developing a new version of the AMD Barcelona proces- sor with a 4 GHz clock rate. We have added some additional instructions to the instruction set in such a way that the number of instructions has been reduced by 15% from the values shown for each benchmark in Exercise 1.12. The execution times obtained are shown in the following table. a. Name Execution Time (seconds) Reference Time (seconds) bzip2 700 9650 SPECratio 13.7 1.13.2 [10] In general, these CPI values are larger than those obtained in previous exercises for the same benchmarks. This is due mainly to the clock rate used in both cases, 3 GHz and 4 GHz. Determine whether the increase in the CPI is similar to that of the clock rate. If they are dissimilar, why?arrow_forwardDescribe the challenges introduced by "pipeline flushing" and its impact on CPU performance.arrow_forward

arrow_back_ios

arrow_forward_ios